FPGA宇航应用全流程保证技术

2017-03-08朱恒静

张 莹,朱恒静,苏 妤

(中国航天宇航元器件工程中心,北京 100094)

FPGA宇航应用全流程保证技术

张 莹,朱恒静,苏 妤

(中国航天宇航元器件工程中心,北京 100094)

文章分析了 FPGA的结构特点,结合宇航型号研制流程和国内近年来元器件保证技术的研究和工程实践,提出了 FPGA宇航应用保证流程和保证的内容,针对其中的器件测试、封装工艺鉴定、开发验证和确认、单粒子效应减缓措施等关键技术进行了深入研究。文章提出的相关技术可以作为 FPGA宇航应用评价和保证的参考。

FPGA;宇航应用;元器件保证

0 引言

随着宇航型号研制技术的不断发展,用户技术指标的不断提高,功能集成和微小型化已经成为星载电子设备的主流趋势。采用大容量、高密度、高性能的FPGA,能够使星载电子设备体积减小、重量减轻、功耗降低,缩小电路板的尺寸,减少焊盘数量,提高航天器承载有效载荷的能力及功效比,还能充分利用冗余技术提高系统的容错能力,需求不断增加。

虽然 FPGA在航天型号中的推广使用呈逐年上升的趋势,但FPGA的设计和结构特点使其在宇航领域应用需要进行一系列的评估和验证工作。NASA每年均会针对有选用需求的新型FPGA制定评估计划并实施,如针对新工艺的宇航鉴定[1-2]、新型封装的可靠性评估[3]、抗辐射能力评估[4]等。ESA要求在决定飞行设备使用FPGA前,应进行全面、系统的风险和可行性评估,并通过多年的研究和实践工作,形成了FPGA应用相关的指南[5-6]。国内对宇航用FPGA保证的研究也逐步深入,除传统的器件级筛选试验外,开展了FPGA应用验证和应用保证的研究。

本文研究建立了覆盖 FPGA的宇航应用全流程的保证方法,然后对流程中的器件测试表征、封装工艺鉴定、开发验证和确认、单粒子效应减缓措施等方面进行了深入分析。

1 FPGA宇航应用概况

根据编程特性,目前 FPGA的主要类型有SRAM型、Flash型和反熔丝型,就其在航天领域的应用而言,每类技术都有各自的优缺点。由于SRAM可以方便地进行重复擦写,基于SRAM技术的FPGA得到了广泛应用,但其最大的缺点是容易发生单粒子翻转,且通常需要使用外部非易失性存储器来存储相关的配置信息,上电加载过程中容易产生错误指令。Flash型FPGA结合了非易失性和可重复编程的特点,上电后无须配置时间,静态功耗低,但其擦写寿命有限,抗单粒子翻转能力较PROM差,难以防护,空间应用具有一定风险。反熔丝型FPGA具有信息安全性高、抗辐射性能优越的特点,但无法重复编程,规模和密度也远低于采用SRAM可编程技术的FPGA。

FPGA通常用于航天器的关键分系统和单机,由于其结构和功能的特殊性,传统的集成电路保证方法不完全适用于 FPGA的性能验证和可靠性评估,如对FPGA的设计和工艺的鉴定、对器件特性验证的特殊要求以及针对应用中薄弱环节的保证,均是在传统保证方法基础上针对 FPGA器件特性提出的特殊保证要求。

2 FPGA宇航应用全流程保证

FPGA保证应在分析FPGA设计、工艺特点的基础上开展,一般包括评估、工艺鉴定、应用验证,以及装机产品保证和应用保证。具体保证内容可视FPGA研制和应用的成熟度确定。

对于新研制FPGA的保证,可以考虑与FPGA研制、型号应用同步开展。保证流程是一种与器件研制流程、宇航型号研制流程有切入、反馈关系的关联结构。FPGA保证不是一项孤立的工作,相关流程也需要保证工作的反馈结果对其是否进行下一步工作提供参考依据。

开展FPGA保证工作前,应首先对型号需求和器件现状进行分析,确定FPGA保证各阶段的具体工作项目。对需要开展的工作项目之间的关联关系进行分析,确定各项目之间的关联结构,建立覆盖FPGA宇航应用全流程的保证方法。

2.1 FPGA评估

FPGA评估包括生产厂评估、设计评估、结构分析和极限评估。

1)生产厂评估。包括:分析产品的研制流程;分析FPGA的生产流程,以及生产流程中每项试验的依据说明、试验程序和方法;分析生产线状态,检查该生产线是否具备持续生产能力,生产线质量是否稳定;分析生产厂是否具备持续供货的能力;分析生产厂质量保证能力,包括生产厂质量保证计划、开展的质量保证工作、生产厂进行可靠性试验的条件和试验数据等方面的内容。

2)设计评估。包括结构设计评估、前端逻辑评估和后端版图评估,重点分析设计流程、IP核、设计过程的验证和确认、可靠性设计的手段、采用的抗辐射设计手段、失效模式。

3)结构分析。包括器件封装设计和结构分析评价、芯片设计和结构分析、器件热分布分析、主要结构的工艺可靠性分析、材料分析、应用于空间环境的设计结构可靠性分析等。

4)极限评估。根据FPGA器件特性和应用环境应力不同,选择合适的试验项目(温度应力、电应力、机械应力和综合应力试验)和试验方式(恒定应力试验方式和步进应力试验方式)。

2.2 工艺鉴定

针对FPGA工艺的鉴定,是指在掌握FPGA生产工艺、失效机理的基础上,基于失效机制建立设计准则,以及激活能与特定失效机制之间的关联关系。FPGA工艺鉴定的内容包括晶片生产工艺鉴定、封装工艺鉴定和器件特性表征。

FPGA生产工艺包含了热载流子效应、与时间相关的介质击穿、电迁移和负偏压温度不稳定性等几种基本的物理退化机制,鉴定应针对上述失效机制进行。应针对生产工艺进行长期可靠性试验,以及失效率验证试验;通过多个生产批次、不同批次的重复性及成品率(应具有多个晶圆的统计数据),分析工艺的成熟性。

FPGA封装工艺鉴定可依据GJB 7400[7]附录B进行,采用非气密陶瓷封装工艺的器件鉴定可依据MIL- PRF-38535K[8]进行。

FPGA器件特性表征需要定制测试向量实现对FPGA的特性或功能验证。在FPGA研发、制造和验证的整个流程中,有许多测试点,可以在晶圆制造阶段采用设计专用测试点的方式,或封装之后对器件进行测试,通过三温测试获取器件电性能参数和基本功能时序参数,并使用特别设计的测试向量和条件进行器件逻辑仿真。

2.3 应用验证

FPGA应用验证应覆盖其功能和性能、可靠性、应用适应性3个方面:

1)功能和性能。包括功能、规范规定的参数、极限参数等。

2)可靠性。包括设计可靠性、结构可靠性、工艺可靠性、禁限用材料、可靠性试验等。

3)应用适应性。包括空间环境适应性、力学环境适应性、热学环境适应性、系统适应性、装联工艺适应性等。

具体验证项目如表1所示。

2.4 装机产品保证

FPGA装机产品保证包括采购规范编制、监制、验收、补充筛选、DPA及使用控制等工作项目。由于FPGA结构和功能的复杂性,在产品验收中需要重点关注筛选过程的老炼试验、测试等项目的实施结果。

2.5 FPGA应用保证

FPGA应用保证包括对单粒子效应的系统加固措施和对FPGA设计开发的验证。

FPGA宇航应用应关注单粒子效应,通过地面评估试验获得器件抗单粒子能力,有针对性地采取系统级加固措施,如三模冗余、定时刷新或备份措施等,并对加固结果进行评估。

对 FPGA设计开发的验证应重点关注系统级需求、FPGA开发的功能性能规范的验证,以及软件代码的验证,可通过测试和仿真手段实施。

3 FPGA宇航应用保证关键技术

3.1 FPGA器件测试表征

FPGA器件测试与传统集成电路不同,每个实现具体功能的FPGA都可视为一个定制集成电路,需要定制测试向量。测试可用于晶圆制造阶段或封装之后对器件进行测试,也可以用于筛选试验,如老炼试验。FPGA的测试需要对FPGA进行编程,使FPGA实现某种特定功能。测试的关键点包括多种内嵌资源的测试、可编程互联资源测试、系统整体测试、功耗测试和内部延时测试。完整的FPGA测试应按照器件内部结构将其划分为多个独立的模块,按照不同模块的功能进行特定的测试向量设计,如针对SRAM型FPGA,可编程互联资源的测试应包括对内部DCM、BRAM、CLB、IOB、IOL等所有可提供的用户可编程资源测试,配置功能测试应通过配置控制模块对 FPGA内部进行特定的数据写入和回读,覆盖所有的配置数据存储单元。

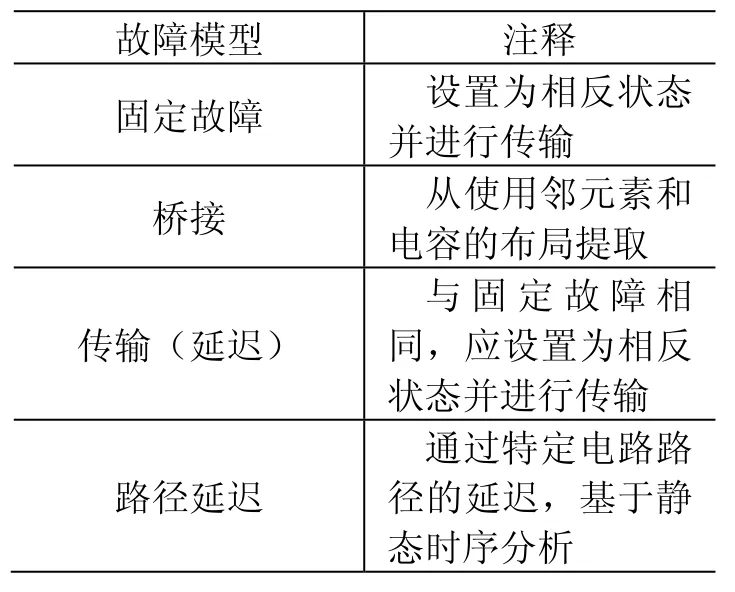

测试向量与器件退化的对应基于故障模型的分析和建立。开发结构化测试向量时,模型基于Verilog开发,应用于门级电路。这些模型通常被设计成易于计算的而不是“故障精确”的,使得与模型对应的测试向量会遗漏芯片上呈正态分布的缺陷。造成这种现象的原因之一是应用侧重于门互连,输出主线和支线常常被分离对待。FPGA主要的逻辑故障见表2。

表2 FPGA主要的逻辑故障模型Table 2 Main logic fault model of FPGA

除了数字逻辑,现代FPGA还使用大量存储单元,结构的唯一性向测试存储单元提出一系列问题。除了固定故障等通用故障模型,其他故障模型还有耦合故障、干扰故障和滞留故障,存储单元的测试通常基于算法而不是故障模型。

电测试与器件现象映射关系的建立仍然是一个主要研究领域。构建的测试向量应能映射引起可靠性降低的潜在物理机制。被测设计和器件级待测参量的测试向量之间的关系十分复杂。具体测试电路的设计在FPGA验证中的作用已经越来越重要。图1说明了潜在器件退化现象与FPGA测试向量之间的逻辑映射。

3.2 FPGA封装工艺鉴定

随着FPGA规模的不断增加,芯片尺寸相应增大,器件封装越来越复杂,倒装结构的封装方式是多管脚复杂大规模集成电路常用的封装方式,如Xilinx公司Virtex系列第4代之后的FPGA采用了非密封封装形式。倒装芯片焊盘通过凸点与基板连接,用环氧树脂来填充缝隙,以保护凸点;芯片背面黏接到散热板上;采用高密度柱栅阵列作为封装引脚,另外,在封装外部陶瓷基板上黏接片式电容达到去耦作用。

在宇航应用的极端温度环境和真空环境条件下,非密封封装可能带来的可靠性风险包括:环境交变导致的应力对封装材料的影响;水汽对有机材料和芯片的影响;真空环境对有机材料的影响等。这种封装工艺涉及倒装焊、填充物、黏接材料、柱栅等方面,其鉴定涉及的应力包括温度循环、温湿度应力、机械应力。封装工艺特性表征和鉴定可参照MIL-PRF-38535K及GJB 7400的规定。

3.3 FPGA单粒子效应减缓措施

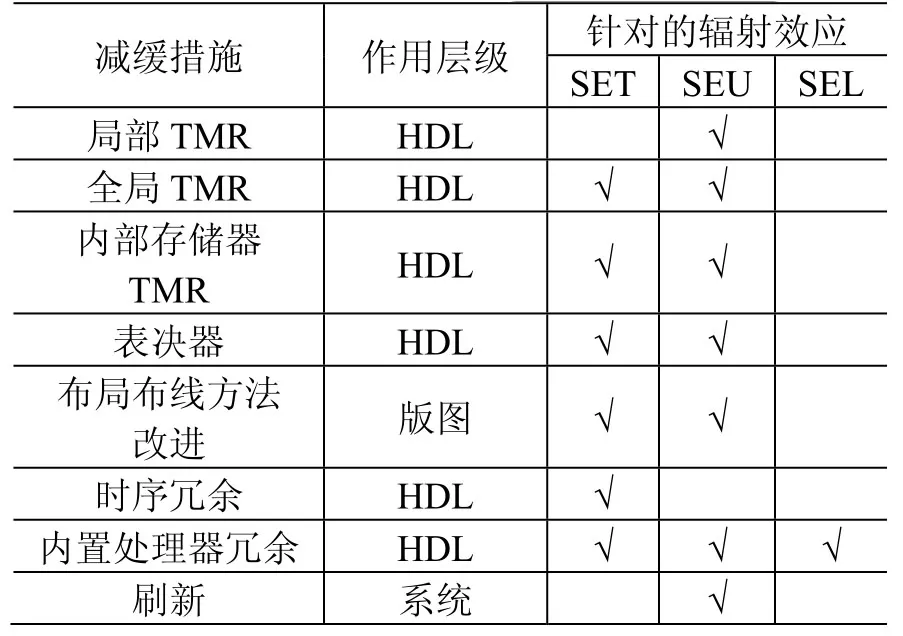

针对FPGA的单粒子效应,应从设计加固、工艺选择和加固、应用加固3方面予以减缓。在设计加固方面,可以采用抗辐射加固结构设计,优化内部关键路径设计,减少数据和控制线的抖动引起的误触发或者数据锁存错误。在工艺选择和加固方面,可以选择外延层工艺、SOI/SOS工艺,埋层和三势阱是工艺加固的有效措施,见表3。在应用加固方面,可以采用冗余、刷新、重启等措施缓解单粒子效应导致的风险,根据应用需求选择局部或全局冗余技术,并配合配置存储器的定时刷新,可以大大降低FPGA发生单粒子错误的概率,见表4。

表3 FPGA工艺选择和加固策略Table 3 Technology selection for dealing with FPGA radiation effects

表4 主要的FPGA应用加固措施Table 4 Main SEE mitigation technique

三模冗余(TMR)技术非常适用于FPGA,因为它提供了包括用户组合和时序逻辑、布线资源及I/O端口在内的全面硬件冗余,但其最突出的问题就是设计占用面积和功耗的开销较大。TMR技术最大的特点就是对1个逻辑电路复制3份,对其结果进行表决输出,通常情况下取多数结果作为最后的输出结果。配置存储器的刷新:利用FPGA在配置完成后支持用户对配置数据进行回读的特性,将配置帧数据回读,与配置存储器中的原始数据进行比较,如发现存在错误的比特流位,则对其进行修改后重新配置到 FPGA中。TMR技术的实现在ASIC中与在FPGA上存在很多不同,在ASIC中,仅局限于保护用户设计中的触发器结构,而不需要考虑对逻辑路径的保护,这是由于在集成电路中,触发器与触发器之间的路径都是固化的,属于硬连接,而不同于FPGA中可编程的互连结构。对于特定的逻辑结构,TMR技术足以抵御SEU效应,但是不能抵御 SET效应,更深层次的保护可以通过全模块冗余来实现。全局TMR是基于FPGA结构的特殊性而提出来的,因为所有的逻辑路径,不仅仅是触发器,都会受到SEU的影响。这就意味着将在FPGA中实现3个相同的设计模块来减缓单粒子翻转效应和单粒子瞬时效应。

3.4 FPGA开发验证和确认

FPGA常作为控制或数据处理的关键器件用于航天器的中央处理单元、数传分系统等。在航天器方案设计阶段,针对航天器的总体要求将被逐级分解为对分系统、单机级的需求和对FPGA的功能需求,形成FPGA的软件设计规范,宇航应用需求分析与FPGA器件研制实现的接口关系如图2所示。

FPGA的设计通过HDL代码实现,而对设计的验证和确认是FPGA宇航应用的必要条件,以保证其能够满足航天器的系统级需求,特别是使用FPGA的关键分系统的需求。验证和确认工作应由独立于用户及FPGA生产厂的第三方进行。

FPGA的典型开发流程包括需求阶段、设计阶段和实现阶段。

1)需求阶段

FPGA需求阶段的验证和确认分析从器件设计规范开始,设计规范是实现层面的需求。在航天器系统级需求和性能的基础上形成 FPGA功能级和实现级需求,所有这些需求一起构成了设计的详细要求。

FPGA需求阶段验证和确认的主要输出是FPGA需求规格说明,通过建立有效的需求评估检查单,跟踪规范直到详细的功能设计,并验证软件设计规范的正确性以及接口设计的完整性。在需求阶段,验证和确认还需要编制系统测试计划和验收测试计划。

2)设计阶段

功能设计阶段[9]验证和确认将需求分析翻译成诸如顶层框图、寄存器表、时序图等形式的设计描述,并将这些设计产物与HDL定义的寄存器转移级代码形式的实际实现进行比较。

概要设计阶段主要的验证和确认是通过审查、评估、仿真的方法对设计文档进行验证。包括FPGA外围部件(如电压源、时钟晶振、存储器或微处理器等)的设计描述,应对FPGA设计原理图、状态图和时序图进行全面验证。

RTL设计阶段主要的验证和确认是对RTL代码清单进行静态检查和动态仿真测试,静态检查并不运行代码本身,仅对代码设计说明、代码结构、流程图进行分析;动态仿真测试需要运行代码,对代码的正确性、可测性、易读性,以及接口协议正确性进行全面验证。

3)实现阶段

FPGA开发的实现阶段始于详细设计,详细设计是功能设计的HDL代码实现,以及代码综合以产生表示FPGA虚拟结构的网表。HDL代码通常从IP库代码复用开始,利用软件开发工具综合代码后,设计师可以运行仿真进行验证和确认,或者进行到下一步并执行布局布线以编程物理器件。

4 结束语

FPGA的保证应贯穿器件设计、生产、质量保证和应用的全过程,应在传统质量保证的基础上,进一步提出对FPGA评估、工艺鉴定、应用验证和应用保证要求。通过分析FPGA设计、工艺特点和失效机理,在器件保证各个阶段有针对性地采取评价、验证和应用加固措施,以保证FPGA宇航应用的可靠性。

本文提出了 FPGA宇航应用全流程保证的概念和各阶段的基本保证项目,识别了其中的关键保证项目并研究了保证的理论方法,可以作为新型FPGA或国产化研制FPGA宇航应用进行评价和保证的参考。但由于FPGA器件的故障模型尚未被完全识别,且其可靠性与应用关联紧密,仍应进一步深入开展研究工作,以及测试验证、应用验证的工程实践,并充分将器件保证与应用相结合。

(References)

[1]DOUGLAS S.FPGA NEPP FY10 summary report: JPL Publication 10-8 9/2010[R]

[2]DOUGLAS S.FPGA NEPP FY09 summary report: JPL Publication 10-1 1/2010[R]

[3]DILLON R P.XILINX V4 package reliability: properties and reliability of underfill material: JPL Publication 12-6 3/2012[R]

[4]ALLEN G.Single-event effect(SEE) survey of advanced reconfigurable field programmable gate arrays: JPL Publication 11-18 12/2011[R]

[5]ESA.Trends and patterns of ASIC and FPGA use in European space missions[DB/CD].[2013-04-15].http://Amstel.estec.esa.int

[6]Techniques for radiation effects mitigation in ASICs and FPGAs: ESCC-Q-HB-60-02A[S].ESA-ESTEC

[7]合格制造厂认证用半导体集成电路通用规范: GJB 7400—2011[S].北京: 总装备部军标出版发行部

[8]Performance specification: integrated circuits (Microcircuits) manufacturing, general specification for: MIL-PRF-38535H[S]

[9]刘瑞, 李朝历, 李艳丽, 等.基于FPGA的核电厂安全级仪控系统验证与确认[J].核电子学与探测技术, 2014, 34(1): 103-106 LIU R, LI C L, LI Y L, et al.V & V for FPGA-based instrumentation and control systems of nuclear power plants[J].Nuclear Electronics & Detection Technology, 2014, 34(1): 103-106

(编辑:王 洋)

FPGA aerospace application assurance technology

ZHANG Ying, ZHU Hengjing, SU Yu

(China Aerospace Components Engineering Center, Beijing 100094, China)

This paper analyzes the construction feature of the FPGA, then proposes an aerospace application assurance process according to the spacecraft development process, based on the theories and practices of the components assurance.The assurance content of different stages is defined, as well as the details for the performance testing, the package technology evaluation and the design verification and validation.It may serve to guide the evaluation and the assurance of the FPGA aerospace application.

FPGA; aerospace application; component assurance

V439+.4

:A

:1673-1379(2017)01-0109-06

10.3969/j.issn.1673-1379.2017.01.018

张 莹(1983—),女,硕士学位,从事型号元器件保证工作。E-mail: mindun_1983@163.com。

2016-07-29;

:2017-02-04

张莹,朱恒静,苏妤.FPGA宇航应用全流程保证技术[J].航天器环境工程, 2017, 34(1): 109-114

ZHANG Y, ZHU H J, SU Y.FPGA aerospace application assurance technology[J].Spacecraft Environment Engineering, 2017, 34(1): 109-114