基于DSP和CPLD的工业用三相电压监测系统设计

2017-03-07李静,刘牮,李彧

李 静,刘 牮,李 彧

(上海理工大学 光电信息与计算机工程学院,上海 200093)

基于DSP和CPLD的工业用三相电压监测系统设计

李 静,刘 牮,李 彧

(上海理工大学 光电信息与计算机工程学院,上海 200093)

现代工业用电环境由于负载的多变性而存在过多干扰噪声。传统的电压监控系统监控手段单一,频率检测多采用硬件检测导致检测精度误差较大。针对此现象设计了一种基于DSP和CPLD架构软硬件结合的工业用三相电压检测系统,并以高精度电流型电压互感器作为采样元件,利用线性拟合法计算电压有效值及使用FFT-Rife算法计算频率,并使用LCD作为人机交互界面。经过测试该系统能实现高精度测量要求,且体积小、方便现场调试与安装,具有一定的实用价值。

DSP;CPLD;FFT-Rife算法;线性拟合

工业设备的稳定工作直接依赖于稳定的电压,实时电压监控应运而生。早先的监控模式为纯硬件电路检测,依靠电阻采样、比较器等模拟器件测量电压的有效值以及频率,常受限于器件的响应速度、环境噪声、温度及采样的精度,导致测量结果的不准确,尤其当电网中存在谐波干扰的情况下导致测量出现更大的偏差[1]。为了提高检测精度以及避免过多使用模拟器件的情况下,设计了一种基于DSP的小型高精度工业电压检测系统,测量功能全部以软件实现,同时带有显示界面,显示测量的有效值与频率。

1 电路结构

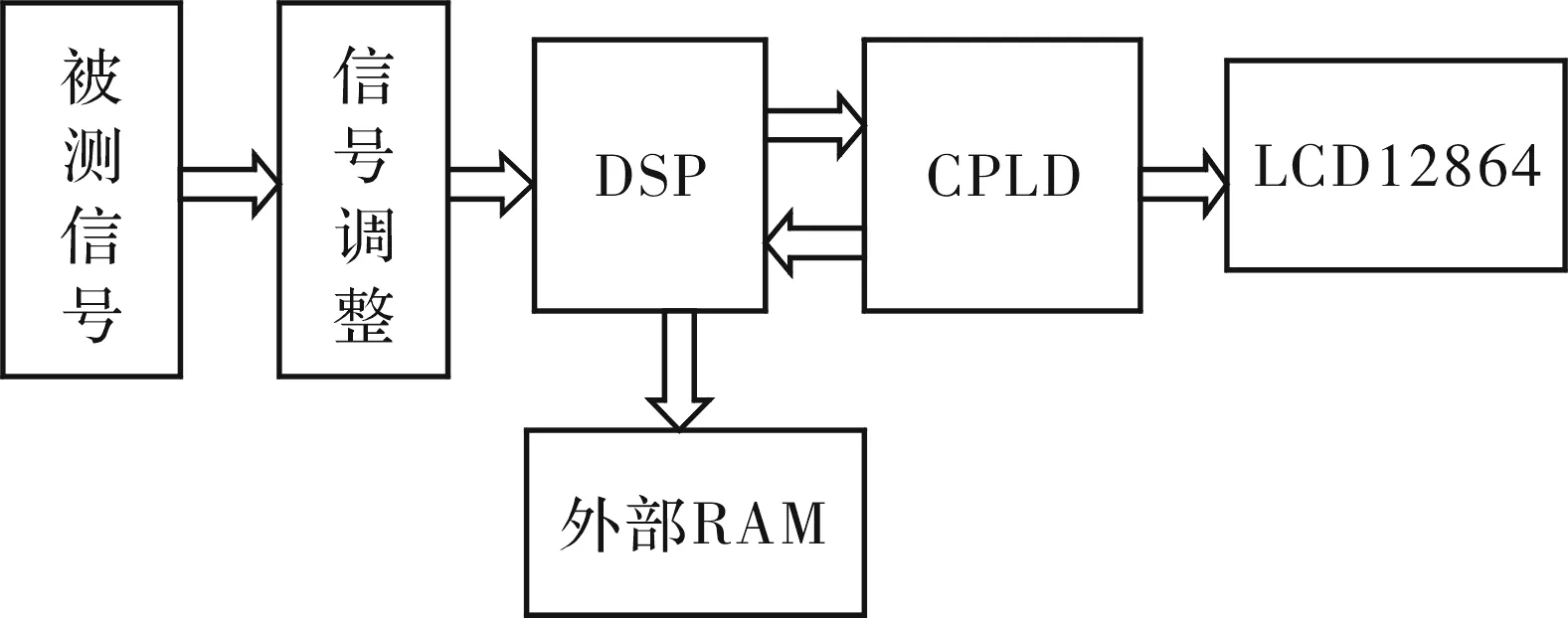

根据频率及有效值的计算量大的特点选用TMS320F28335为主芯片。使用高精度电流型互感器TV18采样,并通过外扩RAM增大DSP的存储空间。电源部分使用TI的DSP专用电源芯片产生所需的3.3 V以及1.9 V,电压有效值测量采用二元线性拟合算法,频率部分采用FFT配合修正后的Rife[2]算法来测量,每一次检测完毕后将检测结果送至LCD显示,整体电路组成如图1所示。

图1 整体电路结构图

1.1 电路电源

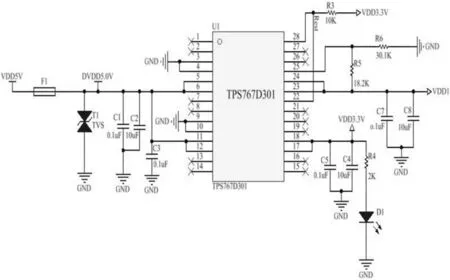

DSP内核电源需要1.9 V,另外需要针对I/O口电平需要设计专门的电压3.3 V电压,目前市面上使用最多的线性稳压电源是类似于78XX系列的的5 V或12 V电源,不能通过简单的分压产生稳定的电源电压,如果通过电阻分压产生3.3 V以及1.9 V的电压,在带载的情况下很容易因为负载电流不稳定导致分压电阻上的电压发生变化,严重时甚至影响DSP内核工作[3]。TI针对DSP提供了一种专用电源芯片TPS767D301,该芯片为两路低压差输出电压(其中有一路可调节),产生3.3 V与1.9 V电压输出,电源整体电路如图2所示。

图2 电源电路

1.2 信号采样与存储电路

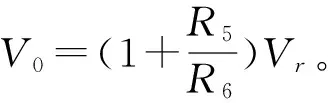

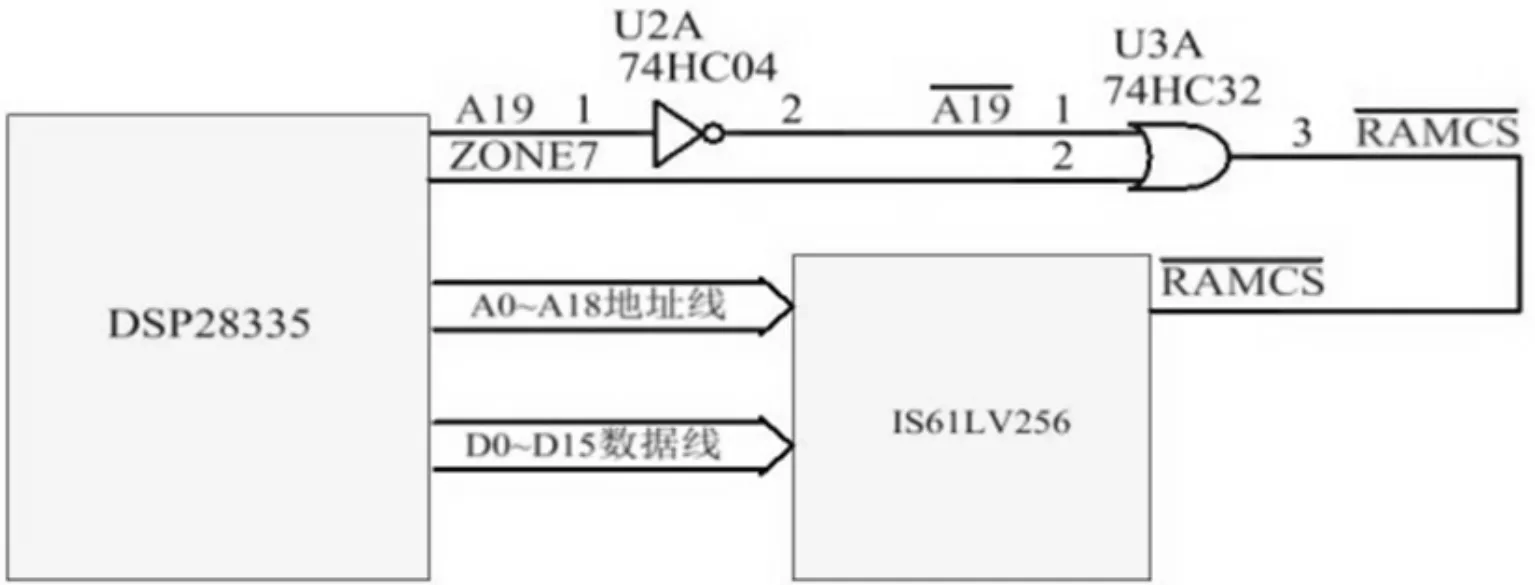

信号经过采样电路调理后输入DSP的AD端口,采样部分电路使用一级跟随电路, TV18原边电流与副边电流呈1:1比例,通过电阻限流将外部转换为1 mA电流叠加至传感器输入端,输出端连接采样电阻4 kΩ,连接运放后接至DSP的A/D端[4]。由于使用FFT算法,数据量较大,考虑使用外部存储器。在DSP外部扩展一片存储容量为256 kB的RAM芯片。外接RAM时首先选择扩展至DSP片外接口的哪个区域,DSP拥有3个外部接口区,ZONE0、ZONE6、ZONE7,ZONE6和ZONE7都有1M宽×16位的存储空间,在此选择ZONE7为外部RAM扩展区域。DSP在读取外部存储器空间时首先跳转至外部指定的地址空间,由于只在外部扩展256 kB片外RAM,所以应设计逻辑电路将片外RAM地址空间映射在ZONE6区域[5],再将CMD文件中ZONE6区域的范围修改为指定地址空间即可。

图3 采样电路

图3中T3,T4和T5为TV18,运放输出电压跟随互感器的输出电压并起到缓冲作用,运放输出端接有电压钳位电路确保输入到DSP的A/D端口信号不高于3.3 V。DSP外扩RAM需要经过逻辑电路的逻辑判断才能读取指定位置的数据,ZONE7的地址范围是0x200000~0x300000,逻辑判断电路如图4所示。

图4 扩展RAM示意电路

当DSP读取ZONE7处的数据时将自动拉低ZONE7片选信号线,由于片外RAM只具有18位寻址范围,所以将DSP的地址线A19也作为片外RAM的片选信号,只有A19输出也为低电平时,与ZONE7同时为低电平,经过74HC32相或后输出RAMCS片选低有效信号启动外部RAM,DSP的A0~A18地址线、D0~D15数据线和片外RAM相连,当DSP读取0x280000处以后的数据时启动片外RAM[6]。同时需要对CMD文件中的ZONE7区域指定专门的存储范围。

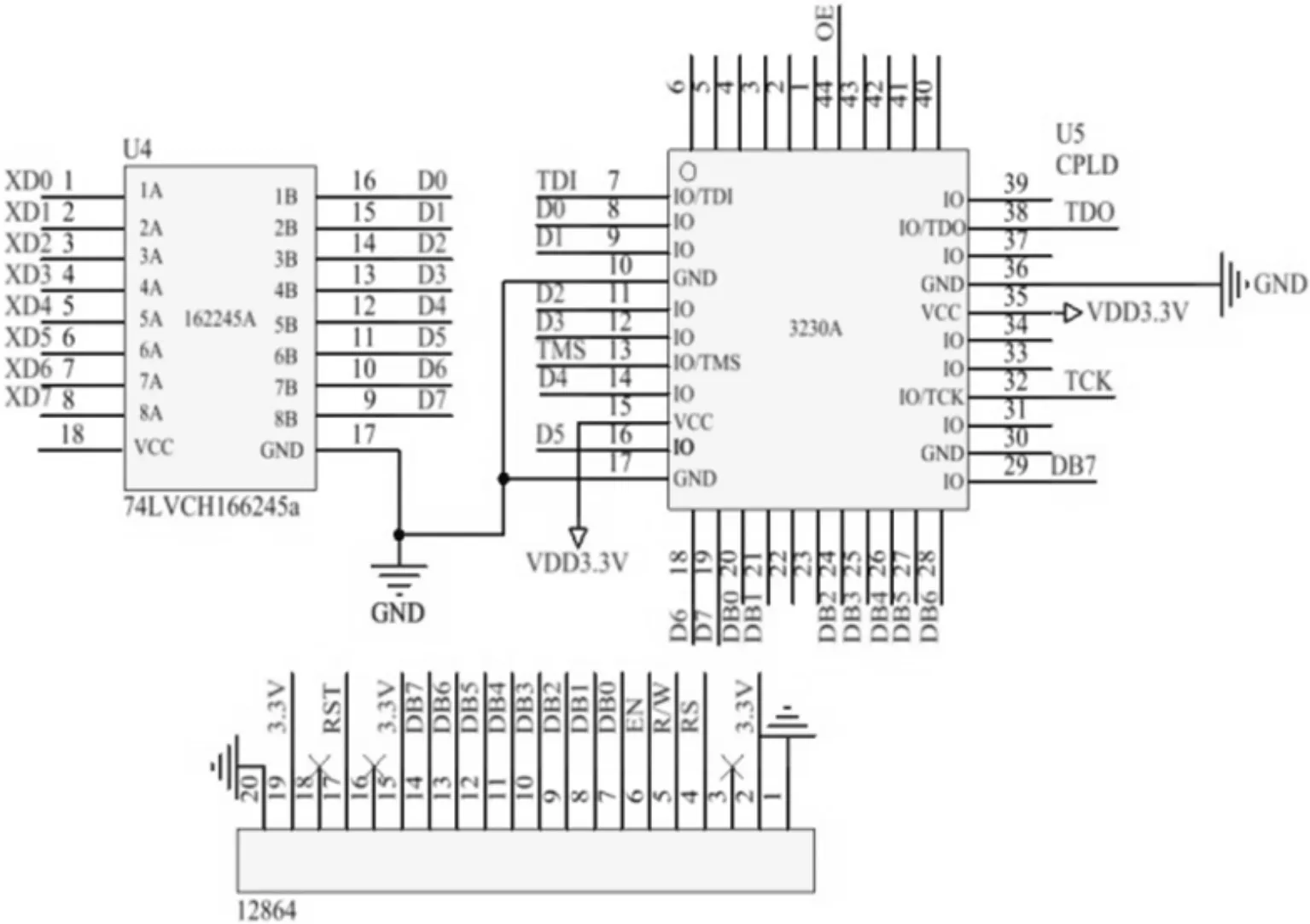

1.3 CPLD以及液晶模块

DSP工作在150 MHz主频下,这就要求与DSP外围对接的器件满足快速电平变化的要求,由于LCD12864属于低速设备,且LCD工作时要求时序严格,包括LCD的初始化,读取以及写内部存储空间数据,绘图等均要求有严格的时序逻辑,若直接将LCD与DSP相连可能会导致LCD无法与DSP速度匹配,导致显示故障[7]。所以针对高速设备与低速设备直接接口电路的特点选用3128ACPLD进行接口逻辑判断及时序控制,CPLD能将DSP输出的各个IO口时序统一,确保总线上的数据同一时间发出,使LCD接受数据的时序同步,避免显示错误,电路图如图5所示。

图5 总线隔离与CPLD电路

使用一片总线隔离芯片74LVCH166245输入端1~8 A与DSP的数据总线D0~D8相连,输出端经过隔离后与CPLD的IO口相连。CPLD的使能端受DSP控制,将CPLD的IO口约束后使得D0~D7和DB0~DB7连通,仅起到连通作用,再与LCD连接构成显示模块。

2 软件设计

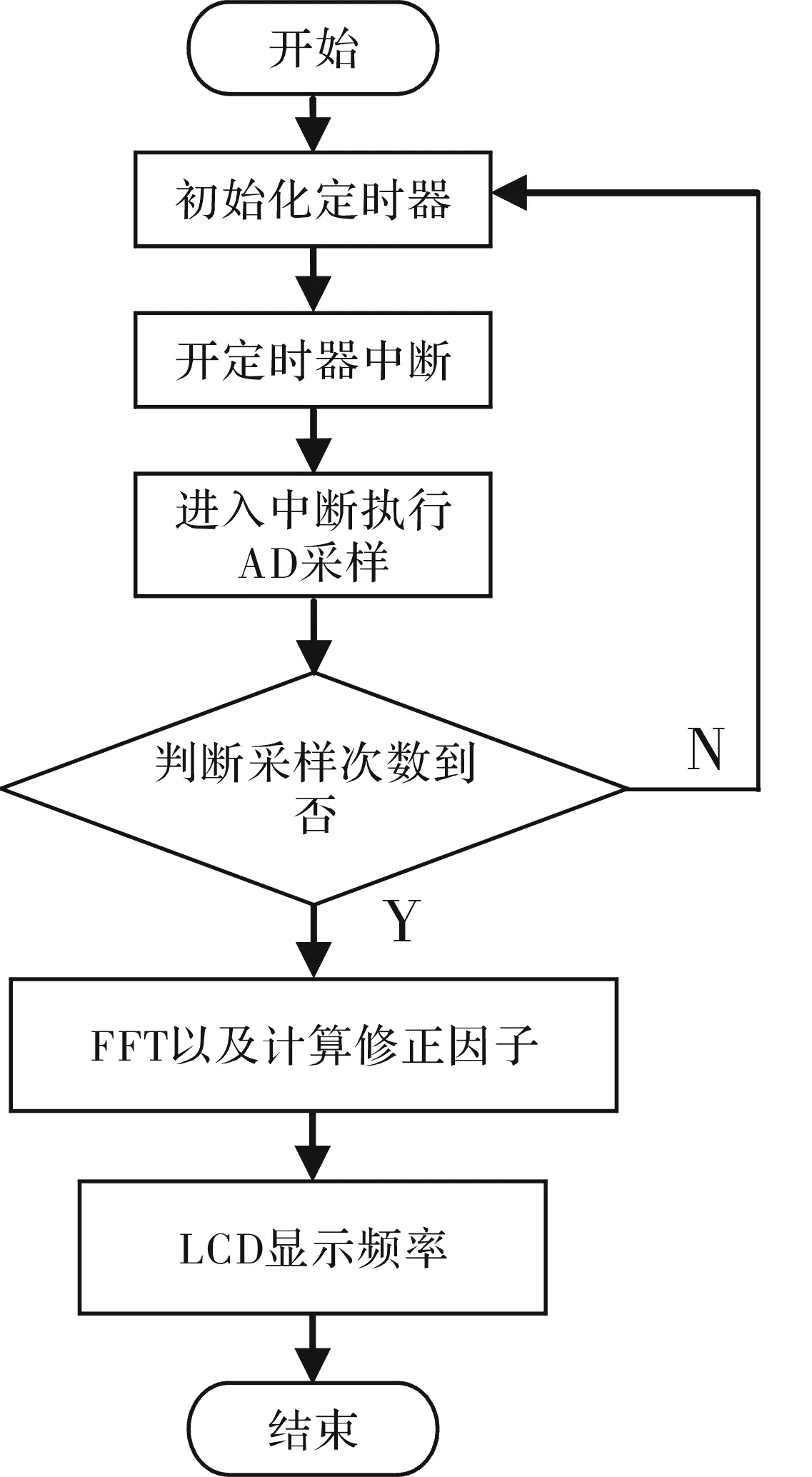

2.1 频率测试子程序

DSP外部晶振频率为150 MHz,以定时器0来监控采样周期,在每个定时器定时结束时完成一次采样。当所监测的信号周频率为50 Hz时,采样128个点,正负半波各64点采样,采样周期为156 μs,可保证0.04%的精度。嵌入式系统中对中断的要求是快速响应,处理程序简单便捷,该处设计为一次性采集够FFT所需的点数,采集完毕后再进行运算以确保实时响应速度[8]。当采样频率为6 400 Hz时采样1 024点,FFT频谱分辨率Ω0=fs/N=6 400/1 024=6.25 。

理论上FFT测试频理想情况下的原理是寻找谱线中最大值所处的位置n,则所测频率f=n×频谱分辨率,但由于实际情况下FFT受计算点数以及处理器运算能力影响,精度无法满足要求[9],尤其在当有接近被测信号频率的干扰噪声时会导致测试结果偏差,通常使用Rife算法对其进行修正,提取频谱中幅度最大与次大的两根谱线,引入系数r,当次大谱线在最大谱线的左边时,r=-1,反之则等于1,修正偏差的频率[10]

(1)

实际频率为

f=nΩ0+δ

(2)

频率测试流程如图6所示。

图6 频率测试流程

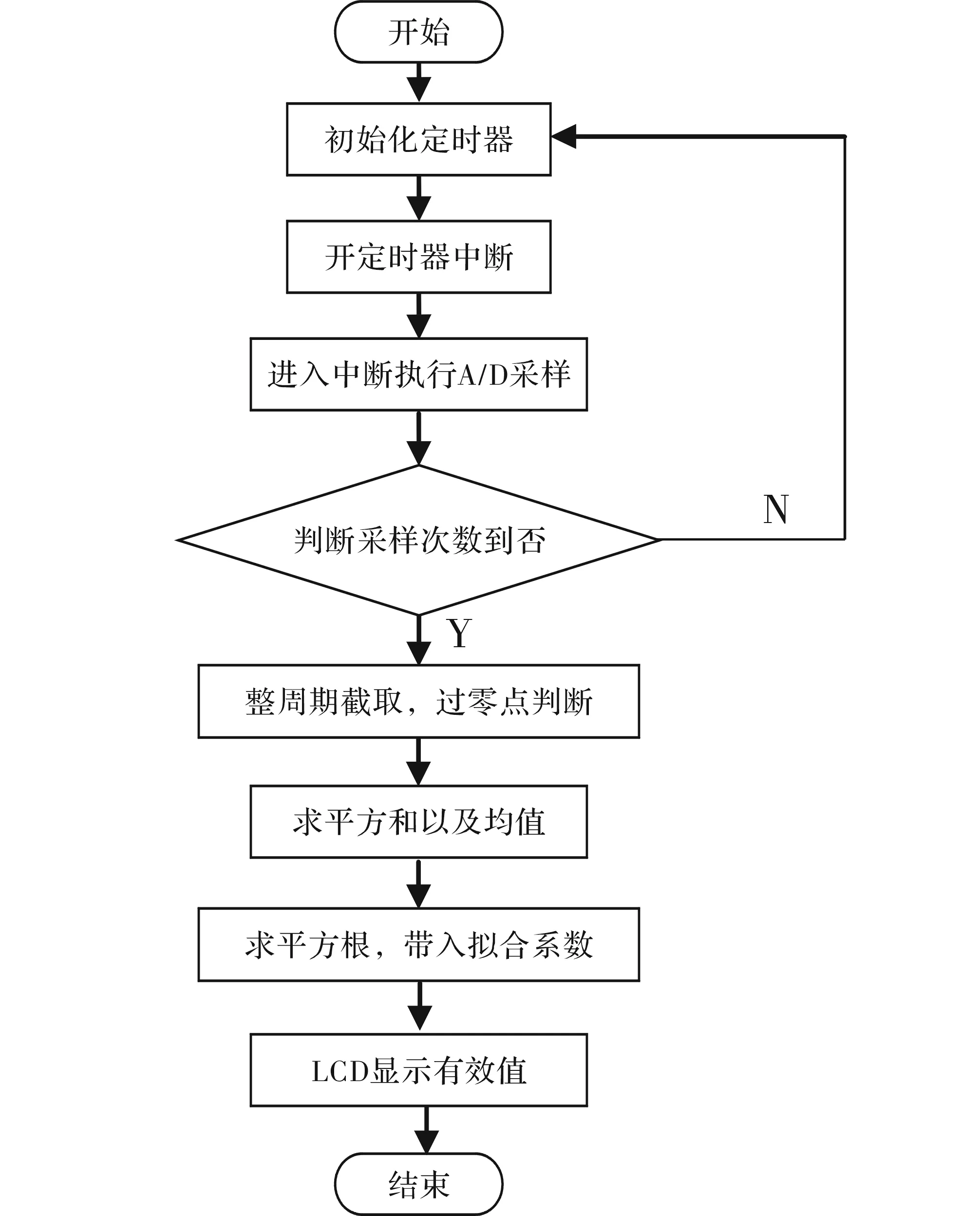

2.2 有效值测试子程序

有效值测量之前先要对各个测量点进行标定,标定时要求外部无干扰无噪声条件下测量到的数据,目的是求出较高精度的曲线拟合系数[5-6]。定标值为90~250 V外部输入交流电压下所测量的传感器输出的交流电压有效值,从90 V开始,每增加1 V电压定标一次有效值,设计两个数组,数组1存放90~250 V数值,数组2存放数组1每个元素对应的有效值,将数组固化到DSP的Flash中,上电后将该数组加载到DSP的片内RAM空间中,因为Flash中的数据与RAM空间通信时存在6个周期的延时,所以不能直接在Flash中直接查询数组。测量有效值之前先计算二元线性拟合的系数[11],经过计算后的系数为6.259 956和670.792 8,之后每次采样所得的有效值带入该系数算出对应的外部真实交流电压的有效值。

有效值计算要求计算正弦信号的真有效值,将一个周波的采样点数平方后求均值在开方,为加快计算速度,避免大量的乘法以运算,将有效值所对应的结果存储在一个数组内[12],有效值测量步骤:(1)A/D采集好的数据首先存放至临时数组,采样点数为1 024点,计算结束后关闭定时器,关闭A/D;(2)零点判断,为截取一个完整的正弦波,查询一个周波的起始和结束点,通过过零比较截取完整周期点数,为128点;(3)将各个点求平方后再取平均值再开方,计算当前输入波形的有效值;(4)线性拟合计算外部真实电压有效值。

图7 有效值测试流程

3 数据采集

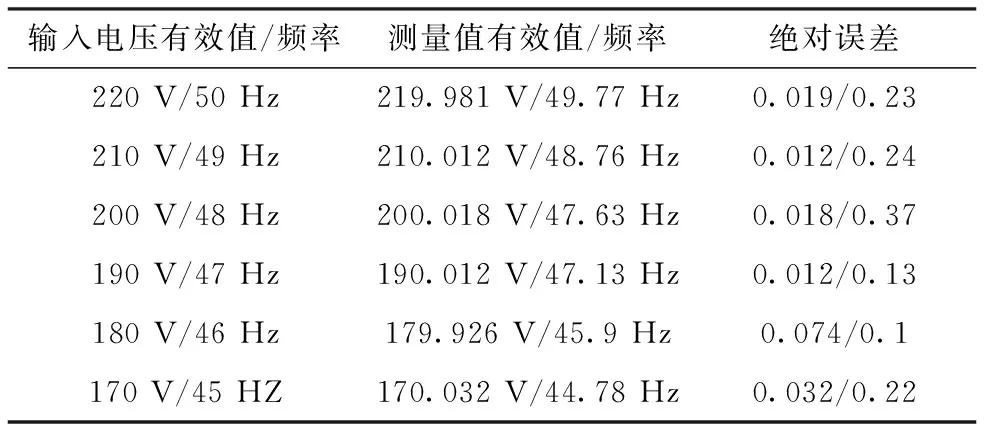

实验室条件下对该系统测试,外部输入有效值为220 V的交流电时,实测219.811 8 V,测试过程中只接入了一路信号,使用1路A/D。使用CCS5中的图形模块监控A/D采集到的电压[13]。实测多次数据结果如表1所示。

表1 实测数据

实际测量表明,该系统能满足工业用三相电的电压和频率的监控测量。

4 结束语

本文设计了一种基于DSP的工业在线电压以及频率检测系统,使用FFT算法完成频率检测,能达到较高的检测精度。该系统利用DSP快速运算的优势,利用线性拟合测量有效值,与传统的频率检测系统相比具有较灵活的检测方式,避免使用过多硬件带来的故障隐患,同时增加LCD人机交互界面,具有一定的实用价值。

[1] 康华光,陈大钦.电子技术基础模拟部分[M].6版.北京:高等教育出版社,2013.

[2] 邓振淼,刘渝,王志忠.正弦波频率估计的修正Rife算法[J].数据采集与处理,2006,21(4):473-477.

[3] 程佩青.数字信号处理教程[M].3版.北京:清华大学出版社,2012.

[4] 项正山,唐龙.基于AD采样量化编码体制的IFM设计[J].电子信息对抗技术,2013,28(3):79-82.

[5] 严志强,王雨,任开春,等.基于DSP、CPLD和单片机的高速数据采集装置设计[J].电力自动化设备,2007,27(5):110-113.

[6] 刘伟明,杜林,司马文霞,等.基于ARM与CPLD的电网过电压采集系统设计[J].高压电器,2009,45(3):36-39.

[7] 张永斌,胡金高.基于DSP的LCD显示控制与设计[J].液晶与显示,2011,26(5):626-630.

[8] 周慈航.嵌入式系统软件中的常用算法[M].北京:北京航空大学出版社,2010.

[9] 王兆华,侯正信,苏飞.全相位FFT频谱分析[J].通信学报,2003,24(11):16-19.

[10] 龚岳洲,周新力,孙小东,等.一种高精度的Rife算法[J].无线电工程,2013,43(2):30-33.

[11] 李俊秀,李明旭.基于DSP电压闪变在线检测方法及仿真[J].工业仪表与自动化装置,2015(5):117-120.

[12] 何菊明,王芙.实验数据的线性拟合及计算机处理[J].武汉工程大学学报,2008,30(1):117-119.

[13] 李全利,刘长亮.CCS上FFT运算的实现[J].自动化技术应用,2009,28(2):59-62.

Design of an Industrial Three-phase Voltage Monitoring System Based on DSP and CPLD

LI Jing,LIU Jian,LI Yu

(School of Optical-Electrical and Computer Engineering, University of Shanghai for Science and Technology, Shanghai 200093, China)

The modern industrial environment has too much interference noise due to the load variability. The traditional method of monitoring the voltage monitoring system is simple, meanwhile the detection accuracy of frequency detection is much more than that of the frequency. An industrial three-phase voltage detection system is designed based on the DSP and CPLD architecture, which combines the hardware and software, with the high precision current voltage transformer as the sampling element. The voltage effective value is calculated by linear fitting and the frequency by the FFT-Rife algorithm, using the LCD screen as man-machine interface. The system achieves the high precision measurement requirements, with small size, convenient debugging and installation site.

DSP; CPLD; FFT-Rife algorithms; linear fitting

2016- 04- 08

刘牮(1961-),男,副教授。研究方向:电子技术及嵌入式技术应用。李彧(1987-),男,硕士研究生。研究方向:智能控制与检测。

10.16180/j.cnki.issn1007-7820.2017.02.006

TN911.72

A

1007-7820(2017)02-022-04