AXI4总线的USB2.0设备控制器IP核设计*

2017-02-09韩进秦宏超刘锴

韩进,秦宏超,刘锴

(1.山东科技大学 信息科学与工程学院,青岛 266590; 2.山东高云半导体科技有限公司)

AXI4总线的USB2.0设备控制器IP核设计*

韩进1,秦宏超1,刘锴2

(1.山东科技大学 信息科学与工程学院,青岛 266590; 2.山东高云半导体科技有限公司)

本设计依托星核计划——山东国产IP软核平台,基于最新片上总线AMBA4.0协议,使用VerilogHDL语言完成了主要由AXI4总线接口、ULPI模式控制、封包、解包和协议处理等模块组成的USB2.0设备控制器的IP核设计,通过综合验证证明了设计的正确性,并有效降低了FPGA逻辑资源占用率。可以根据实际应用要求将设计的USB2.0控制器 IP核直接移植到FPGA内部,实现USB数据传输协议,省去了USB协议芯片,节省了产品开发成本,并且有效缩短了产品设计周期。

USB2.0;IP核;AXI4总线;VerilogHDL

引 言

Philips、Cypress等公司推出的各类USB芯片得到了广泛应用,但国内并没有厂商推出相关产品,特别是兼容USB2.0协议的接口芯片,几乎完全依赖国外产品[1-2]。目前国内对USB的相关研究更多的是利用国外的控制芯片进行产品开发,因此设计拥有自主知识产权的USB2.0 IP核显得尤为重要。本设计依托星核计划——山东国产IP软核平台,基于最新片上总线AMBA4.0协议,使用VerilogHDL硬件描述语言完成了USB2.0设备控制器的IP核设计及验证。

1 整体系统设计

图1是AXI4USB2.0设备控制器的整体架构图。该IP主要有寄存器管理模块、AXI总线接口模块、工作模式控制模块、数据包处理模块、协议处理模块和端点缓冲区模块组成。设计采用外接符合ULPI协议的PHY芯片。寄存器管理模块定义了USB设备控制器IP所需要的所有寄存器,用于管理整个IP的各种功能;AXI4总线接口模块实现IP与AXI4-Lite、AXI4-Stream总线的接口;基于ULPI的工作模式控制模块主要是检测USB总线状态,根据USB总线状态来控制整个IP核的工作状态;数据包处理模块和外接的PHY相连,用于实现USB物理层;协议处理模块主要功能是处理各种不同的传输事务,用于实现USB协议层;端点缓冲区模块主要用于缓存协议处理模块和AXI4总线之间需要交互的所有数据。

图1 整体架构

2 模块设计

2.1 AXI4总线接口模块

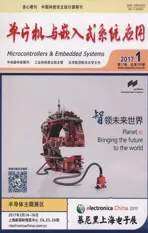

AXI4总线接口模块实现IP与AXI4-Lite、AXI4-Stream总线的接口,AXI4-Lite接口主要用于实现AXI4总线主设备对USB设备控制器寄存器的读写,AXI4-Stream接口用于AXI4主机完成对USB数据缓冲区的读写[3]。表1是AXI4-Stream I2C主机总线的端口信号及描述。

表1 AXI4-Stream I2C主机总线端口信号描述

AXI4-Lite总线的信号可以参考ARM公司的相关标准。

AXI4 Streamslave 接口具体实现如下:

assignaxis_wr_en=S_AXIS_TVALID;

always@(posedge S_AXI_ACLK)

if(!S_AXI_ARESETN)

axis_wr_addr<=13'b0; //复位清空写地址信号

else if(!S_AXIS_TVALID)

axis_wr_addr[12:0] <=axis_s_addr[12:0];

else

axis_wr_addr<=axis_wr_addr + 1'b1;

//数据有效写入下一个数据地址

assign axis_wr_data=S_AXIS_TDATA;

//总线写入主机读数据

AXI4 Stream Master接口具体实现:

regaxis_m_en_reg;

wireaxis_m_en_ris_edge;

always@(posedge S_AXI_ACLK)

if(!S_AXI_ARESETN)

axis_m_en_reg<=0;

else

axis_m_en_reg<=axis_m_en;

assignaxis_m_en_ris_edge = axis_m_en& (!axis_m_en_reg);

always@(posedge S_AXI_ACLK)

if(!S_AXI_ARESETN)

axis_rd_addr<=13'b0;

else if(!axis_rd_en)

axis_rd_addr[12:0] <=axis_m_addr[12:0];

else

axis_rd_addr<=axis_m_addr + 1'b1;

always@(posedge S_AXI_ACLK)

if(!S_AXI_ARESETN)

axis_rd_en<=1'b0;

else if(axis_m_en_ris_edge)

axis_rd_en<=1'b1; //上升沿总线读数据使能

else if(axis_m_sendov)

axis_rd_en<=1'b0;

always@(posedge S_AXI_ACLK)

if(!S_AXI_ARESETN)

data_send_count<=11'b0;

else if(axis_rd_en)

data_send_count<=data_send_count+1'b1;

//数据有效主机发送数据量加1

else

data_send_count<=11'b0;

assignaxis_m_sendov=(data_count==data_send_count) ? 1:0;

assign M_AXIS_TDATA=axis_rd_data;

assign M_AXIS_TVALID=axis_rd_en;

2.2 ULPI模式控制模块

基于ULPI的模式控制模块主要是检测USB总线状态,根据USB总线状态来控制整个IP核的工作状态,完成复位检测、设备挂起与恢复、高速握手等工作。模式控制模块有PHY_CLK和S_AXI_ACLK这两个时钟,其中非挂起状态检测RX_CMD的电路工作在PHY_CLK,其他电路基本都工作在来自AXI4总线的系统时钟域。模式控制模块采用状态机设计,如图2所示。

图2 模式控制模块状态图

图2中部分状态和跳转没有画出。除了与挂起相关的状态,其他状态只要是vbus无效(设备与HOST断开连接),状态机都会回到IDLE状态。

2.3 协议处理模块

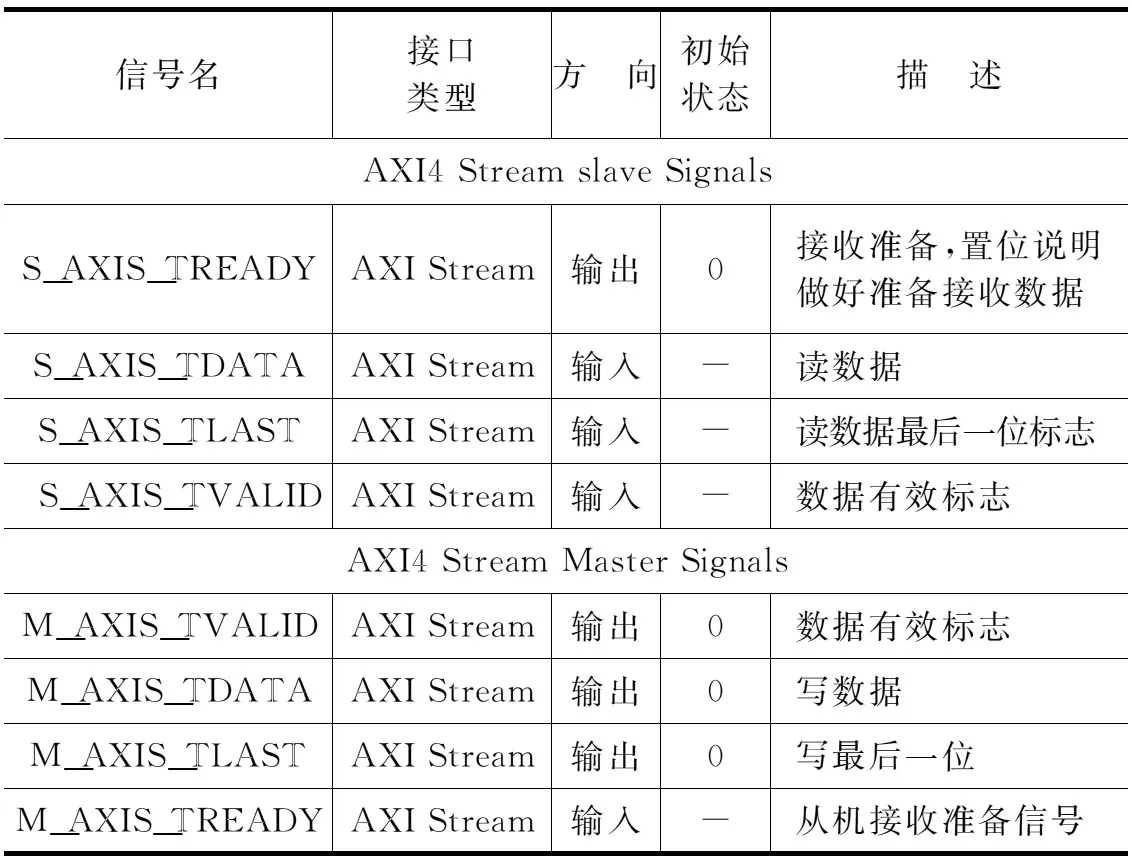

协议处理模块作用是完成USB2.0协议规定的各项功能,处理SETUP、IN、OUT等各项事务。USB2.0协议中定义了4种数据传输类型:控制传输(Control Transfer)、批量传输(Bulk Transfer)、中断传输(Interrupt Transfer)以及同步传输(Isochronous Transfer)。USB各种传输过程如表2所列。

表2 USB传输过程

2.3.1 USB控制传输

控制传输由2~3个阶段组成,分别是建立阶段、数据阶段(可能没有)和状态阶段,每个阶段都由一次或多次事务传输组成[4]。

(1) 建立阶段

主机从USB设备获取配置信息,并设置设备的配置值。建立阶段的数据交换包括了SETUP令牌包、紧随其后的DATA0数据包以及ACK握手包。它的作用是执行一个设置的数据交互,并定义控制传输的内容(即在数据阶段中IN或OUT的data包个数及发送方向,在建立阶段已经被设定)。如果建立阶段发送CRC错误,USB设备控制器不会有任何回应,如果正确接收到SETUP令牌包和8字节的DATA0数据包,USB设备控制器回应ACK,并且使能接收完成状态标志。

(2) 数据阶段

控制传输数据阶段包括控制读取(IN事务)和控制写入(OUT事务),控制读取是用于读取USB设备描述符,控制写入是用于传输USB设备的配置信息。控制读取和控制写入过程如图3所示。

图3 控制读取和控制写入过程

(3) 状态阶段

用来表示整个传输过程已经结束。状态阶段传输方向与数据阶段方向相反,即数据阶段是IN令牌包,状态阶段应为OUT令牌包;反之,数据阶段是OUT令牌包,状态阶段为IN令牌包。

控制传输事务处理流程比较复杂,采用了三段式状态机的方式进行设计,如图4所示。

图4 控制传输状态图

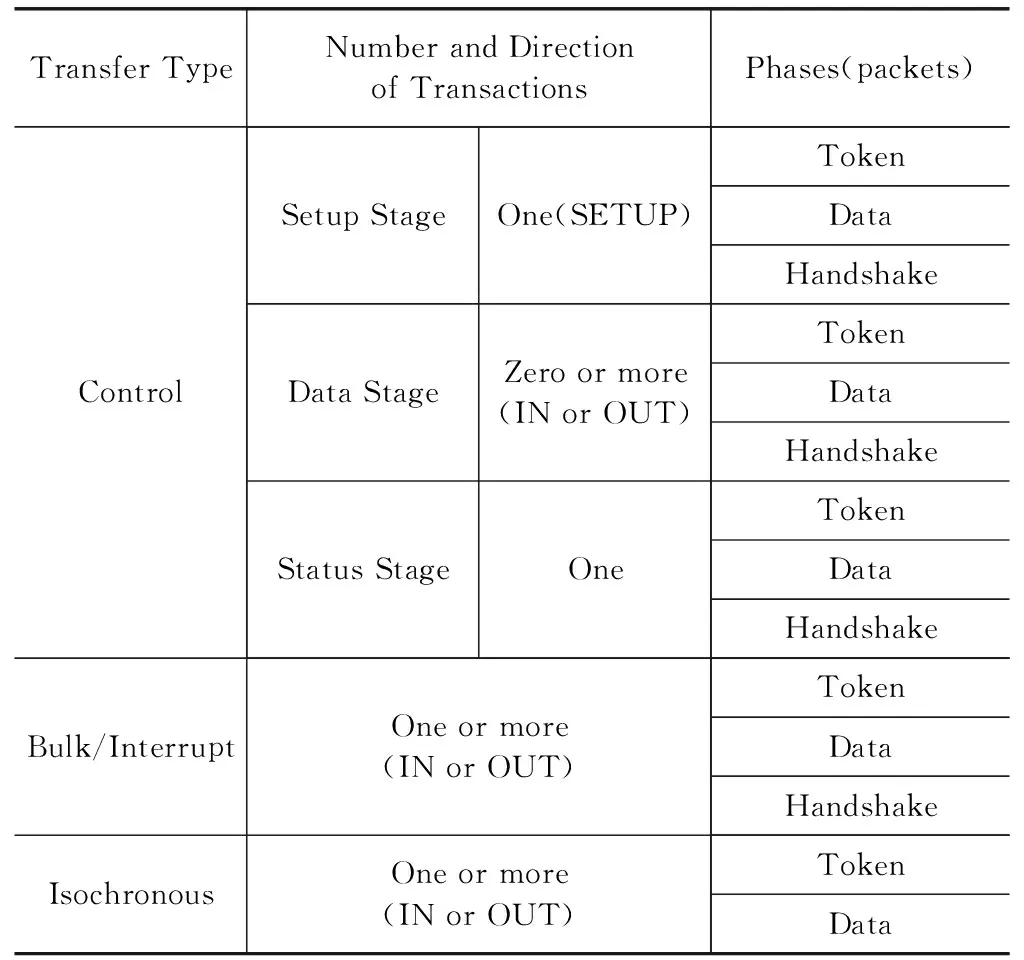

2.3.2 USB IN事务处理

USB的IN事务处理模块主要完成USB中批量、中断和同步传输的IN事务的处理,在主机给出IN令牌后,该模块发出向主机发送数据的指令信号。该模块会首先检测当前的端点、缓存是否可用,若端点挂起,发STALL;若缓存不可用,发NACK。该模块由状态机实现,流程如图5所示。

图5 IN事务处理流程图图

2.3.3 USB OUT事务处理

OUT事务处理状态机比较简单,图6是批量传输和中断传输OUT事务处理流程。图中NYET流程只有在批量传输中出现,中断传输中设备不会回应NYET。

图6 批量传输和中断传输OUT事务处理流程图

3 验证综合结果

3.1 VCS验证

由于USB2.0事务较多,协议比较复杂,采用纯信号的方式加入激励信号验证功能操作起来会非常复杂,实现比较困难。因此,为了提高验证效率,采用基于事务的角度加入激励。具体操作为在测试激励和待验证的USB2.0控制器之间加入附加层,使信号激励的加入转变为事务激励的加入,从而在测试时只需按不同事务的加入来验证控制器的功能。

以IN事务传输仿真验证为例,本设计使用Synopsys

公司的VCS仿真软件进行仿真验证。仿真如图7所示。图中给出的是端点1执行IN事务传输,当时钟上升沿dir置1开始由USB设备向主机发送数据,通过8位数据输出信号data_out[7:0]可以看出,首先完成握手发送握手包1f,之后传输令牌包,8’h69为IN 事务PID高4位,是第4位的取反,8’hd5和8’hd8包含的16位数据为7位ADDR、4位ENDP以及5位CRC5,由此可以知道ADDR为1010101B,ENDP为0001B即端点1执行IN事务传输。令牌包之后会接着发送一个1f握手包,之后发送数据(1a、2b、3c…为自定义的传输数据)。

图7 IN事务传输仿真

图8所示为编写testbench对各模块代码进行测试的结果,代码覆盖率超过90%,IP核逻辑正确。

图8 各模块代码覆盖率

3.2 Synplify Pro综合

通过综合工具Synplify Pro对IP核进行综合验证,综合验证结果如图9所示。

使用不同的器件、密度、速度和等级时,AXI4-LiteI2C主机总线IP的性能和资源利用情况可能不同。IP设计时,适配采用默认设置。AXI4USB2.0设备控制器IP核可以应用于高云的GW2A55系列FPGA。性能和资源利用情况如表3所列。整个IP核占用资源只有2100 LUTs,具有170个I/O接口,最高速率可达120 MHz。

表3 性能和资源利用表

结 语

[1] Philips Semiconductors. ISP1501 Hi-Speed Universal Serial Bus peripheral transceiver Rev.2[S].2002.

[2] Cypress Semiconductor Corporation. CY7C68000 USB2.0 UTMI Transceiver Datasheet[S].2003.

[3] ARM Corporation. AMBA4.0规范优化性能与功耗[J].微电脑世界, 2010(4): 6.

[4] 刘清明.USB2.0设备控制器IP核设计与验证[D].合肥: 中国科学技术大学, 2014.

USB2.0 Device Controller IP Core Based on AXI4 Bus

Han Jin1,Qin Hongchao1,Liu Kai2

(1.College of Information Science and Engineering,Shandong University of Science and Technology,Qingdao 266590,China;2.Shandong Gowin Semiconductor Technology Co.,Ltd.)

The design relies on the star nuclear program-Shandong domestic IP soft core platform.Based on the lastest on-chip bus AMBA4.0 protocol,the design of USB2.0 device controller IP core is completed using Verilog hardware description language,which includes the AXI4 bus interface module,the ULPI mode control module,the packet and unpacked module,the protocol processing module.The experiment results prove the correctness of the design,and it effectively reduces the logic resource utilization of FPGA. According to the actual application requirements, the designed USB2.0 controller IP core will be directly plant into the FPGA internal.It implementates the protocol of USB data transmission without the USB protocol chip.The design saves the product development cost and shorts the product design cycle effectively.

USB2.0;IP core;AXI4 bus;Verilog HDL

国家自然科学基金资助(项目编号:41572244);山东省自然科学基金(项目编号:ZR2015DM013)资助。

TP336

A

�迪娜

2016-08-08)