可编程引信高速编码信号测试仪

2017-01-16裴东兴王勇贞

谢 锐,裴东兴,王勇贞

(1.中北大学电子测试技术重点实验室,山西 太原 030051;2.中北大学仪器科学与动态测试教育部重点实验室,山西 太原 030051)

可编程引信高速编码信号测试仪

谢 锐1,2,裴东兴1,2,王勇贞1,2

(1.中北大学电子测试技术重点实验室,山西 太原 030051;2.中北大学仪器科学与动态测试教育部重点实验室,山西 太原 030051)

针对模拟环境下可编程引信高频编码信号无有效测试装置的问题,提出了基于高速数据采集和存储技术的高速编码信号测试仪。该测试仪以高速AD转换器与FPGA为核心,根据编码信号的特点对其进行有效的衰减和差分化,增强了测试仪的抗干扰能力减小了测试误差,采用并行双通道时间交替采样技术实现了200 MHz的高采样频率,使用FPGA实现高速控制时序逻辑和数据分区缓存,避免了高速存储中可能产生的丢点情况。实验结果表明,高速编码信号测试仪具有完整的记录信号波形,能满足高频引信编码信号测试要求,可作为可编程引信高频编码信号测试的有效装置。

引信;编码测试;并行采样;高速数据采集

0 引言

可编程引信是采用电磁感应技术通过位于炮口的线圈设定工作方式的,当引信随弹丸发射通过线圈时,发射线圈将编码信号传输给引信的接收线圈,因此编码过程的特点是时间短、信号频率高、工作环境恶劣[1-2]。编码信号的正确与否是影响引信综合性能的关键因素,在使用前需要对引信的编码装置进行全面的检测,确保其正常工作[3]。因此有效的试验与测试方法对引信而言是非常重要的。

目前对于引信装定方法的研究较多,而对装定结果的验证大都是通过原理样机进行测试,对于引信模拟环境下的编码测试方法及测试仪器的研究有限[4],不能满足引信测试的需要。近年来专用数据采集卡集成系统发展迅速,它的内部元件高度集成化,功能强大,采集速度快,存储容量大,可以覆盖从低频到高频、从低温到高温大范围的动态测量[5-6]。但其大多是针对工业控制领域,对于高频引信编码信号的测试无法采用现有的数据采集卡实现,本文针对此问题提出了基于高速数据采集和存储技术的高速编码信号测试仪。

1 高速编码信号测试仪原理

对编码信号检测时使用空气炮模拟引信发射过程的环境[7],高速信号测试仪与引信的信号接收端连接,通过空气炮发射,测试仪经过炮口的发射线圈时被触发,开始高速记录编码数据,记录完成后将测试仪取回与计算机连接将存储的数据传输至专用软件中进行显示,通过软件的数据处理和分析功能判断编码数据是否正确。

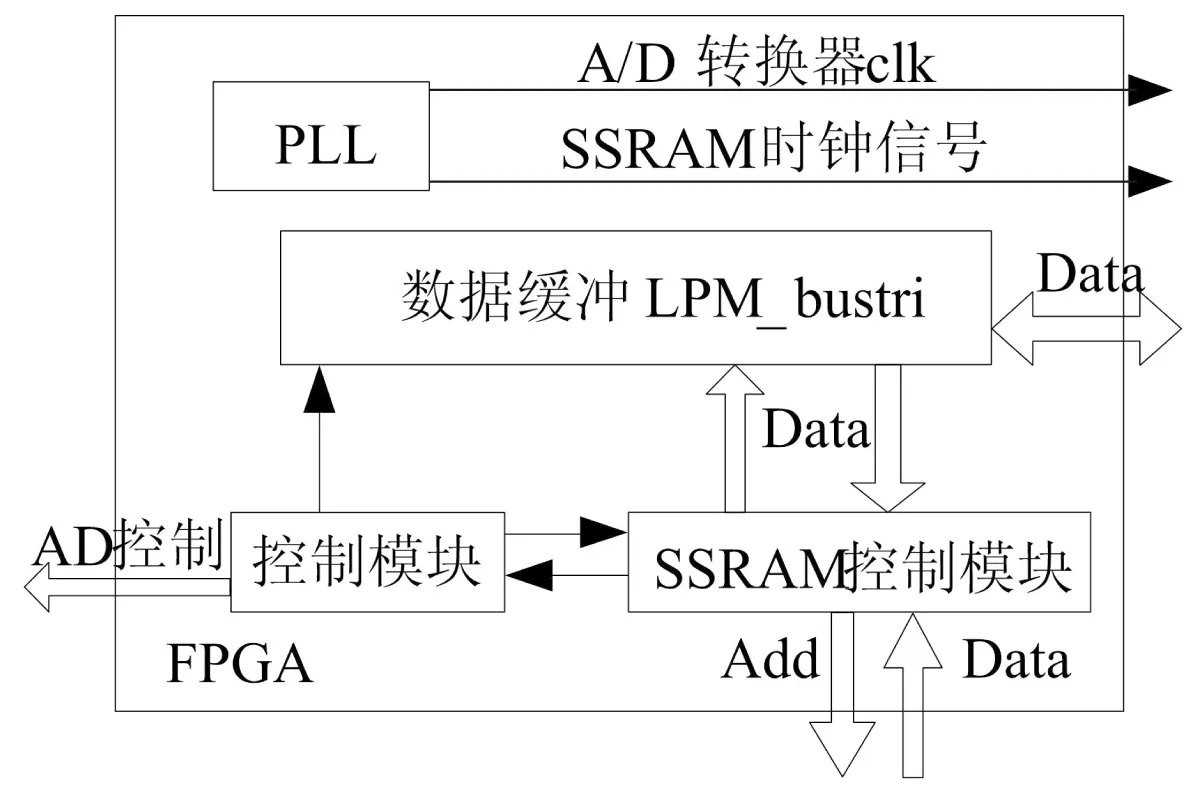

可编程引信的编码信号为脉冲序列,其幅值为6 V,最高频率分量可达50 MHz,输出阻抗为1.2 kΩ。测试要求高速信号测试仪的采样频率达到200 MHz,存储容量为1 MB,测试仪体积不大于Ф55 mm×100 mm,连续工作时间不小于4 h。根据以上要求采用双通道、8 bit、最高采样率为100 MHz的高速模数转换器AD9288实现编码信号的转换,选用CycloneⅢ系列的FPGA对高速数据转换和数据的存取进行控制,数据的存储选用同步静态随机存储器IS61VPS25636A,它的存储容量为1 MB,最大同步时钟频率能达到200 MHz。高速信号测试仪的结构框图如图1所示。

图1 测试仪结构框图Fig.1 Structure diagram

测试仪要达到200 MHz的采样频率,要使用AD9288的两个100 MHz数据采集通道并行工作[8]。它的两个通道可由各自的时钟来控制信号的转换,采用FPGA给两个通道分别提供同频率、相位相差180°的转换时钟[9],两通道均在时钟的上升沿对同一输入信号进行采样,也就是在一个时钟周期内得到两个采样点,即并行双通道时间交替采样技术。两通道分别输出的8 bit数据经FPGA以乒乓结构缓存,之后再以较低的速度写入静态存储器中[10]。采取这种模式可以有效地提高测试仪的采样率同时减轻了数据传输和存储的压力,保证了测试结果的可靠性。

2 高频编码信号的调理

根据编码信号的特征在进行模数转换之前需要将信号进行调理,以满足ADC对输入信号有效范围和模式的要求,因此信号调理包括衰减和差分化两部分。

2.1 信号的衰减

由于编码信号属于高频信号,不能通过简单的电阻串联实现衰减,在衰减的同时还需要考虑阻抗匹配的问题。所设计的信号衰减电路如图2所示。

图2 信号衰减电路Fig.2 Signal attenuation circuit

通常衰减电路中的电容比较小,当信号频率很低时,衰减电路的分压比仅由电阻决定,但对于高频的输入信号,容抗对于信号的影响会大于阻抗。由于编码信号频带较宽,当信号频率改变时,衰减电路中R1+R2、C1的并联阻抗Z及R3和C2的并联阻抗Z′均会随信号频率变化,为了能在较宽的频率范围内使衰减电路的分压比保持不变,需要适当选择阻容元件的大小。

衰减电路的分压比为:

(1)

当编码信号频率改变时衰减电路的分压比保持不变则需要满足:

即:R3C2=(R1+R2)C1

(2)

衰减电路中两个阻容元件的时间常量(R1+R2)C1和R3C2必须相等,否则衰减后的信号会产生失真。因此电路中选择R1为10 MΩ,R2、R3为1 MΩ,C1为8 pF,C2为88 pF。此信号衰减电路带宽范围较宽,输入阻抗高,可以把幅值为6 V的编码信号不失真的衰减到500 mV,满足AD9288对信号输入范围的要求。

2.2 信号的差分化

由于AD9288要求差分信号输入,所以需要把衰减后的编码信号转为差分模式。设计采用集成信号调理芯片AD8138将信号差分化,在保证AD的模拟输入信号稳定的同时尽量避免噪声信号的引入,增强测试仪的抗干扰能力。

在高速电路中的设计中,需要考虑由于传输线阻抗失配引起的信号反射问题,因此在AD8138的正负输出端各使用一个50 Ω的串联电阻分别与AD转换器的IN+和IN-端连接。此外,为了避免产生共模噪声要求AD8138的输出信号差分对的布线紧凑且等长,保证等值反相。图3为信号差分化电路,其中R6=R5且R1=R2。由于输入的编码信号阻抗较小,所以四个电阻R1、R2、R5和R6阻值均为500 Ω。

图3 信号差分化电路Fig.3 Signal differencing circuit

3 高速数据采样存储技术

3.1 并行双通道时间交替采样技术

前文所述高速信号测试仪设计采用AD9288以并行双通道时间交替采样方式工作,其具体过程是:给AD9288的通道A、B分别提供100 MHz的采样时钟,通道A在时钟上升沿采得样本点,通道B在时钟下降沿采得样本点,如果两通道的采样时钟相位相差180°,也就是两通道之间的采样时间间隔为5 ns,相当于在10 ns的时间内对输入模拟信号进行了两次采样,测试仪的采样率就可达到200 MHz。最后将两通道的采样数据按相应的顺序拼接后形成一个完整的数据输出。

AD9288工作时序如图4所示,其中通道A在ENCODE A上升沿tA到来后开始对输入信号第N点采样,4个脉冲之后从通道A输出数据DATAN,通道B在ENCODE B上升沿即ENCODE A下降沿对输入信号第N点采样,4个脉冲之后从通道B输出数据DATAN,将两通道的数据按序存储,也就是在ENCODE A的一个周期内得到了两个DATA数据输出。当下一个时钟ENCODE到来后,通道A和通道B均对其输入信号第N+1点采样,同样分别得到DATAN+1数据输出,输出数据经过FPGA缓存。

图4 AD9288时序图Fig.4 AD9288 timing chart

3.2 FPGA高速控制逻辑设计

作为高速信号测试仪的控制核心FPGA为ADC提供采样时钟,将转化后的数据以正确的顺序在内部缓存,并控制SSRAM对数据的存储和读取。FPGA内部功能模块划分如图5所示。在设计时,AD9288需要两路相位相反的100 MHz的转换时钟,对SSRAM的操作需要时钟,FPGA内部逻辑需要时钟,另外通过USB与上位机连接进行操作时也需要时钟,因此需要考虑满足对不同频率的多个时钟的要求。高速数字电路在逻辑设计时对时钟的稳定性要求很高,时钟的抖动和延迟需要控制在最小的范围内,以保证多个时钟到达各个寄存器的延迟最小,避免出现信号不完整的问题。

图5 FPGA内部功能模块Fig.5 Internal function modules of FPGA

基于以上分析设计利用FPGA内部的锁相环通过全局时钟网络产生多个同源时钟,满足测试仪对多时钟以及时序约束的要求。选用的EP3C16Q240C8N内部包含四个锁相环,每个锁相环最多有五个时钟输出,采用外部50 MHz晶振作为锁相环的时钟输入,通过全局时钟网络经PLL倍频得到两个相位差为180°的100 MHz时钟CLKA和CLKB作为AD9288两个通道的采样时钟,再倍频得到一个200 MHz时钟GCLK用于测试仪的逻辑控制,GCLK通过检测其他时钟边沿变化来实现不同时钟的同步,图6所示为FPGA时钟产生模块的时序仿真结果。

图6 锁相环时序仿真Fig.6 PLL clock logic simulation

3.3 数据的高速存储

高速信号测试仪设计的并行双通道时间交替采样技术使其对存储器操作速度的要求有所降低。测试仪采用的同步静态随机存储器IS61VPS25636A有32根数据线,在对转换后的数据进行存储时,首先将AD9288两个通道输出的数据在FPGA内部缓存,FPGA内部构建了四个寄存器,全部写满后同时再将数据写入到外部存储器中,这样数据写入的速度进一步降低,使得数据的高速存储更易实现。

图7为存储器写时序仿真结果。其中DataA和DataB是AD9288两通道的数据,两通道在一个采样周期10 ns产生的两个数据缓存到FPGA的A、B两个寄存器中,下一个采样周期产生的两个数据缓存到C、D两个寄存器中,之后一次写入外部存储器中。也就是将每10 ns产生的两个数据按照每20 ns进行一次写数据操作,在AD采样频率为200 MHz的情况下,写数据的频率为50 MHz。通过降速避免了高速数据传输中丢点的情况,同时也可以方便对存储器进行操作。

图7 SSRAM写时序仿真Fig.7 SSRAM write timing simulation

4 实验测试结果

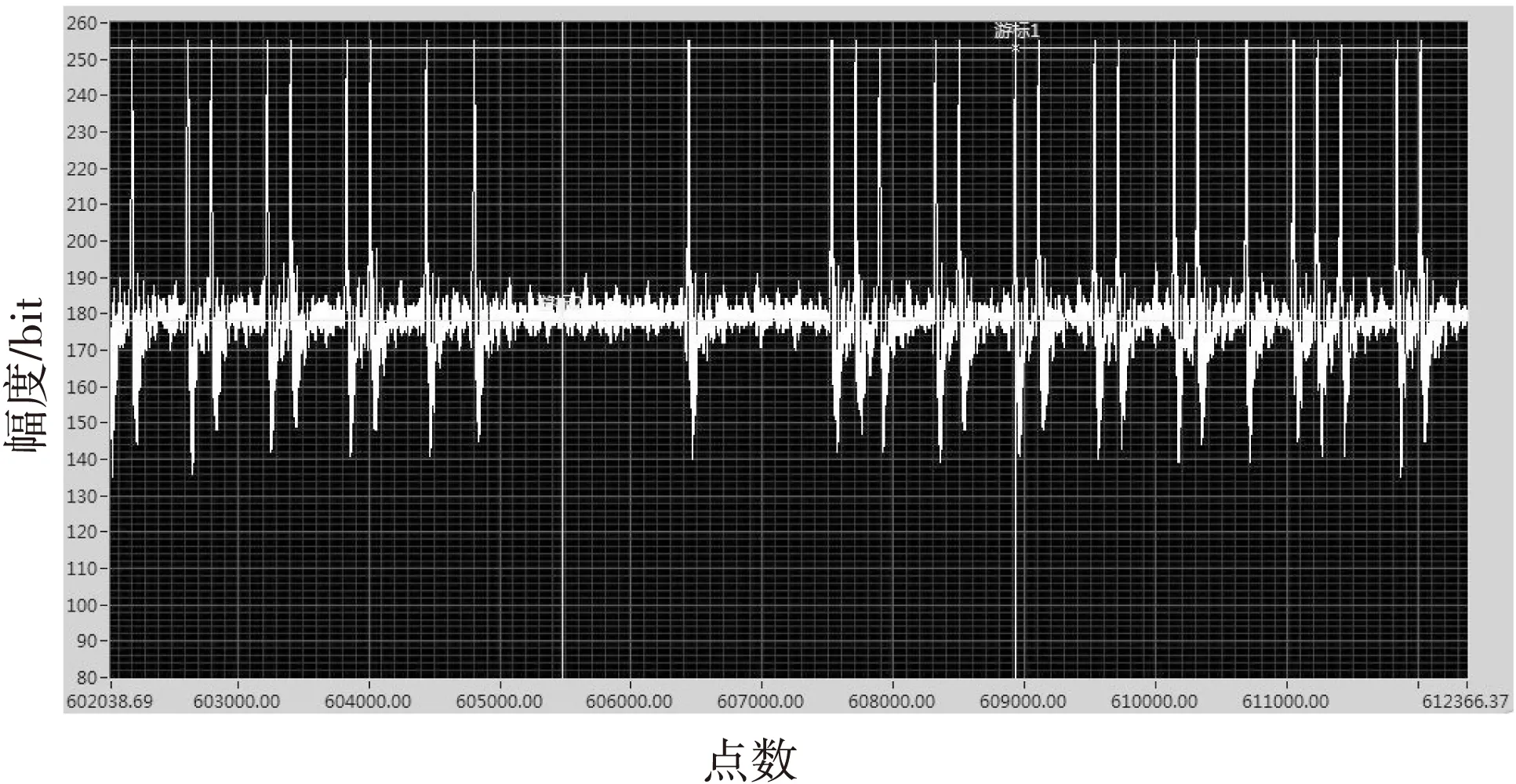

使用高速信号测试仪在空气炮上对引信编码信号进行了测试,编码发射装置安装在炮口处。测试仪体积为168 cm3,经过灌封后可承受2万g的冲击,满足在空气炮上进行测试的要求。由于引信编码为电磁感应方式,因此测试仪的外壳选用磁导率小的材料对磁场进行屏蔽,防止磁场对测试仪的正常工作产生影响。测试仪发射后通过炮口的磁环时被触发,开始记录引信收到的编码信号,记录完成后将测试仪与上位机连接进行数据的读取,并在软面板上显示编码信号波形。图8为其中一组编码信号,从中可以看出编码信号是一系列脉冲,经过去噪等处理后编码信号如图9所示,可以看出编码信号波形完整,信号幅值、频率和编码次数与预设的编码信号特征吻合,达到了预期测试结果。

图8 编码信号序列Fig.8 Encoding signal sequence

图9 处理后的编码信号波形Fig.9 Processed encoding signal waveform

5 结论

本文提出了可编程引信高速编码信号测试仪。该仪器基于高速数据采样和存储技术,以高速AD转换器与FPGA为核心,测试仪根据编码信号的特点对其进行有效地衰减和差分化,增强了测试仪的抗干扰能力减小了测试误差,采用并行双通道时间交替采样技术实现了200 MHz的高采样频率,使用FPGA实现高速控制时序逻辑和数据分区缓存,避免了高速存储中可能产生的丢点情况。所设计的高速编码信号测试仪具有小体积、抗高冲击的特点。在空气炮上进行了实验测试,实验结果表明,高速编码信号测试仪可以完整地记录信号波形,能满足高频引信编码信号测试要求,可作为可编程引信高频编码信号测试的有效装置。

[1]曲秀杰,李喆,李杰. 电子时间引信装定技术研究[J]. 探测与控制学报,2001,33(3):21-24.

[2]李长生,张合. 基于磁共振的引信无线装定方法[J]. 探测与控制学报,2014,36(2):1-6.

[3]吴晓颖,张万君,杨雨迎,等. 可编程电子时间引信保险距离动态试验方法的优化设计[J]. 制导与引信,2009,30(1):1-5.

[4]王兵,阮朝阳. 引信电子安全系统片上可编程测试仪通用性技术[J]. 探测与控制学报,2013,35(3):61-64.

[5]孙波. 基于PCI总线的高速数据采集卡的设计[D]. 成都:电子科技大学,2007.

[6]马海潮. 超高速数据采集技术发展现状[J]. 测试技术学报,2003(4):287-292.

[7]齐杏林,杨清熙,文健,等. 基于气体炮的引信动态模拟方法综述[J]. 探测与控制学报,2011,33(4):1-5.

[8]邱渡裕,田书林,叶芃,等. 基于并行结构的随机等效时间采样技术研究与实现[J]. 仪器仪表学报,2014,35(7):1669-1675.

[9]汤少维. 基于FPGA控制的高速数据采集系统设计与实现[D]. 成都:电子科技大学,2007.

[10]王勇贞. 高速数据采集与存储系统设计[D]. 太原:中北大学,2013.

High-speed Encoding Signal Test Instrument of Programmable Fuze

XIE Rui1,2, PEI Dongxing1,2, WANG Yongzhen1,2

(1. Science and Technology on Electronic Test and Measurement Laboratory,Taiyuan, 030051, China;2. Key Laboratory of Instrumentation Science & Dynamic Measurement, Ministry of Education, North University of China, Taiyuan, 030051, China)

For the situation that programmable fuze high frequency encoding signal have no valid test instrument under simulated environment, a high-speed coding signal test instrument based on high-speed data acquisition and storage technology was proposed. It had high-speed AD converters and FPGA as the core, by effective signal attenuation and differencing according to the characteristics of the encoding signal, enhanced anti-jamming capability and reduced the measurement error. It was designed through a parallel two-channel time alternate sampling technology to achieve a high sampling frequency of 200 MHz. A high-speed timing control logic and data cache partitions in FPGA was used to avoid lost points in high speed transmission. Experimental results showed that it could meet the requirements of high-frequency fuze coding signal test, recording signal waveform was accomplished. The experimental results were accurate and reliable, which could be used as an effective instrument for programmable fuze high frequency coding signal testing.

fuze encoding test;parallel sampling;high speed data acquisition

2016-07-03

谢锐(1983—),女,山西太原人,博士,讲师,研究方向:动态测试与智能仪器。E-mail: zbxierui@163.com。

TJ430.6

A

1008-1194(2016)06-0026-05