反走样字符图形叠加算法与FPGA快速实现

2017-01-05全颖夏伟杰周建江

全颖,夏伟杰,周建江

(南京航空航天大学 电子信息工程学院,南京 211100)

反走样字符图形叠加算法与FPGA快速实现

全颖,夏伟杰,周建江

(南京航空航天大学 电子信息工程学院,南京 211100)

为了提高机载平视显示系统中反走样字符图形与背景视频叠加输出的显示效果,提出一种反走样字符图形与视频叠加算法并通过FPGA快速实现。叠加过程中增加反走样字符图形背景融合计算,使反走样字符图形与背景视频叠加后边缘光滑过渡,系统使用两片DDR3分别存储视频和图形数据,两者并行处理,提高系统整体性能,优化背景融合算法DDR3实现流程,降低DDR3中断复杂度。结果表明,该系统整体性能得到提高,叠加融合画面效果良好,灵活性强,适用于机载座舱显示系统。

视频叠加;背景融合;反走样;FPGA;DDR3

引 言

随着机载座舱显示系统的发展,对字符图形与背景视频叠加输出时的显示效果要求越来越高,尤其是反走样字符图形与背景视频的叠加处理效果。常见的处理方式是采用字符图形芯片直接生成反走样字符图形画面,然后通过FPGA与采集的背景视频进行叠加处理[1]。由于无法区分芯片生成的反走样字符图形数据,只能进行简单的叠加处理,叠加后的字符图形与视频交接边缘锯齿明显,影响显示效果。

本文设计一种基于FPGA的反走样字符图形与视频叠加处理系统,使用单片FPGA实现字符图形生成、视频采集处理以及两者叠加输出功能。对于反走样字符图形,在与背景视频叠加前先做背景融合处理,使反走样字符图形与视频叠加后边缘光滑过渡,明显削弱边缘锯齿效应。使用两片DDR3并行存储,加快了系统运转速度,为更高分辨率做准备。整个系统采用单片FPGA实现,灵活性强,可以减少系统的体积和功耗。

1 字符图形与视频叠加系统框架设计

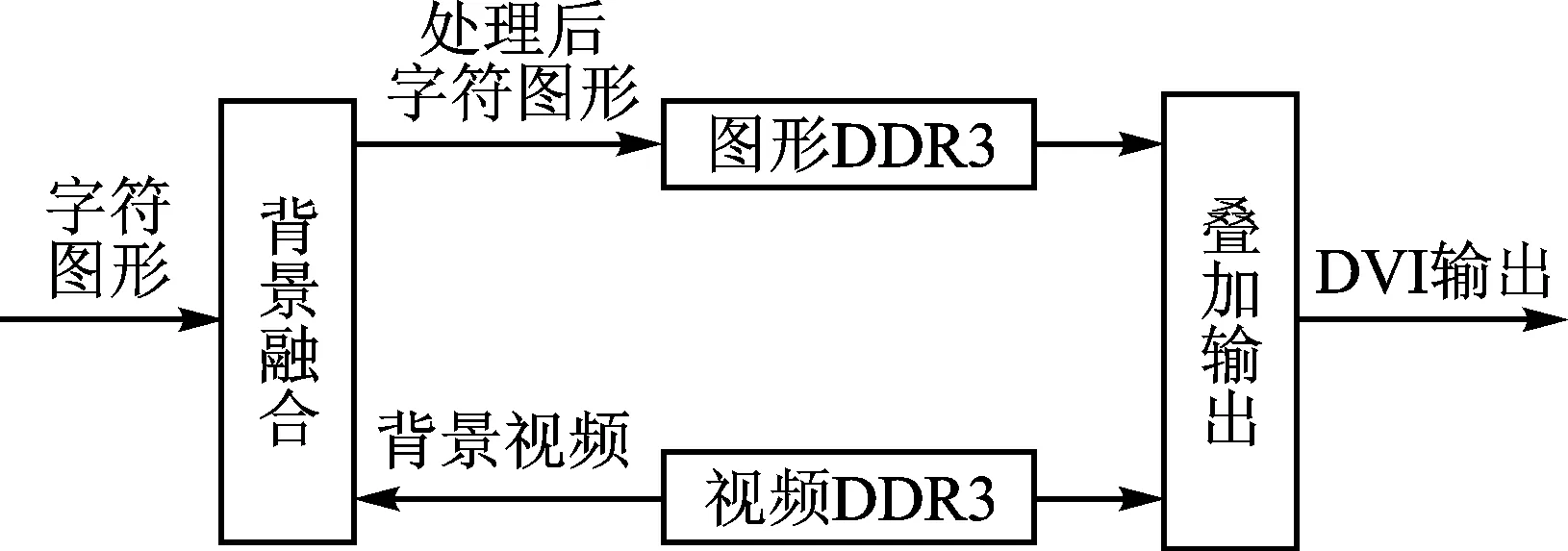

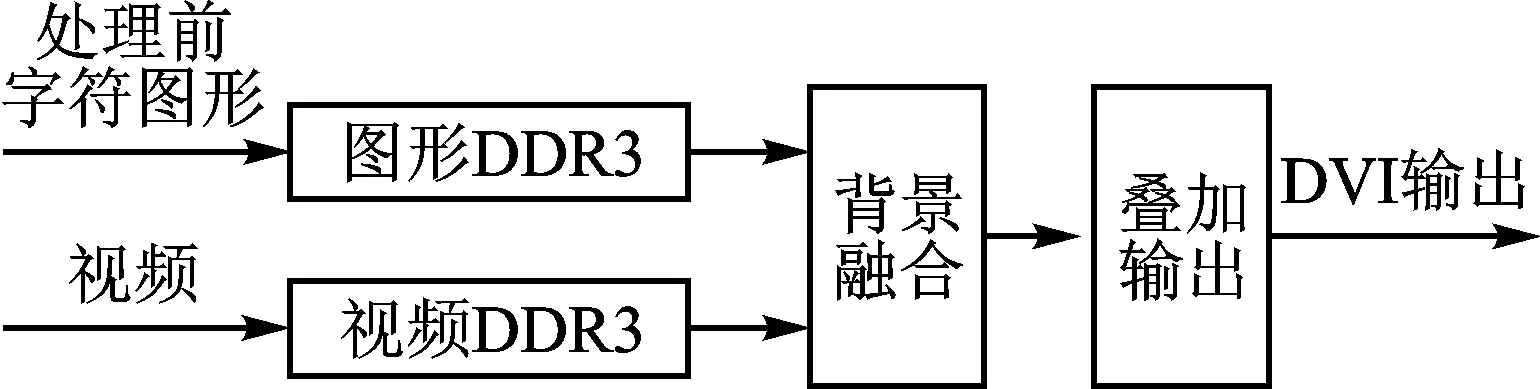

字符图形与视频叠加系统以Xilinx公司的Kintex-7 FPGA为核心[2],实现视频处理、字符图形生成和视频图形叠加输出等一系列功能。具体系统框图如图1所示,主要包括以下5个模块:

① 主机接口模块:通过PCIe总线接收来自CPU的视频处理指令和字符图形绘制指令,对各个指令进行解析,提供给子模块进行处理。

② 视频处理模块:接收PAL和DVI两种制式的视频,选择其中一路视频进行缩放、旋转处理后存入视频DDR3存储单元。

③ 字符图形生成模块:根据绘图指令绘制相应字符和图形,存入图形DDR3存储单元。

④ DDR3存储控制模块:实现DDR3的存储中断控制和中断嵌套功能。

⑤ 叠加输出模块:将背景视频数据和字符图形数据叠加输出,一路直接通过DVI接口输出到显示器,另一路经过畸变校正[3]后输出到平视显示器。

图1 字符图形与视频叠加系统框图

2 反走样字符图形叠加算法研究

2.1 字符图形与视频叠加原理

字符图形与视频叠加是指以字符图形为前景,视频作为背景,将字符图形的有效数据覆盖在视频之上输出[4]。字符图形与背景视频叠加输出时,当图形RGB数据为0时,表示该点没有字符图形输出,则该点输出背景视频数据,否则输出字符图形数据[5]。具体比较如下所示:

(1)

式中,G表示字符图形RGB值,Gbk表示背景视频RGB值,Gout表示最终DVI输出的RGB值。

反走样字符图形与背景视频叠加的Matlab仿真效果图如图2所示。

图2 反走样字符图形与背景视频直接叠加示意图

其中反走样斜线是采用wu反走样方式[6]绘制的单线宽斜线,反走样字符是用FreeType字体引擎提取的256级灰度值位图[7]。从图2中可以看出,反走样斜线和字符与背景视频直接叠加时,边缘有明显的锯齿状,影响显示效果,不利于飞行员识别,降低了人机功效。所以在反走样字符图形与背景视频叠加前,需要对反走样字符图形数据做背景融合处理,在反走样点中加入视频信息,再与背景视频按照式(1)进行叠加处理。

2.2 反走样字符图形背景融合算法

反走样图形以wu反走样单线宽斜线为例,反走样斜线绘制时每个点对应的显示颜色值为Gorig×(1-d),Gorig为理想斜线显示颜色,d为斜线绘制点到理想斜线的距离[8]。为了消除反走样图形与背景视频叠加时的边缘锯齿效应,在反走样斜线绘制的颜色中需要加入背景视频信息,两者按一定的比例进行融合,使得反走样点颜色信息与背景视频相关。反走样图形背景融合公式如下:

(2)

其中Gmix为反走样图形与背景视频融合后的颜色值。

反走样字符通过FreeType字体引擎提取,直接提取出反走样字符每个点的显示颜色,将字符每个点的颜色值与背景视频作如下处理:

(3)

(4)

如果视频数据或者字符图形数据中有彩色数据信息,则需要将对应的RGB值均按照式(2)或式(4)进行计算,得到新的RGB三个分量的值。

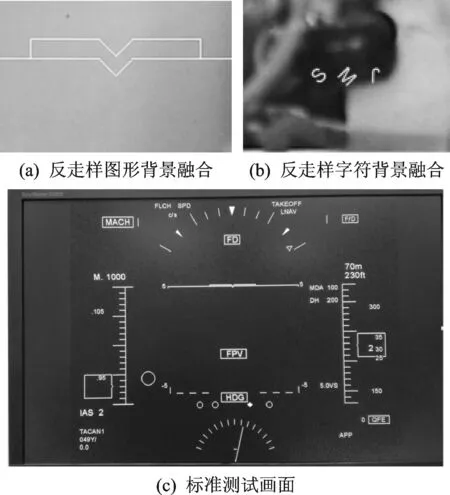

将反走样字符图形分别按照式(2)、式(4)作背景融合处理,处理后的数据按照后文第3.1节所述方式与背景视频叠加,背景融合后的叠加效果图如图3所示。经过背景融合的反走样字符图形与视频叠加后边缘锯齿明显减弱,图形和视频之间光滑过渡,显示效果明显提高。

图3 反走样字符图形背景融合后与视频叠加示意图

3 FPGA设计与快速实现

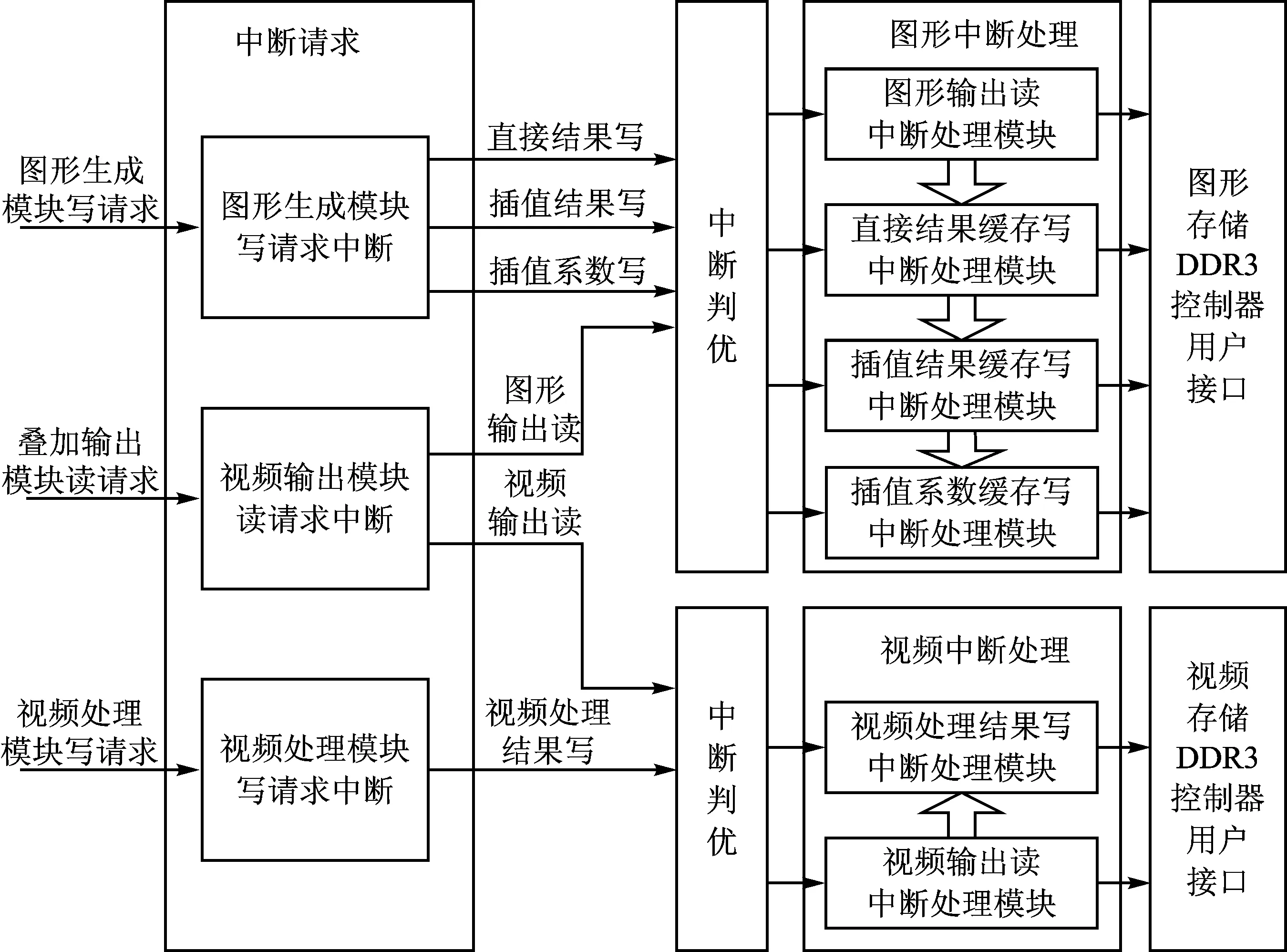

图5 先背景融合再存储DDR3用户接口仲裁控制框图

本设计采用两片DDR3分别存储视频和字符图形数据,两者并行存储和读取数据,与使用单片DDR3相比,一帧画面的存储和读取时间缩短为原来的50%,提高了系统的整体性能,可以处理更高分辨率的视频图形画面。

硬件实现反走样字符图形背景融合计算与叠加时,需要同时用到两片DDR3中的数据,降低两片DDR3中断复杂度并综合实际字符图形和视频的存储特点,是FPGA逻辑实现时主要考虑的问题。

针对本系统,背景融合处理有两种实现方案,方式一先对反走样字符图形数据作背景融合处理后再存入图形DDR3;方式二先将反走样字符图形数据直接存入图形DDR3,再与视频叠加输出前作背景融合处理,然后与背景视频叠加输出。

3.1 先背景融合再存储

图4为先背景融合计算再存储的逻辑实现框图。反走样字符图形数据先与从视频DDR3读出的背景视频数据作融合计算,然后将计算结果存入图形DDR3,叠加输出时直接使用从图形DDR3中读出的数据与视频叠加输出[9]。

图4 先背景融合再存储逻辑实现框图

使用先背景融合再存储的方式对应的DDR3读写中断如图5所示。图形中断处理模块中,按照中断优先级从高到底依次为:图形输出读中断处理、直接结果写中断、插值结果写中断。其中图形输出读中断则读出字符图形颜色值;直接结果写中断对应的是字符图形数据中不反走样点的颜色值写操作;插值结果写中断对应的是字符图形数据中反走样点经过背景融合计算后的颜色值写操作。视频中断处理模块,按照中断优先级从高到低依次为:视频输出读中断、视频处理结果写中断、读背景视频中断。其中读背景视频中断对应背景融合计算时,需要从视频DDR3中读取相应视频数据的操作。

图形生成模块写请求对应的中断处理框图如图6所示,当一帧图形绘制结束后,图形生成模块发送图形DDR3写请求,此时先执行图形直接结果写中断,同时申请插值背景读中断。插值背景读中断每读回一个视频数据,则和对应反走样点做背景融合计算并存入新的FIFO,等所有反走样点都作完背景融合计算后,再执行插值结果写中断。

图6 图形生成模块写请求对应的中断处理框图

先背景融合再存储的优点是所有存入图形DDR3的数据都是有效数据,叠加输出时无需作多余处理,直接输出即可。缺点是两片DDR3之间处理有交集,增加了各自中断处理的复杂度;当反走样点较多,同时视频处理结果写效率较低时,可能存在不能在一帧图形处理时间内将所有反走样点都作背景融合处理并存入DDR3的情况;对于PAL格式的输入视频以DVI格式输出时,需要进行帧速率提升[10]处理,导致与反走样字符图形做背景融合的视频数据和最后叠加输出的视频数据可能不是同一帧数据,叠加后边缘还会存在明显锯齿。

3.2 先存储再背景融合

图8 先存储再背景融合DDR3用户接口仲裁控制框图

图7 先存储再背景融合的逻辑实现框图

使用先存储再背景融合方式对应的DDR3读写中断如图8所示。图形中断处理模块中,按照中断优先级从高到低依次为:图形输出读中断处理、直接结果写中断、插值结果写中断和插值系数写中断。视频中断处理模块,按照中断优先级从高到低依次为:视频输出读中断、视频处理结果写中断。一帧图形绘制结束,图形生成模块发送图形DDR3写请求,先执行直接结果写中断,然后执行插值结果写中断,最后执行插值系数写中断。视频DDR3只需要完成视频叠加输出读中断和视频处理结果写中断即可,无需增加读背景视频的操作。

对比两种方式,方式一中增加了背景视频读中断处理,方式二中增加了插值系数写中断,虽然中断方式不同,但是两者读出或写入的数据个数是相同的,即两片DDR3总吞吐量不变。方式二中两片DDR3各自存储数据,互不影响,可以加快存储速度;而且在叠加输出前进行背景融合计算,可以保证和反走样字符图形作背景融合的数据就是将要叠加输出的视频数据,保证了叠加后的显示效果。所以最终选择先存储再背景融合的方式用于硬件实现。

3.3 背景融合FPGA实现

经过比较,选择先存储再背景融合的方式用于反走样字符图形背景融合计算硬件实现。硬件实现时,FPGA内部逻辑时钟为200 MHz,除了视频采集模块需要根据输入视频信号确定时钟,其余模块均使用200 MHz的处理时钟。视频输入端输入分辨率为720×576的PAL视频信号,对其进行缩放处理,放大至1280×1024分辨率,然后存入视频DDR3中。一帧图形绘制结束存入图形DDR3中,叠加输出时将叠加后的视频信号按照1280×1024分辨率对应的DVI视频信号的VESA标准输出到显示器显示,每秒输出60帧画面。图9(a)为绘制的反走样斜线与PAL输入外视频叠加输出画面;图9(b)为绘制的反走样字符与PAL输入外视频叠加输出画面;图9(c)为绘制的标准测试画面与PAL输入的蓝色视频叠加输出画面。

图9 反走样字符图形背景融合画面测试结论

从实际显示画面中可以看出,反走样字符图形经过背景融合后与视频叠加输出边缘光滑,无明显锯齿,显示效果良好;绘制标准画面图9(c)时,对应每秒绘制60帧画面,图形DDR3一帧画面的读写时间约为6.19 ms,占一帧画面实际预留处理时间(1/60=16.7 ms)的37%,表明在一帧时间内,可以绘制更多的字符图形或者绘制更高分辨率输出的字符图形画面;现支持的最大输出分辨率为1920×1080,适用于机载座舱显示系统。

结 语

本文基于机载平视显示系统项目,研究了反走样字符图形与视频叠加时的背景融合算法,并通过FPGA快速实现与验证。增加反走样字符图形背景融合计算,有效解决了反走样字符图形与背景视频叠加后边缘锯齿状明显的缺陷,使两者交接边缘光滑过渡。在FPGA实现时,使用两片DDR3并行存储视频和图形数据,DDR3处理时间缩短为单片DDR3工作时的50%;结合DDR3中断仲裁控制,选择采用先存储再背景融合的方式实现反走样字符图形的背景融合计算,有效地降低了DDR3中断复杂度,优化了系统实现流程,便于硬件开发;绘制标准测试画面时,图形DDR3一帧画面处理时间占预留时间的37%,可以支持更高分辨率的字符图形画面绘制和视频处理。

[1] 王旭东,王新赛,李坚.基于FPGA的视频图像叠加系统的设计与实现[J].电子技术应用,2007,33(11):38-40.

[2] 吴连慧,周建江,夏伟杰,等.基于 FPGA 的机载显示系统架构设计与优化[J].单片机与嵌入式系统应用,2014(8):31-34.

[3] 郑春,周拥军,温永强.大视场光学显示设备图像畸变校正算法[J].电光与控制,2011,18(5):23-27.

[4] 万鹏,杨大伟.基于FPGA的视频叠加融合系统设计与实现[J].电子技术应用,2013,39(9):44-46.

[5] 刘施.基于FPGA的图像视频叠加系统的研究[D].西安:西安电子科技大学,2013.

[6] Wu X.An efficient antialiasing technique[J].Acm Siggraph Computer Graphics,1991,25(4):143-152.

[7] 沈梦杰,周建江,韦小杰,等.基于背景融合的机载字符生成[J].电子技术应用,2015,41(4):25-28.

[8] 张晓燕.基于FPGA的机载视频处理与图形生成系统设计与实现[D].南京:南京航空航天大学,2011.

[9] 吴连慧.机载平显图形生成与视频处理算法研究及其FPGA实现[D].南京:南京航空航天大学,2014.

[10] 张磊.帧速率上变换算法研究[D].上海:上海交通大学,2010.

全颖(硕士研究生),主要研究方向为机载信号处理、数字图像处理及FPGA技术;夏伟杰(副教授),主要研究方向为信号处理;周建江(教授),研究方向为机载电子信息系统。

结 语

参考文献

[1] 阚伟,董群,王东军,等.气固两相流固体质量流量测量技术[J].测量与设备,2007(12):90-92.

[2] 赵会芝.浓相固体流量计在气力输送中的应用[J]. 石油化工自动化, 2010, 46(1):65-66.

[3] 徐苓安.相关流量测量技术[M].天津:天津大学出版社, 1988.

[4] 傅晓林.离散卷积和相关运算的快速傅立叶仿真研究[J],重庆交逋学院学报,2003,22(4).

[5] 罗良玲,胡容华,黄双江,等.互相关技术在动平衡测试中的应用[J].南昌大学学报:工科版,2000,22(4):25-28.

[6] 李良.气固两相流静电相关流速测量研究[D].天津:天津大学,2008.

[7] 郑君里.信号与系统(上册)[M].北京:高等教育出版社,2009:341-342.

[8] 徐文波,田耕.Xilinx FPGA开发使用教程[M].2版.北京:清华大学出版社,2012:16-17.

[9] 加油.为你的USB设备“加把劲”[J].网络与信息,2009,23(9):54-54.

(责任编辑:杨迪娜 收稿日期:2016-06-27)

Anti-aliased Character Graphics Overlay Algorithm and Fast Implementation on FPGA

Quan Ying,Xia Weijie,Zhou Jianjiang

(College of Electronic and Information Engineering,Nanjing University of Aeronautics and Astronautics,Nanjing 211100,China)

In order to improve the display effect of anti-aliased symbol and video superposition in the airborne head-up display system,a kind of anti-aliased symbol and video overlay algorithm is proposed and is realized on FPGA.By adding the background fusion calculation,the adjacent edges of anti-aliased symbol and video is smooth.Two DDR3 are used to store the video and graphic data respectively,both parallel process to improve the overall performance of the system.Optimization of the implementation process of background fusion algorithm,the complexity of the DDR3 interrupt is reduced.The experiment results show that the overall performance of the system is improved,and the overlay fusion image has good effect and high flexibility,which is suitable for the display system of the airborne cockpit.

video superposition;background fusion;anti-aliased;FPGA;DDR3

TP302

A

�士然

2016-06-13)