基于存储器映射的Flash高速低功耗驱动实现

2016-12-03任勇峰李辉景

李 杰,任勇峰,李辉景

(中北大学 电子测试技术国家重点实验室,山西 太原 030051)

基于存储器映射的Flash高速低功耗驱动实现

李 杰,任勇峰,李辉景

(中北大学 电子测试技术国家重点实验室,山西 太原 030051)

针对高速大容量Flash芯片控制中面临的高速可靠性不高与动态功耗大的问题,研究了一种将复杂状态机操作映射到内嵌RAM上运行的方法。通过对内嵌RAM读地址的切换,实现了等延时的状态跳变与输出控制。同时采用加强时钟管理、分割组合逻辑来避免信号不必要的翻转,极大地提高了时序运行的可靠性并降低了其动态功耗。实践表明,该方法实现的 Flash控制时序比传统的状态机在资源消耗和功耗方面均能降低50%以上,为复杂时序逻辑的实现提供了一个新思路。

状态机映射;动态功耗;门控操作;组合逻辑分割

0 引言

在 FPGA对 Flash控制操作中,有限状态机(Finite State Machine,FSM)与多进程描述方式相比有着层次分明、结构清晰、易于修改和移植的明显优势而被广泛应用。传统状态机在描述实现寄存器存储状态信息、组合逻辑产生下一个状态和输出值时,大量使用了FPGA的布线、查找表、寄存器等宝贵资源[1]。

为了实现FPGA的可编程性,在其内部使用了大量的可编程逻辑开关。由于可编程逻辑开关的电阻较金属线大得多,而且引入了大量的寄生电容,从而增加了电路功耗,降低了电路速度[2](研究表明,总动态功耗中62%来自于可编程布线资源)。而且大量组合逻辑容易受到布局布线延迟,在查找表的输出端产生“毛刺”,当系统时钟频率、操作密度大幅提高时,极易引起时序逻辑错误[3]。为此,研究了一种基于存储器映射的有限状态机逻辑实现方法,对FPGA资源进行选择性使用,从而达到降低FPGA功耗、提高运行可靠性的目的。

1 NAND Flash芯片接口及底层驱动实现

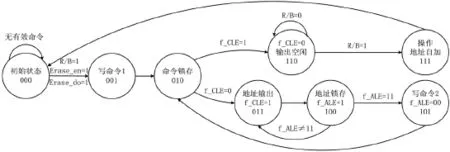

NAND Flash芯片是通过异步高性能 I/O与主控芯片通信的,8位复用总线传输操作指令、操作地址以及数据,多个控制信号来区分总线接口状态以及获取芯片工作状态,如图1。

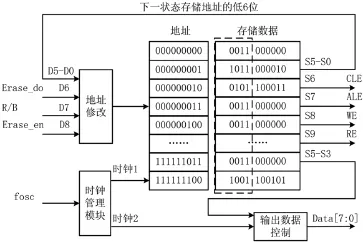

NAND Flash芯片控制器主要完成初始化、无效块检测、块擦除、页编程和页读取共5个基本操作模式。其中初始化操作与无效块校验是在系统上电后需要率先完成的操作,随后控制器将进入到空闲状态,并根据输入的相应控制信号完成剩下的块擦除、页编程和页读取操作。各个操作模式都是状态转移实现一定时序的输出与接收,并且用状态机容易实现。以块擦除为例,其中输入信号有Erase_en、Earse_do和R/B 3个信号,输出信号有CLE、ALE、WE、RE 4个信号,状态转移如图2所示。

图1 Flash控制接口示意图

图2 NAND Flash擦除状态转移图

2 基于存储器映射的有限状态机设计

2.1 基于优化资源配置的低功耗、高可靠设计思路

目前主流的FPGA芯片内部除含有查找表、触发器、布线资源等基本逻辑资源外,还集成了块 RAM、分部式RAM、时钟管理等多种丰富的资源。FPGA的可编程特性主要靠布线结构中的可编程开关连接可编程逻辑块实现。

不同类型资源所消耗的动态功耗在FPGA总功耗中所占比例不同。其中总动态功耗的62%来自于布线资源,19%来自于时钟网络,而可编程逻辑块只占动态功耗的19%[4]。

根据FPGA中各种资源性能、功耗不同的现象,提出了一种新的设计思路,即在满足系统性能的前提下,对FPGA资源进行优化选择性使用,尽可能使用相对较低功耗的资源完成设计任务。将有限状态机映射到FPGA内部RAM中执行,不仅可以减少布线资源的使用,从而降低FPGA的动态功耗,而且能够消除高速状态下切换布线延迟产生的错误或者无效状态[5]。

2.2 基于存储器映射的有限状态机设计方法

状态机组合逻辑都可以抽象为一定输入编码与一定输出编码的对应,即当前状态与输入信号共同决定次态的编码[6]。为了能在块 RAM中执行有限状态机,需要将状态机的编码及状态转移等信息映射到块RAM中。具体方法为:块RAM中每个存储单元内容分为状态机的状态编码信息与状态机的输出信息两部分。由状态机的当前编码信息和状态机的输入信息一起构成下一个状态编码信息的存储地址。

如果采用[D2:D0]表示Flash块擦除状态机的8个操作状态、[D4:D3]表示分3次发送的操作块地址信息、[D5]表示所用的两个操作命令,则操作状态编码、地址编码、命令编码即可唯一确定该状态机当前所处的状态(具体编码方式如图3所示)。其中次态的高4位是状态机向下一状态转化时的输出值,用于对Flash芯片的控制;当前态的高3位是状态机的输入控制信号。采用这种编码方式容易将图2所示的有限状态机表示为当前态与次态对应的真值表见表1。

表1 有限状态机当前态与次态对应的真值表

图3 当前态与次态编码方式

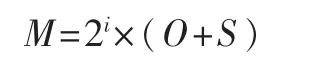

将表1中当前态作为RAM的存储地址,次态作为RAM中存储的数据,即可以将图2所示的有限状态机映射到存储器上执行,如图4所示。状态机进行转化时,下一状态的编码信息存储地址由当前状态的编码信息和状态机的输入信息共同决定。同样,Flash操作中其他的操作模式均可以按这种方式编码并映射为用存储器执行的有限状态机。

图4 有限状态机在RAM上执行示意图

实现有限状态机到存储映射所需要的存储空间最大为:

其中i表示状态机输入的位数,O表示状态机输出的位数,S是状态编码的位数。

当然,当有限状态机越来越复杂时,其所需的存储空间容量越来越大,也可以适当地根据实际情况通过逻辑控制对地址控制进行修正来减小存储空间需求。

3 NAND Flash控制中的低功耗优化设计

FPGA的功耗主要包含静态功耗和动态功耗两部分。静态功耗主要取决于所选FPGA的型号;动态功耗是所有电容性节点充放电产生的组合功耗和电路转换过程中的短路电流形成的功耗[7]。降低FPGA动态功耗的思路为:在保证满足设计要求的情况下,通过降低内部信号的翻转率来降低功耗。其手段包括对时钟进行管理与增加防火墙寄存器。

3.1 基于时钟管理模块的低功耗优化

在FPGA内部时钟信号不断翻转,由时钟信号派生出的信号通常运行在主时钟频率的较小分量[8](通常为12%~15%)。所以在所有高耗能信号中,时钟是主要矛盾。通常情况下,一个状态机会在某个时间段内保持同一个状态不变,但其时钟始终处于翻转状态。因此,关闭闲置模块程序的时钟可以降低时钟资源产生的功耗[9]。在 Flash操作中,当 FPGA处于擦除模式时,初始化操作、无效块校验、页编程和页读取模式均处于闲置状态。图4中时钟管理模块负责对FPGA内部各模块的时钟进行管理,只有该模块处于工作状态时时钟信号才会翻转。在设计中增加时钟管理模块非常简单,可以在硬件描述语言中添加,也可以通过综合工具自动添加。

3.2 增加防火墙寄存器的低功耗优化

在FPGA程序设计中大量组合逻辑很容易受到布局布线延迟在查找表的输出端产生“毛刺”。“毛刺”在后续组合逻辑电路的传播中,可能导致多米诺骨牌效应,致使系统变得不稳定,而且增加了调试难度,消耗了大量的能量。研究表明,由“毛刺”在大量组合逻辑中的传递引起的动态功耗占总动态功耗的10%。用FPGA实现大多数电路功能时,FPGA内部大部分的基本逻辑单元中的触发器(Flip-Flop,FF)没有使用,将这些未用的 FF添加到信号传输路径上被称作增加防火墙寄存器[10](如图5)。通过在程序中添加防火墙寄存器来分割组合逻辑,把每个逻辑功能限制在相邻的逻辑单元中,从而缩短布线长度和减小负载电容,将“毛刺”波的传递限制在最小范围,达到降低功耗的目的。

图5 在程序中添加防火墙寄存器

4 仿真实验结果及分析

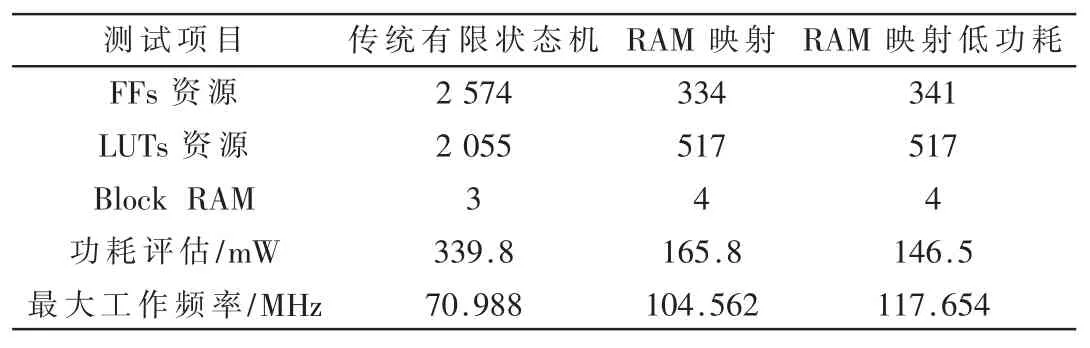

为了比较分析传统状态实现方法与基于RAM映射的有限状态机设计以及低功耗优化方法的性能差别,对设计完成FPGA内部资源消耗情况、功耗评估以及理论最高工作频率3方面进行测试。

整个试验以 Xilinx公司的 Spartan-6系列 FPGA XC6SLX150为目标器件,选用 ISE13.1版本的综合工具,并利用ISE中自带的XPower进行功耗分析。XPower从布局和布线(.ncd)文档中获得 FPGA设计信息,从 Vcd文档中获得设计中所需的时钟、开关活动等信息,该文件可在布局和布线时在Pwr文档中得出功耗报告。仿真结果如表2。

表2 不同时序实现方法下测试结果

从表中可以看出,基于RAM映射的有限状态机设计仅仅增加一个片内Block RAM资源的使用就使内部其他资源占用率下降到传统方式的1/3,总功耗也能下降到原来的50%以下,并且最大工作频率有明显提高。对基于RAM映射的有限状态机进行低功耗优化后仅仅增加了小部分闲置FFs资源的使用,使FPGA总功耗进一步下降到传统状态机设计的43.1%,而且最大工作频率提高了65.6%。

5 结论

文章针对Flash控制应用中实现复杂状态机的设计时存在高速可靠性与动态功耗的问题进行研究,提出了一种优化FPGA内部资源使用方法,利用FPGA内部存储资源构成有限状态机的设计并进行了低功耗优化。其将传统方式下的状态机电路结构中不断变化的状态机寄存器信息转化成RAM中的固定模块,减少了使用功耗较高的布线资源。不仅有效降低了FPGA动态功耗,而且能够消除高速状态下切换布线延迟产生的错误或者无效状态,特别适合大规模的复杂状态机结构,使得各个状态机切换具有等间隔的时间延迟。增加时钟管理模块关闭闲置模块的运行以及添加防火墙寄存器限制“毛刺”传播,进一步降低了 FPGA的动态功耗,提高了系统可靠性。该方法很容易迁移到其他FPGA应用设计中,有较高的实用价值。

[1]马寅,安军社,王连国.基于 Scrubbing的空间 SRAM型FPGA抗单粒子翻转系统设计[J].空间科学学报,2012,32(2):270-276.

[2]SHANG L,KAVIANI A,BALHALA K.Dynamic power consumption in Vinex-I1 FPGA family[C].Proceedings of the 2002 ACM/SIGDA tenth international symposium on Field-programmable gate arrays.2002:157-164.

[3]CROMAR S,LEE J,CHEN D M.FPGA-targeted highlevel binding algorithm for power and area reduction with glitch-estimation[C].Proc of the 46th Annual Design Automation Conference.New York:ACM Press,2009:838-843.

[4]李列文.FPGA低功耗设计相关技术研究[D].长沙:中南大学信息科学与工程学院,2014.

[5]吴强,张逸中.FPGA位流解析及电路还原方法[J].计算机工程,2013,39(5):714-726.

[6]储成群.存储测试系统若干关键技术研究[D].太原:中北大学仪器与电子学院,2015.

[7]李宏钧,胡小龙.流水线的 FPGA低功耗设计[J].计算机系统应用,2011(8):234-237.

[8]WANG Q,GUPTA S,ANDERSON J.Clock power reduction for Virtex-5 FPGAs[C].Proceedings of the ACM/SIGDA international symposium on Field programmable gate arrys. 2009:13-22.

[9]何艳霞,何永泰.FPGA低功耗的设计研究[J].楚雄师范学院学报,2012(6):22-25.

[10]黄娟,杨海钢,谭宜涛,等.防火墙寄存器技术的 FPGA低功耗布线算法研究[J].计算机应用研究,2011(8):2954-2957.

High speed and low power driver realization of Flash based on RAM mapping

Li Jie,Ren Yongfeng,Li Huijing

(National Key Laboratory for Electronic Measurement Technology,North University of China,Taiyuan 030051,China)

Considering the reliability and power consumption problems of FPGA in modern NAND Flash chip controlling,a new design method based on FPGA internal memory mapping for finite state machine(FSM)is proposed.In this way,transfer information and output information will be mapped to internal memory resources of FPGA,by means of controlling the address of memory to implement the state transfer of FSM,and reading data in corresponding memory address to implement state transfer information and corresponding output.The controller clock and combination of the combinational logic to avoid the unnecessary flip of signal greatly improve the reliability of working and reduce the dynamic power consumption.The practice shows that this method can reduce the resource consumption and the power consumption more than 50% of the traditional FSM,which provides a new way in the realization of complex sequential logic.

FSM mapping;dynamic power consumption;controller clock;division of the combinational logic

TP301

A

10.16157/j.issn.0258-7998.2016.03.009

李杰,任勇峰,李辉景.基于存储器映射的 Flash高速低功耗驱动实现[J].电子技术应用,2016,42 (3):31-34.

英文引用格式:Li Jie,Ren Yongfeng,Li Huijing.High speed and low power driver realization of Flash based on RAM mapping[J]. Application of Electronic Technique,2016,42(3):31-34.

2015-08-11)

李杰(1989-),男,硕士研究生,主要研究方向:嵌入式电子电路系统。

任勇峰(1968-),男,教授,博士生导师,主要研究方向:微电路系统、电路系统检测与诊断技术。

李辉景(1982-),男,硕士研究生,主要研究方向:数据采集及存储。