基于FPGA的FLAC音频硬解码的设计与实现

2016-11-30刘乔寿黄国臣吉福生

刘乔寿,黄国臣,吉福生

(重庆邮电大学 光通信与网络重点实验室,重庆 400065)

基于FPGA的FLAC音频硬解码的设计与实现

刘乔寿,黄国臣,吉福生

(重庆邮电大学 光通信与网络重点实验室,重庆 400065)

针对高保真FLAC音频播放系统中软件解码效率低下、占用系统资源大的问题,提出一种基于FPGA的FLAC音频硬解码的设计方案。分析了FLAC音频基本编解码原理,并详细介绍了基于现场可编程门阵列(FPGA)器件的FLAC解码器各模块的设计思想和实现。利用 Verilog语言在Quartus II的开发环境中进行设计输入与仿真验证。实验测试结果表明,该FLAC解码器设计灵活、工作稳定可靠、解码效率高,可作为 IP核应用于不同 SoC的无损音频播放系统中。

FPGA;FLAC;硬解码;IP核

0 引言

FLAC是音频的无损压缩格式,即音频以FALC编码解码后不会丢失任何信息,FLAC音频文件解码还原为WAV文件后,与压缩前的 WAV文件内容是一样的[1]。FLAC是专门针对 PCM音频的特点而设计的压缩方式。现今大多数据系统采用专用芯片或者软件实现FLAC音频的解码。使用专用芯片灵活性差,不利于FLAC解码器的特殊应用。而软件实现解码需要占用大量的系统资源,且解码效率低。

FPGA具有运行速度快、可重复编程、集成度高等优点,是进行原始设计最理想的载体[2]。为此,笔者以音频播放系统中FLAC解码为应用背景,提出了一种采用Verilog语言设计的通用FLAC音频解码器的FPGA模块化解决方案。所设计的解码器可作为IP核用于专用音频集成电路设计或者FPGA设计中,可以缩短设计周期,提高系统设计的成功率。

1 FLAC编码原理及FALC音频格式

与其他的音频编码器类似,FLAC对音频的编码需要经过四阶段:分块、声道去相关、预测编码和残差编码。首先,把未经压缩的音频流划分为块,并进行独立压缩,分块的大小是可变的;然后,对每个分块进行声道去相关操作,去除声道间的冗余信息;之后进入预测器进行预测编码,分块越大,压缩等级越高,就越难以找到高效的压缩模型;最后使用残差编码对预测编码残留下来的残差进行编码,得到最终的音频编码信号。FLAC编码过程如图1所示。

图1 FLAC编码器

图2为FLAC音频文件格式示意图。所有FLAC文件都以四个字节的“fLaC”标志开头。FLAC文件标志之后就是数个元数据块,每个元数据块用来描述特定的音频信息。最后就是音频帧。每个音频帧主要包括了帧同步字、子帧样本数量、采样率、声道分配、样本采样深度、CRC-8校验码以及编码主数据。在FLAC比特流中,所有的数值都是整数,没有浮点运算。所有的数值都采用大端模块,且如果没有特殊说明,所有的数值都是无符号的。

图2 FLAC音频格式示意图

2 FLAC音频解码器的设计

2.1硬件结构设计

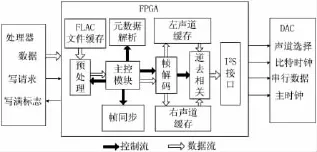

FLAC音频解码器的整体设计框图见图3,其中FLAC音频解码器由以下 9个模块组成:FLAC文件缓存模块、预处理模块、主控模块、元数据处理模块、帧同步模块、帧解码模块、左右声道缓存、逆去相关模块和I2S音频接口模块。其中主控模块控制FLAC解码器运行以及数据的流向。FLAC音频解码器除了有时钟和复位信号外,与处理器连接的还有数据输入端口、写请求信号线和写满信号线。采用I2S音频总线与音频数模转换芯片连接。FLAC音频解码器的各个模块功能将在下面详细介绍。

图3 总体设计框图

2.2FLAC文件缓存模块

FLAC文件缓存模块负责储存处理器传递进来的FLAC数据。如图4所示,FLAC文件缓存模块由两部分组成:FIFO模块和启动信号发生器。这里的 FIFO输入输出宽度为32 bit,深度为1K。FIFO模块的写满标志信号线作为输出外,还作为启动信号发生器的输入信号。为了减少操作的复杂性,此FLAC解码器并不向外部提供专用的启动控制信号线,笔者设计了如下自启动方式:在处理器开始往解码器写入数据时,解码器并没有立即启动相应的模块进行解码。当FLAC文件缓存模块首次缓存满后,启动信号发生器会产生一个有效的启动信号,主控模块检测到启动信号有效才会跳出空闲状态,启动相应的模块开始进行解码。

图4 FLAC文件缓存模块结构图

2.3预处理模块

由于FLAC文件缓存模块输出的数据是并行数据,而内部各个模块每次取数是不定长度的,为了降低取数操作的复杂性,本文设计了预处理模块,负责将并行的码流转换成可取任意位码元的码流。预处理模块为控制模块提供编码器输入FIFO的状态信息,当其他模块读取数据前需要对FIFO空状态进行检测。同时,预处理模块还为帧解码模块提供字节对齐信息。

图5给出了预处理模块结构框图,其主要由两部分组成:边沿检测器和任意位移位寄存器。边沿检测器将检测到的读请求信号电平变化转换为与时钟同步的单脉冲信号,以此作为任意移位寄存器移位控制信号。任意移位寄存器模块的工作机制是根据输入的移位比特数n,在读请求信号的驱动下,将高位的 n比特移出,更新输出。

图5 预处理模块结构框图

2.4控制模块

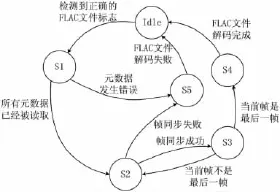

此模块是整个FLAC解码器的核心控制模块,主要功能是检测FLAC文件缓存的储存状态,控制各个模块的运行与停止,并响应模块解码过程中反馈的信息,同时完成将FLAC文件数据传送到相应模块。具体过程如图6所示。在控制器中采用了状态机的设计方式。

图6 控制模块状态机及转移条件示意图

主控模块的状态机状态有:Idle(空闲)、S1(解析元数据)、S2(帧同步)、S3(帧解码)、S4(完成文件解码)、S5(解码失败)。

FLAC文件缓存模块首次储存满时,向主控模块发出Start信号有效,主控模块检测到启动信号有效后会立即从预处理模块获取前4个字节的码流,如果检测到这4个字节是FLAC文件的标志“FlaC”,则会进入S1(元数据解析)状态,并启动元数据解析模块。如果检测到不是有效和FLAC文件标志,则会向外部处理发出文件错误信号。

在解析元数据过程中,如果FLAC元数据存在错误,元数据解析模块会向主控模块发出 S1_Error信号有效,主控模块检测到此S1_Error信号有效后进入S5(解码失败)状态,并最终返回到 Idle(空闲)状态,同时 FLAC解码器向外部处理器发出文件错误信号。如果元数据解析模块成功完成所有元数据的解析工作,则会向主控模块发出S1_Finish信号有效,主控模块检测到 S1_Finish信号有效后会进入 S2(帧同步)状态,启动帧同步模块进行帧同步。

帧同步模块如果同步成功会产生Syn_Frame信号有效,主控模块检测到此有效信号会进入S3(帧解码)状态,并启动帧解码模块开始解码FLAC数据。帧解码模块完成一帧数据的解码会向主控模块发出有效的 Finish信号,主控模块据此会再次进入 S2(帧同步)状态,如此循环,直到完成整个文件的解码。

2.5元数据解析模块

FLAC最多支持128种元数据块,目前只定义了7种。但并不是所有的元数据块都对FALC解码有用,因此本文设计的元数据解析模块只对其中STREAMINFO类型的元数据进行解析,其他类型的元数据块不作解析。所有的FLAC文件都包含STREAMINFO类型的元数据块,此元数据块提供了关于整个FLAC音频流的信息:采样率、声道数量、总采样数等。其中的总采样数参数提供给主控模块,主控模块将此总采样数与当前已经解码的采样数进行比较,以此来判断是否完成整个FLAC的解码。

2.6帧解码

解码是编码的反过程,解码器并不关心FLAC文件的压缩等级,而只需要根据FLAC文件中提供的编码参数进行解码即可。与编码过程相对应,解码同样也依次经过四个阶段:残差解码、预测编码还原、逆去相关、重组。

2.6.1残差解码

信号经过预测编码时,预测器不能非常精确的描述整个信号,因此使用预测模型描述的信号与原始信号是存在差值的。FLAC只采用一种方法(Rice Coding)对残差进行无损编码,残差编码后的数据量远远小于原始数据量。对残差编码值进行解码很简单,本文采用下面的算法对之进行解码。

解码前需要从FLAC码流中提取出相应的残差解码参数:阶数m。假设S为当前FLAC码流,高位在前。首先对S从高位开始计算停止位“1”前“0”的个数为n。再从停止位“1”后面取出g比特的二进制码,用k表示此二进制码所代表的十进制数,再进行如下计算:H=n* (2m)+g。最后根据下面的方法计算最终的解码值X:

(1)如果H是偶数,X=H/2;

(2)如果H是奇数,X=-((H+1)/2)。

至此,残差解码已经完成,解码得到的X需要输送到预测编码还原模块。需要指出的是,FLAC的残差解码采用四种预测模型:原样模型、常量模型、固定的线性预测模型和FIR线性预测模型。而只有采用后两种预测模型的编码才会产生残差,前两种预测模型只在预测编码还原阶段进行解码还原。

2.6.2预测编码还原

如前文所述,FLAC有四种预测编码模型,对使用原样模块和常量模型编码的信号进行还原比较简单。如果是原样模型,只需要根据帧头部的编码个数L和原样模型中编码长度n从FLAC码流中直接提取L个长度为n编码值即可。对于常量模型,需要从FLAC码流中提取出一常量值,依次输出L个此常量值即可。

对使用固定线性预测模型编码得到的信号,还原信号等于预测值加上残差值。预测值根据前n个训练样本通过固定的预测算法计算得到。

对使用FIR线性预测模型编码得到信号,计算过程稍微复杂些。在编码时为了避免小数乘法运行,需要将实数型的预测因子都扩大2n倍,舍去小数,同样也需要将原始信号扩大2n倍。因此解码时使用扩大了的预测因子和训练样本还原得到的信号需要缩小2n倍,再与所对应的残差相加得到还原信号。

2.7逆去相关模块

在立体声音频流中,左右声道之间的相关性导致存在大量的冗余信息。FLAC有多种去除声道相关性的方法。对一帧中,编码器会选择效果最优的一种方法去除声道相关性。

(1)独立编码。左右声道分别独立编码,不做去相关性处理。

(2)中边编码。通过对左右声道信号进行运算产生中值声道和边值声道。而且规定中值声道是左右声道信号的均值,边值声道都是左声道减右声道得到的。

(3)左边编码。被编码成独立的左声道和差值声道。

(4)右边编码。被编码成独立的右声道和差值声道。逆去相关模块内部结构如图7所示。

逆去相关模块主要由相关性还原模块、声道配置队列模块、采样数队列模块和减法计数器等组成。由于左右声道缓存中可能存在数帧,因此需要声道配置队列模块和采样数队列模块将左右声道缓存中各个帧的声道配置信息和采样数缓存起来,采用减法计数器计算缓存中当前剩余采样数,当计数器计数到“0”时,会从采样数队列模块中获取下一帧的采样数并预装计数初值,同时声道配置队列模块的输出也更新到下一帧的声道配置信息。相关性还原模块根据新的声道配置信息对新一帧的左右声道数据进行相关性还原。

图7 逆去相关模块结构图

2.8I2S音频接口

I2S有 3个主要信号:(1)比特时钟 BCLK,即对应数字音频的每一位数据,BCLK都有一个脉冲。BCLK的频率=2×采样频率×采样位数;(2)帧时钟 LRCK,用于切换左右声道的数据。LRCK的频率等于采样频率;(3)串行数据SDATA,就是用二进制补码表示的音频数据。有时为了使系统间能更好地同步,还需要另外传输一个信号MCLK,称为主时钟[3]。

为了解决音源采样率的问题,实现对 44.1 kHz和48 kHz音频的精确采样,本设计采用了双晶振方案。22.579 2 MHz晶振用于 44.1/88.2 kHz的音源采样率,24.576 MHz用于48/96/192 kHz的音源采样率。

本文设计的I2S音频接口模块由两部分组成:分频模块和并串转换模块,如图8所示。分频模块根据外部输入的采样率选择22.579 2 MHz或者24.576 MHz作为输入时钟,并分频出 I2S的3个时钟信号。同时分频出的BCLK也作为并串转换模块的时钟,并串转换模块将DATA信号总线上的数据以串行方式输出。

图8 I2S音频接口模块结构图

3 系统仿真及分析

系统在Quartus II 12.0中进行设计、综合仿真,并将设计下载到DE2-115开发板的Cyclone IV EP4CE115F29C7N上。为了验证设计的正确性,通过modelsim工具对FLAC解码器的工作状况进行仿真验证。笔者编写了test_bench文件读取计算机中的音频文件输入到 FLAC解码器中。图9为解码器解码输出时序。从图中可看出,FLAC解码器能实现正确解码,且I2S音频接口模块各种信号完全满足时序要求。

图9 仿真结果时序图

4 总结

为了解决高保真FLAC音频播放系统中软件解码效率低下、占用系统资源大的问题,本文提出了一种基于FPGA的 FLAC音频硬解码的设计方案。本设计采用Verilog语言,在 ALTERA公司的 FPGA(Cyclone IV EP4-CE115F29C7N)芯片上成功实现了对 FLAC音频文件的解码。利用FPGA实现FLAC音频的解码器可以作为IP核应用于不同的SoC音频播放系统中,有助于缩短产品的开发周期。

[1]COALSON J.Flac-free lossless audio codec[EB/OL].(2014-12-27)[2015-5-2].http://xiph.org/flac/index.html.

[2]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003.

[3]张景璐,周金和,朱恭生,等.IIS接口的 FPGA实现[J].电子技术应用,2007(6).

Design and implementation of FLAC hardware decoding based on FPGA

Liu Qiaoshou,Huang Guochen,Ji Fusheng

(Optical Communication and Network Key Laboratory,Chongqing University of Posts and Telecommunications,Chongqing 400065,China)

In Hi-Fi FLAC audio player system,software decoding efficiency is low,and also occupy a large number of system resources.To solve these problems,a design scheme of FLAC audio hard decoding based on FPGA is proposed.This paper analyze the basic principles of audio coding and decoding,and introduced the design idea and implementation of FLAC decoder based on field programmable gate array(FPGA)device in detail.Verylog language be used to design and simulation verification in Quartus II. The experimental results show that the FLAC decoder is flexible,stable and reliable,and can be used as the IP core to be used in the SoC system.

FPGA;FLAC;hard decoding;IP core

TP331.2

A

10.16157/j.issn.0258-7998.2016.02.005

2015-07-29)

刘乔寿(1979-),男,副教授,博士研究生,主要研究方向:无线泛在网络,物联网等。

黄国臣(1989-),男,硕士研究生,主要研究方向:多媒体信息处理与传输。

吉福生(1982-),男,高级工程师,硕士研究生,主要研究方向:网络管理及无线网络核心技术等。

中文引用格式:刘乔寿,黄国臣,吉福生.基于 FPGA的 FLAC音频硬解码的设计与实现[J].电子技术应用,2016,42 (2):21-24.

英文引用格式:Liu Qiaoshou,Huang Guochen,Ji Fusheng.Design and implementation of FLAC hardware decoding based on FPGA[J].Application of Electronic Technique,2016,42(2):21-24.