基于FPGA的列车网络接口单元设计

2016-11-09田地杨伟

田地 杨伟

摘要:针对西安地铁2号线辅助变流器与车辆网络通信问题,设计了一种基于FPGA的HDLC通讯协议接口。硬件部分包括spantan3系FPGA和RS485电路,软件部分介绍了使用Verilog HDL语言实现了HDLC协议控制时序的方法,利用FPGA内部生成RAM实现车辆设备与列车网络之间的数据交换。最终进行装车调试,结果表明,通信可靠稳定,达到设计要求。

关键词:列车网络 FPGA HDLC

中图分类号:TN919 文献标识码:A 文章编号:1007-9416(2016)09-0188-01

地铁车辆在运行过程中,车辆的制动、空调运行模式等信号会通过车辆网络(ATI)实时传输给相应车辆设备,相应的车辆设备也会实时将运行状态,故障数据等上传至车辆网络。高级数据链路控制(HDLC)协议,其具有通信速率高、数据传输可靠等优点,广泛应用工业现场总通信领域。利用FPGA实现HDLC协议,开发周期短,易于移植,灵活性强。

1 HDLC协议

HDLC是一个面向比特的数据链路层协议。在HDLC协议中,数据被组成一个个单元(称为帧)通过网络发送,并有接受方确认接收,HDLC协议也管理数据流和数据发送的间隔时间,帧中包含了控制和响应命令。HDLC支持全双工传输,在同一时刻,数据在两个方向上传输,形成了较高的吞吐率。HDLC适合点对点和点对多点连接。

2 系统硬件

FPGA采用硬件处理技术,可以反复编程,能兼顾速度和灵活性,并能并行处理多路信号,实时性能够预测和仿真。因此,使用FPGA实现HDLC协议是一种合适的选择。

列车运行环境中,常会有电气噪声干扰传输线路,且列车通信节点多,位置分散,通讯距离远,而RS-485接口采用平衡驱动器和差分接收器的组合,抗共模干扰能力增强,即抗噪声干扰性好,传输节点多,传输距离远,因此物理层选用RS485传输。

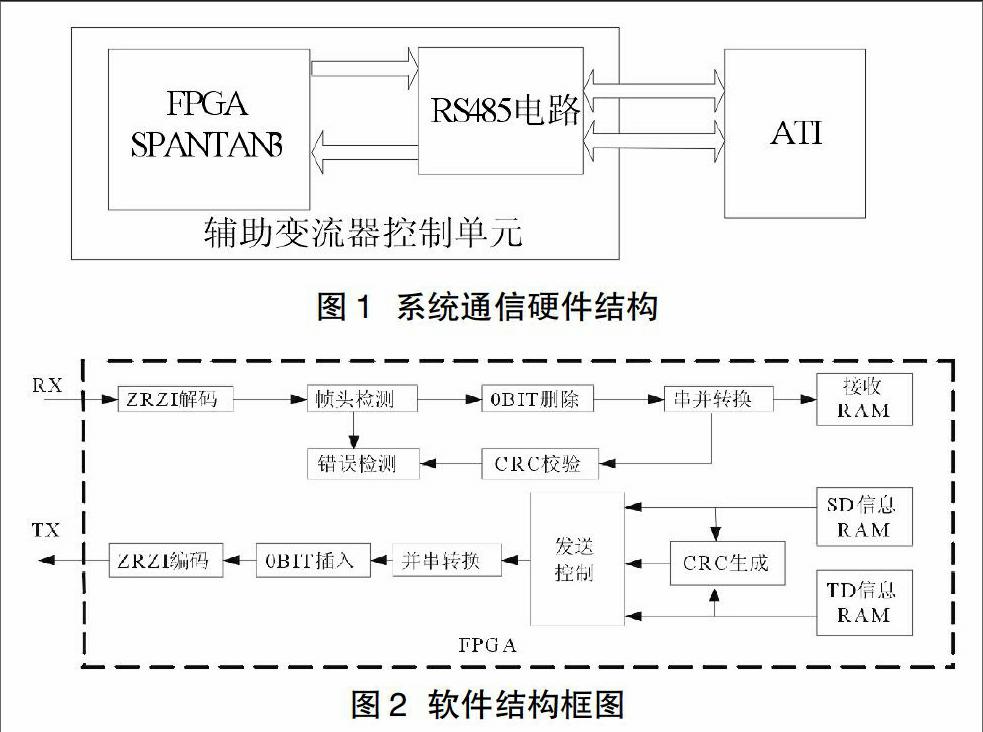

系统相关硬件结构如图1所示,主控芯片采用XILINX公司的SPANTAN3系FPGA,通过电平转换电路、RS485电路与列车网络相连接,完成数据的交换。

3 FPGA软件设计

由于本项目中通讯编码方式为NRZI编码,故FPGA需要完成数据的编码与解码、数据的接收发送、CRC校验、传输错误检测等功能。

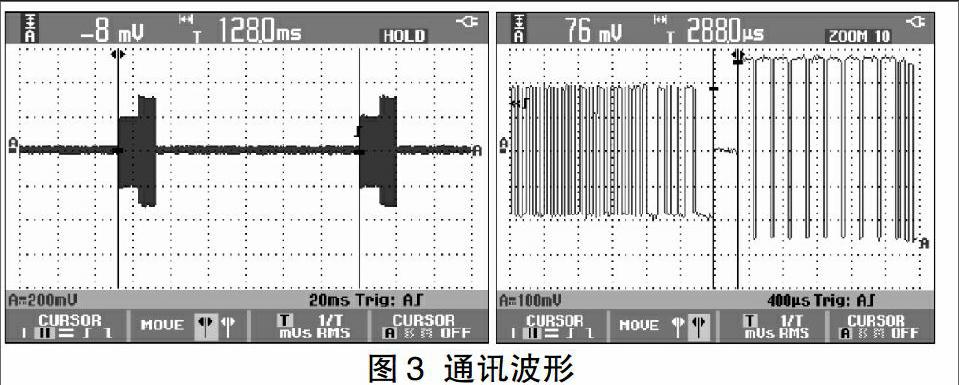

软件主要通过以下模块完成上述功能:NRZI解码与编码模块、0BIT删除与插入模块、CRC校验模块、串并转换模块、并串转换模块、接收RAM与发送RAM、传输错误检测模块、发送控制模块。具体如图3所示。

3.1 NRZI解码与编码模块

一般的串行通信总线信号的同步性存在问题,而NRZI(不归零反向编码)编码方式,不需要额外增加时钟信号线,解决了通信双方信号同步的问题。本模块完成串行数据输入的解码与数据输出的编码。

3.2 帧头检测模块

本项目中HDLC协议规定连续2到15个7E视为一帧数据的开始故在接收数据时检测到帧头后才能提取数据。具体的做法为检测到串行数据中出现7E后,持续检测,当出现数据不为7E时开始使能下一级处理模块,进行0BIT删除、串并转换、CRC校验等操作;如图2所示。

3.3 0BIT删除与插入模块

为了保证标志字的独立性,避免在接受数据中接收到7E(01111110)发送方在发送信息过程中,遇到连续5个1将自动插入一位0,相反,接收方在接收数据时将连续5个1后的0位删除。保证HDLC协议传输的正确性。

3.4 串并转换模块与并串模块

接收过程中经过0BIT删除后的串行信号是包含真实数据的串行信号,根据传输的波特率将串行数据转换为单字节数据,发送过程中将单字节数据组进行组帧,再依照传输波特率按位依次串行发送,经过0BIT插入、NRZI编码模块完成数据发送。

3.5 接受RAM与发送RAM

在接收时,将串并转换过后的数据依次存入接收RAM供后极模块使用,发送时将设备的状态量等需要上传至列车网络的数据存入发送RAM再经过并串转换模块、0BIT插入、数据发送模块、NRZI编码模块依次发送至列车网络。

3.6 CRC校验模块

为了保证传输过正中数据的正确性,需要对除标志外的帧数据进行校验,HDLC协议中采用16位循环校验码进行差错控制。

3.7 发送控制模块

列车网络向辅助变流器发送的数据信息包括:SDR信息(一般监视数据)和TDR信息(故障追踪数据),发送模块根据接收到信息第一个有用字节区分信息类型(20H代表SDR信息,21H代表TDR信息),并将相应的SD信息(一般监视数据)或TD信息(故障追踪数据)通过发送模块上传至列车网络。

3.8 错误检测模块

通讯过程中检测CRC校验错误、超时错误、帧长错误,做相应的记录与告警。

4 结果验证

本项已经应用于西安地铁2号线增购车辅助变流器单元中,运行稳定良好,采集波形如图3所示。当列车网络发出SDR信息或者TDR信息后,设备会回复相应的SD信息或TD信息,响应速度为288us。经过长时间通信测试,通信状态稳定,相应及时,达到设计要求。

5 结语

本文以西安地铁2号线辅助变流器自主化项目为依托,设计了基于FPGA的HDLC通信接口方案,阐述了该方案优势,并给出了FPGA通信模块的详细设计过程。经过装车运行,通信数据正确、稳定、响应速度快。验证了该方案的正确性,达到设计要求。

参考文献

[1]李宁.一种动车组用HDLC总线装置的研制与应用[J].计算机光盘软件与应用,2014(22).

[2]刘志清.HDLC通道汇聚器设计与验证[D].西安电子科技大学,2009.

[3]田耕等著.Xilinx ISE Design Suit10.xFPGA开发指南[M].人民邮电出版社,2008.