三值光学计算机解码器中并行感光阵列的设计

2016-10-20石也强金翊欧阳山展豪君

石也强,金翊,欧阳山,展豪君

(上海大学计算机工程与科学学院,上海 200444)

三值光学计算机解码器中并行感光阵列的设计

石也强,金翊,欧阳山,展豪君

(上海大学计算机工程与科学学院,上海 200444)

介绍了针对数千位的三值光学计算机解码器而设计的一款并行感光阵列。在整体规划上,采用了将16个感光单元电路集成为一个感光模块,再用多个感光模块拼接成实用的并行感光阵列之策略.设计的感光单元电路将三值光学处理器一个像素输出的光信号转换成对应的电信号,一个感光模块将三值光学处理器16个像素输出的光信号并行转换成对应的电信号,感光阵列将三值光学处理器的数千个像素输出的光信号并行转换成对应的电信号.设计的感光模块封装外形解决了拼装成大规模感光阵列的问题.该模块为三值光学计算机提供了一个成本低、方便维护及更换的并行光电器件.最后介绍了对感光模块中电路的实验研究和对模块外形拼接性能的实物样板测试,实验证实了所设计电路的功能有效性和性能稳定性,样板测试表明该设计的感光模块封装外形适于拼接.

光电转换;并行感光阵列;三值光学计算机;模块设计

随着可重构三值光学处理器在理论和实验上的成功[1-6],研制实用的三值光学计算机成为该领域的一个关注点[7-8],于是对这种新型计算机各部件的探索正在逐步从其工作原理和构造原理的研究转向精密设计方面的研究,即通过对部件的精密设计来提高整机性能并达到实际可用的水平.在这个背景下,2004—2013年金翊等[9-15]对三值光学计算机的光电信号转换部件——解码器的感光阵列进行了全新设计,即以三值光学计算机前期实验系统中建立的解码器理论和技术为基础,在延续了原技术中的电路、感光原理以及液晶结构的基础上,针对构建全并行解码器这一目标,对现有的技术进行了重大改进.

在三值光学计算机的研究过程中,以往的工作重心都集中在计算功能的实现上[7-8,16-21],面对整机性能的追求才刚刚开始,因此其解码器的光电转换部件至今仍将手机摄像头用作替代品.然而,摄像头的工作速度以满足视觉为目标,鉴于视觉要求的帧频远远低于图像传感器处理一帧图像数据的速度,故摄像头都采用行扫描工作方式,即摄像头都采用对图像像素依次处理的串行技术.但是,光学计算机要求对图像的所有像素同时进行处理,故用作替代品的摄像头严重影响了三值光学计算机的整机性能.目前在国内外对并行光电转换阵列的研究比较少[22-24],少量成品的价格比较昂贵,而且封装外形完全不适合在三值光学解码器中使用,为此从科学研究、经济效益和封装外形等方面考虑,研究用于三值光学计算机解码器的并行光电转换器件很有必要.针对这一需求,本研究提出了一种适用于三值光学计算机解码器的并行感光阵列,包括设计了该并行感光阵列的工作电路、单元芯片的集成规模、单元芯片的封装外形、单元芯片的内部电路、单元芯片的外部引脚配置、用单元芯片拼装成大规模并行感光阵列等.本研究通过必要的实验证实了所设计的并行感光阵列的有效性和适用性,并报道了这项研究的核心内容和实验情况.

1 并行感光阵列的设计要点

1.1 设计方案的选择

本设计的总体目标是研发全部像素并行工作的、易维护且造价低的感光阵列.

为达到这个目标,最直观的设计方案是制作一整块与液晶板大小相同的感光阵列.以三值光学计算机实验系统使用的液晶板为例,需要制作一块24×24大小的阵列.该方案虽能达到全部像素并行工作的目的,但一个器件中包含很多相同的单元电路,这存在3个问题:①成品的需要量很小,导致成本很高;②单个阵列中包含的像素越多,单像素损坏的概率就越高,而单像素损坏就会导致整个阵列不可用,于是成品的损坏率就很高,这进一步提高了成本;③使用过程中有一个像素点损坏就需要更换整个阵列,当更换了整个感光阵列后,系统的每个像素都需要重新设定工作电压,从而使系统维护相当困难.故这个方案是不可行的.

第二种方案是将每一个感光电路制作成一个芯片,即每个芯片仅包含一个感光像素.显然,对这种小芯片的需求量会很大,每个小芯片的成本就会比较低,而且一个感光像素损坏时只需更换一个小芯片,对其他像素没有产生影响,便于维护.但是,小芯片的体积很小,对制作工艺的精度要求较高,而且制作一块24×24大小的阵列就需将576个小芯片拼接起来,导致拼接大感光阵列很难.因此这个方案也不可行.

第三种设计方案是取前两种设计方案中的合理部分,综合考虑电路制作的难易、感光阵列的成本、拼接的可实现性和维护难度等因素,构造包含多个感光像素的单元芯片,并使单元芯片的体积和外形便于拼接.这样的单元芯片有便于制作、成本较低、方便拼接、易于维护等优点.鉴于此,本研究选择了这个方案.

在第三种设计方案的指导下,本研究选定一个单元芯片中包含4×4个感光像素.主要原因有以下3个方面:①为方便模块的拼接与扩充,将模块的形状设计为方阵;②为了便于利用现有的常规器件,如四运算放大器LM324、16位锁存器,故方阵的阶数最好为2的幂数;③综合考虑阵列的几何尺寸大小、目标像素的大小以及模块加工制作的难易程度、拼接成大感光阵列的方便性和维护的简便性.

1.2 关键技术

为制作合适的感光模块,必须解决的关键技术如下.

(1)当被测图像上任一个像素的亮度超过亮阈值时,对应感光单元输出确定的高电平值;而当被测图像任一个像素的亮度低于暗阈值时,对应感光单元输出确定的低电平值.

(2)感光阵列的所有感光单元同时曝光,同时输出探测电平.

(3)制作包含适当数量感光单元的并行感光模块,并用这种感光模块拼接成大规模的感光阵列.

如果能解决关键技术(1),则允许三值光学处理器输出光信号的亮度在一个较大的范围内变化,于是就降低了对光学处理器输出图像的亮度均匀性要求,进而降低了对光源稳定性的要求;也降低了对液晶旋光角度的精准性要求,进而降低了对液晶控制电路的精度要求.这就使得三值光学计算机整机更容易达到稳定的工作状态,且降低制造精度和研发成本.

解决这个问题的设计要点是:用一个感光管、一个运算放大器(以下简称运放)和一位锁存器构成一个感光单元.在感光单元中,感光管的输出端接运算放大器的输入端,运放的输出端接锁存器的输入端,锁存器的输出端为该感光单元的输出信号.在这个设计中,感光管用来探测光学处理器中一个像素的光亮度,运放将感光管的输出放大到足以推动锁存器输入端的电平,而锁存器对运放的输出电平进行整形,使该感光单元的输出电平符合TTL电平规范.

关键技术(2)是针对并行感光阵列的基本要求,解决这个问题的设计要点是:将所有感光单元中锁存器的锁存有效端并接在一起,用一个信号控制所有感光单元同时探测光学处理器各像素的输出光强;并将所有感光单元中锁存器的输出有效端并接在一起,用一个信号控制所有感光单元同时输出探测电平.

关键技术(3)的作用有3点:①制作数量较多的小感光模块比制作一个大感光阵列的成本低很多;②用小感光模块可以拼接成长宽尺寸不同的多种并行感光阵列,以适应三值光学处理器使用不同规格的液晶阵列;③当感光阵列局部损坏时,只需调换损坏的几个感光模块即可修复整个感光阵列,从而延长系统的寿命,降低维护成本.

解决这个问题的设计要点是:将16个感光单元排成4×4方阵构成一个感光模块,这16个感光单元的一位锁存器合并成一个16位锁存器;该模块的一面均匀排列4×4个感光管,另一面排列24根电接触针,其中16根为16位锁存器数据的输出针,一根为锁存信号,一根为输出有效信号,两根电源,两根地线,两根未用(计划用于防止插座接反);该模块的4个侧面为燕尾形互接齿,以方便拼接成感光阵列时感光模块间相互啮合.

2 并行感光阵列的详细设计

2.1 电路设计

(1)感光单元设计.

本研究采用的CMOS型感光管是一种光控三极管,当其光控端接收到光照时,它的PN结电阻减小,借此实现光照信号强度对PN结上电信号强度的控制.但光电管允许通过的电流强度在微安量级,通常用运放电路将这个弱信号放大到可以被后续电路识别的程度,本研究也采用这一设计思想,具体电路设计如图1所示.图1中感光管为CMOS型光电三极管,运放采用负反馈反向比例放大电路,锁存器为一位D触发器.本研究用G、L和D分别表示感光管和锁存器.

图1的工作原理可以简述为照射到感光管上的光信号越亮,感光管的导通性就越好,则运放两个输入端的信号差就越大,运放的输出电压就越高,当光照强度超过一个较高的亮度时,运放输出电压就会超过3.5V,这时对于锁存器的输入端就是高电平状态,锁存器就存储“1”值;而当光照强度低于一个较低的阈值时,运放输出电压就会远低于3.5V,这时锁存器的输入端处于低电平状态,它就存储“0”值.用这个电路去探测光学处理器一个像素的输出光强,当该像素输出亮信号时,锁存器中就存储到“1”值,而当该像素输出暗信号时,锁存器中就存储到“0”值.于是图1的电路将光学处理器一个像素的输出光信号转换成一位的电信号,故本研究称它为感光单元电路.

图1的工作时序由锁存器的锁存有效端LE和输出有效端OE控制,当给LE施加有效信号时,锁存器将运放的当前输出值保存在锁存器中,即完成探测光强的操作,当给OE施加有效信号时,锁存器将保存的值输出.于是外界通过适时给LE和OE施加有效信号,控制感光单元的操作时序.另外,锁存器输出标准的TTL电平,这意味着对运放的输出信号进行了整形,于是只要照射感光管的光强度超过较大阈值[25-26],即使光强有波动也不会影响感光单元电路输出“1”;同理,暗光状态有波动也不会影响感光单元电路输出“0”,因此这个电路对光学处理器输出光信号强度的容错能力较高.

图1 感光单元电路Fig.1 Photoreceptor cell circuit

(2)感光模块设计.

图1给出的感光单元电路能够探测光学处理器的一个像素输出的光信号,对于有数百万个像素并行工作的光学处理器[27-28],每个像素都需要一个感光单元电路,这数百万个感光单元电路将按照光学处理器像素的排列方式组成感光阵列.由于光学处理器的像素面积很小,这些感光单元电路必须采用集成化制造技术构成一个与光学处理器对应的大规模集成感光阵列,本研究就是为构建这种大规模集成感光阵列奠定技术和结构研究的基础.因此,必须考虑用尽量低的代价来验证用图1给出的感光单元电路排成的感光阵列的功能有效性和制造的可行性.为达到这一目标,考虑在此期间三值光学处理器还保持着较大的像素面积以方便人眼直接观察,本研究采取用较少的感光单元构成一个小规模集成度的感光模块,再用许多感光模块拼接成感光阵列之策略.由于感光模块的集成度较小,其研发成本和风险比研发感光阵列低很多;由于需要的数量较多,每个感光模块的制作成本就比较低;由于感光阵列用很多感光模块拼接而成,当感光阵列局部损坏时,只需更换个别感光模块即可,从而降低了实验研究的成本和系统维护成本,因此这个策略满足本研究的需要.

鉴于目前三值光学处理器一个像素的尺寸为3.98 mm×3.28 mm[29],本设计的感光模块包含排成4×4方阵的16个感光单元电路,图2给出了感光模块的内部电路图.为了进一步减小感光模块的集成度,也为了能对运放输出电平进行更细致的研究和利用,图2中将16个感光单元的一位锁存器集中在一个16位的常规锁存器中,并将该存储器设置在感光模块之外,于是这个锁存器可以使用常规芯片,进一步降低研究成本.由于16个感光单元的一位锁存器集中在一个锁存芯片中,它们的OE端在锁存芯片内连在一起,LE端也连在一起,于是16个感光单元的操作时序完全同步.

图2 感光模块电路Fig.2 Photoreceptor module circuit

在使用中,每个感光模块都将被贴附在三值光学处理器的输出画面上,每一个感光管正好对正光学处理器的一个像素.于是,每个感光模块并行探测光学处理器16个像素的光强度并同时输出探测结果,整个感光阵列就同时探测光学处理器每个像素输出的光信息,并同时输出探测结果,成为实现三值光学计算机并行解码器的基本器件.

2.2 感光模块的封装设计

用多个模块拼接成实用的感光阵列的设计思想可以有效降低研发成本、制作成本和维护成本.但模块的几何尺寸应既方便模块电路和引脚的配置,又便于每个感光单元对正光学处理器的一个像素,而模块的外形也应既方便相互拼接,又便于相互啮合,避免松散,为此本研究详细设计了感光模块的封装.

(1)感光模块尺寸.

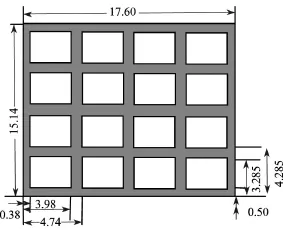

设计感光模块外形的最大几何尺寸为长17.60 mm、宽15.14 mm,高度由芯片制作工艺确定(见图3).

设计感光模块的正面为光线射入面,要求镜面平整且透光性好,各部分的具体尺寸如图3所示.图3中的白色部分对应于光学处理器输出面上的像素面积,灰色部分对应于光学处理器输出面上像素之间的隔光带,每一个白色区域的中部安置一个感光单元的光电管,为提高感光管的可靠性,在每个白色区域中安放并联的3个感光管,只要有一个感光管能正确感知光学处理器像素的输出光强,该感光单元即可正常工作.为充分降低相邻液晶点对感光阵列的影响,液晶像素的隔光带必须正对感光模块中感光管之间的间隔,并且制作时尽量将感光管集中在图3中白色区域中心,以增大隔光带的尺寸,降低相邻液晶点的相互影响.

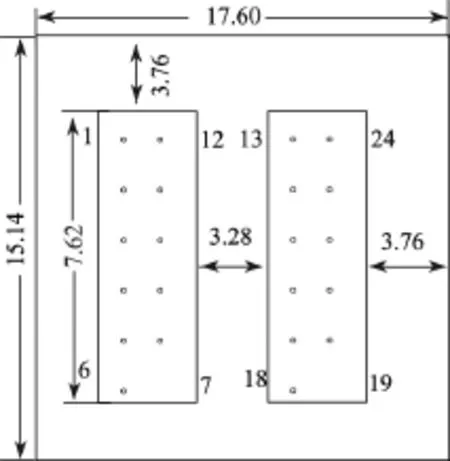

设计感光模块的背面安装垂直插针,用于电连接.参考派睿公司M50-3500622型号的排针规格,设计感光模块安装两个相同的双排直针A和B,它们在感光模块上的定位参数如图4所示.排针的几何参数为针距1.27mm、行距1.27mm,针直径为0.50mm,电器参数为额定电流1A、绝缘电压为500V,环境温度:[-40,105]◦C.

图3 感光阵列模块尺寸大小(mm)Fig.3 Photoreceptor array module size(mm)

(2)模块电接触引脚设计.

感光模块共有24根插针,各针的编号如图4所示,各针的功能定义如表1所示,其中O1~O16是16个感光单元输出的电信号,在本设计中为各个运放输出的电平.第7号和第19号引脚没有定义,要求对应的插座上的这两个位置为空,以防止插反.

图4 感光阵列模块引脚设计(mm)Fig.4 Photoreceptor array module pin design(mm)

表1 感光阵列模块引脚功能定义Table 1 Pin function definition of photoreceptor array module

(3)模块外形设计.

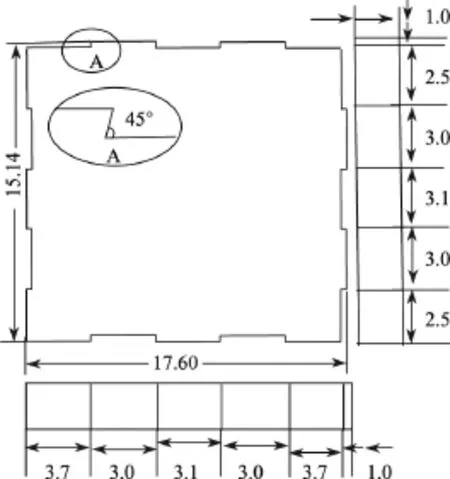

为方便将感光模块拼接成感光阵列,在感光模块的4个侧面设计了燕尾形互接齿,具体形状和尺寸如图5所示.

图5 感光阵列模块封装外形三视图(mm)Fig.5 Photoreceptor array module encapsulation shape(mm)

3 实验

3.1 电路原理实验

3.1.1 实验环境搭建

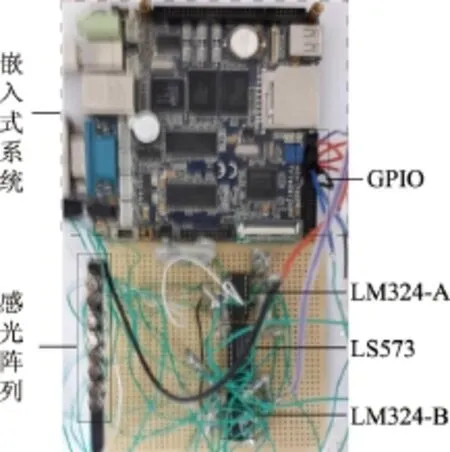

图6中的实验电路板上焊装有8个如图1所示的感光单元电路,其中感光管采用与感光单元中感光材料质地和结构均相同的CMOS管,以真实验证感光单元的工作情况;各电阻的值分别为R1=200Ω,反馈电阻Rf=50 MΩ,平衡电阻R2=3 kΩ;8个运算放大器采用两个LM324芯片来实现,记为LM324-A和LM324-B,每片集成了4个运算放大器,每个运放负责放大一个感光管的输出信号;8个一位锁存器采用一片LS573来实现,LS573中集成了8位锁存器;还焊装了一个12针插口,用于连接嵌入式系统.实验电路板上各元件的主要连线如图7所示.

在图7所示的连接中,锁存器LS573的输出有效端OE通过H12的8号引脚与嵌入式系统的GPB1相连,于是当嵌入式系统在GPB1输出低电平时,控制LS573输出锁存值,即控制锁存器输出的嵌入式系统指令为rGPBCON=0x10,rGPBDAT=0x01;同理,LS573的锁存有效端LE通过H12的9号引脚与嵌入式系统的GPB2相连,于是当嵌入式系统在GPB2输出低电平时,控制LS573锁存输入值,即控制锁存的嵌入式系统指令为rGPBCON=0x04,rGPBDAT=0x03.在这个连接下,通过PC机的ADS开发环境向嵌入式系统发出的实验命令由一个锁存命令和经过延时t后的一个锁存器输出指令组成:rGPBCON=0x10,rGPBDAT=0x03,delay(100),rGPBCON=0x04,rGPBDAT=0x01.

图6 感光阵列(8位)实验照片Fig.6 Photoreceptor array(8 bits)experiment device photo

3.1.2 实验过程

为了能够全面地测试与验证并行感光阵列的功能,本设计的实验步骤如下.

(1)用散射光照亮8个感光管,使0号感光单元的运放输出电平达3.5V(使用DT-9205A型号数字万用表测量);发出实验命令;在PC上保存收到的锁存器输出值.理论值为FF.

(2)遮挡对8个感光管的光照;发出实验命令;在PC上保存收到的锁存器输出值.理论值为00.

(3)遮挡对1、3、5、7号感光管的光照;发出实验命令;在PC上保存收到的锁存器输出值.理论值为55.

女人很漂亮,约莫二十岁出头,高挑的个头,瓷白的皮肤。一条曵地的白色纱裙像一朵盛开的白色蔷薇朝下铺陈开放着。

(4)遮挡对0、2、4、6号感光管的光照;发出实验命令;在PC上保存收到的锁存器输出值.理论值为AA.

(5)降低散射光亮度,使0号感光单元的运放输出电平约3.0V;执行实验步骤(1)~(4).

(6)降低散射光亮度,使0号感光单元的运放输出电平约2.5V;执行实验步骤(1)~(4).

(7)降低散射光亮度,使0号感光单元的运放输出电平约2.0V;执行实验步骤(1)~(4).

(8)根据上述实验情况,调整散射光亮度,重复实验步骤(1)~(4),找到能正确测定光信号的光强度值所对应的0号感光单元的运放输出电平.

(9)根据步骤(8)的实验结果定出光亮度的高阈值,执行实验步骤(1)~(4),重复10遍,每次重复间隔2min.

(10)根据步骤(8)的实验结果定出光亮度的低阈值,执行实验步骤(1)~(4),重复10遍,每次重复间隔2min.

3.1.3 实验数据及分析

步骤(1)的目的是为了判断感光阵列能否正确地探测到光强度的亮状态;步骤(2)是为了判断感光阵列能否正确地探测到光强度的暗状态;步骤(3)和(4)是为了判断液晶相邻像素的亮暗信息是否影响感光阵列的工作;步骤(5)~(8)的设计目的是为了找出感光阵列的亮暗阈值;步骤(9)是为了验证感光阵列的亮阈值是否正确;步骤(10)是为了验证感光阵列的暗阈值是否正确.

根据光电转换原理,目标像素的光强度用0号感光单元的运放输出电压表示.这里由于篇幅所限,表2中只列出了上述实验过程中步骤(1)和(3)的实验数据.步骤(2)的实验数据全部为0,步骤(4)和步骤(3)相似,略.

图7 感光阵列(8位)实验图Fig.7 Photoreceptor array(8 bits)experimental schematic diagram

表2 实验数据Table 2 Experimental data

分析实验数据可知,在0号感光单元的输出电压值为[0,1]V之间,不管是否用黑色物质挡住感光阵列,测试单元的输出电信号的值均为0,与理论值一致;0号感光单元的输出电压值在[2.0,3.5]V之间时,如果感光管被黑色的不透光物体遮挡住,测试单元输出的电信号为0,否则为1,与理论值一致;当0号感光单元的输出电压值在[1,2]V时,测试单元输出的电信号有时为1,有时为0,光电转换的结果是不稳定的,该区间对应的光强度介于暗阈值与亮阈值之间.

3.1.4 实验结论

(1)能正确测定光信号的光强度亮阈值所对应的0号感光单元的运放输出电平为2V;暗阈值所对应的0号感光单元的运放输出电平为1V.

(2)当光强度超过选定的高阈值时,各感光单元的输出值在反复10次的实验中都为1,与理论值一致.

(3)当光强度低于选定的低阈值时,各感光单元的输出值在反复10次的实验中都为0,与理论值一致.

(4)当光强度介于暗阈值与亮阈值之间时,随着光强度的降低(电压值的下降),输出1的能力明显减弱,输出0的能力明显增强.

(5)步骤(3)和(4)的实验结果表明,相邻液晶点像素之间的亮暗对感光阵列没有影响.

3.2 外形及拼接实验

为了验证模块设计中外形封装的正确性,本研究采用厚度为2mm的双色塑料板制作了感光模块的1∶1外形样板,用这种样板进行了拼接实验.操作容易,拼接效果良好,拼接实物照片如图8所示.

图8 感光阵列模块拼接示意图Fig.8 Photoreceptor array module splicing diagram

4 并行解码器与串行解码器的对比

三值光学计算机解码器的基本功能是将光学处理器的输出结果从光信号转换为电信号,其核心部件是光电转换器件,将感光阵列作为光电转换器件的解码器称为并行解码器,将CMOS手机摄像头作为光电转换器件的解码器称为串行解码器.虽然二者的解码过程比较类似,但在性能上却有较大区别.

首先,在串行解码器中,CMOS摄像头工作速度以满足视觉为目标,通常为30帧/s,鉴于视觉要求的帧频远远慢于图像传感器处理一帧图像数据的速度,故摄像头都采用行扫描工作方式,即采用摄像头对图像像素依次处理的串行技术,因此采用该器件的解码器也是串行的.解码的每个数字电信号的宽度为8位或10位,进而影响光学解码器的工作速度.

本设计的感光阵列能够全并行地探测到三值光学处理器对应像素的光状态,并且同时将光电转换结果进行输出.三值光学处理器的信号光源与SI-PIN光电二极管的光谱特性相符合,均在可见光与红外光之间;光电二极管响应时间的数量级为10-6s,低于液晶的响应时间(10-3s)[27-28].另外,感光阵列中使用的光电二极管具有信号噪声低、线性性能好、价格低廉、使用寿命长、外加电压低、功耗小和稳定可靠等优越的特性,能满足光学解码器的全并行、低功耗和可靠性的需求,故感光阵列更适合用作三值光学解码器中的光电转换器件.

5 结束语

随着三值光学计算机整机实验系统SD11的建成,快速提高三值光学计算机的性能成为下一个研究重点.在当前的三值光学计算机实验系统中,制约提高运行速度的主要因素之一是解码器感光部分采用了串行工作的摄像头,因此研发并行工作的解码器感光部件成为提高三值光学计算机性能的关键技术之一.本研究为解决这一问题设计了一款并行感光阵列器件.该设计采用将16个感光单元电路集成为一个感光模块,再用多个感光模块拼接成实用的并行感光阵列之策略.由于感光模块的集成度低而用量大,因此大幅度降低了研发成本,提高了感光阵列的可维护性;而且感光模块的几何尺度适中,能容纳足够多的电路引脚,便于保存、手持、安装.经过实验验证,本设计的感光单元电路功能达到要求,工作可靠;感光模块外形合理,拼接方便,相对位置稳定可靠.本研究为厂家生产这种并行感光模块奠定了理论基础和提供技术支持,为三值光学计算机构造并行解码器解决了关键技术问题.

[1]JIN Y,HE H C,L¨U Y T.Ternary optical computer principle[J].Sci China Ser F-Inf Sci,2003, 46(2):145-150.

[2]JIN Y,HE H C,L¨U Y T.Ternary optical computer architecture[J].Phys Scr,2005,T118:98-101.

[3]金翊.走近光学计算机[J].上海大学学报(自然科学版),2011,17(4):401-411.

[4]YAN J Y,JIN Y,ZUO K Z.Decrease-radix design principle for carrying/borrowing free multivalued and application internary optical computer[J].Sci China Ser F-Inf Sci,2008,51(10):1415-1426.

[5]JIN Y,WANG H J,OUYANG S,et al.Principles,structures,and implementation of reconfigurable ternary optical processors[J].Science China Information Sciences,2011,54(11):2236-2246.

[6]王宏健,金翊,欧阳山.一位可重构三值光学处理器的设计和实现[J].计算机学报,2014,37(7):1500-1507.

[7]张茜,金翊,宋凯,等.三值光学计算机MPI编程技术在超算集群中的使用[J].上海大学学报(自然科学版),2014,20(2):180-189.

[8]李梅,金翊,何华灿,等.基于三值逻辑光学处理器实现向量矩阵乘法[J].计算机应用研究,2009, 26(8):2839-2841.

[9]YAN J Y,JIN Y,SUN H.Study on the feasibility of coding and decoding multi-bit ternary optical signal used in ternary optical computer[J].Comput Eng,2004,30(14):175-177.

[10]SUN H,JIN Y,YAN J Y.Research on principle of coder and decoder in ternary optical computer by experiment[J].Comput Eng Appl,2004,40(16):82-83,136.

[11]JIN Y,GU Y Y,ZUO K Z.Theory,technology and implementation of ternary optical computer[J].Science Sinica,2013,43(2):275-286.

[12]严军勇,金翊,孙浩.三值光计算机多位编码器与解码器的可行性实验研究[J].计算机工程,2004, 30(14):175-177.

[13]ZUO K Z,JIN Y,XUE T,et al.Study on image acquiring system based on decoding simulator of ternary optical computer[J].Semicond Optoelectron,2008,29(6):949-952.

[14]XUE T,JIN Y,ZUO K Z.Data acquiring control system for decoder of tema optical computer[J].Comput Eng Des,2009,30(17):3932-3933.

[15]LIU S B,PENG J J,JIN Y,et al.Technology of synchronizing decoder with operator in TOC experimental system[J].Comput Eng Des,2010,31(16):3565-3568.

[16]JIN Y,HE H,AI L.Lane of parallel through carry in ternary optical adder[J].Sci China Ser F-Inf Sci,2005,48(1):107-116.

[17]JIN Y,SHEN Y F,PENG J J,et al.Principles and construction of MSD adder in ternary optical computer[J].Sci China Ser F-Inf Sci,2010,53(11):2159-2168.

[18]沈云付,潘磊,金翊,等.三值光学计算机一种限制输入一步式MSD加法器[J].中国科学E辑(信息科学),2012,42(7):869-881.

[19]LIU Y,PENG J,CHEN Y,et al.A new carry-free adder model for ternary optical computer[C]// Distributed Computing and Applications to Business,Engineering and Science(DCABES),2011 Tenth International Symposium on IEEE.2011:64-68.

[20]SONG K,YAN L.Design and implementation of the one-step MSD adder of optical computer[J].Applied Optics,2012,51(7):917-926.

[21]PENG J J,SHEN R,JIN Y,et al.Design and implementation of modified signed-digit adder[J]. IEEE Transactions on Computers,2010,53(11):2159-2168.

[22]初宁,曹立军,黄威.基于光照强度的PIN光电二极管响应时间分析[J].传感技术学报,2013,26(1):34-37.

[23]戴竞,张敏明,何岩,等.新型液晶光学相控阵的特性研究[J].光子学报,2014,43(2):61-66.

[24]秦臻,林祖伦,叶祥平,等.CMOS图像传感器光电二极管模型[J].电子器件,2014(6):1039-1042.

[25]LEI L,JIN Y.Auto-measurement of grayscale threshold of ternary optical computer's decoder[J].Comput Eng Des,2012,33(1):233-237.

[26]雷镭,金翊.三值光学计算机解码器亮度阈值自动测定技术[J].计算机工程与设计,2012,33(1):233-237.

[27]金翊,欧阳山,宋凯,等.三值光学处理器的数据位管理理论和技术[J].中国科学E辑(信息科学), 2013,43(3):361-373.

[28]金翊.三值光计算机高数据宽度的管理策略[J].上海大学学报(自然科学版),2007,13(5):519-523.

[29]谌章义.千位三值光学处理器理论、结构和实现[D].上海:上海大学,2010.

本文彩色版可登陆本刊网站查询:http://www.journal.shu.edu.cn

Design of parallel photosensitive array in ternary optical computer decoder

SHI Yeqiang,JIN Yi,OUYANG Shan,ZHAN Haojun

(School of Computer Engineering and Science,Shanghai University,Shanghai 200444,China)

This paper discusses the design of a parallel photosensitive array for a decoder in a thousand-bit ternary optical computer.The strategy is to make a parallel module with 16 photosensitive pixels and circuits,and joint some modules into a utility parallel photosensitive array.Each module transforms 16 three-state optical signals from a ternary optical processor into 16 two-state electoral signals concurrently.A parallel photosensitive array then transforms thousands of three-state optical signals into electoral signals concurrently.Thus the module becomes a low-cost,maintainable and replaceable parallel photoelectric device.Experiments are performed to verify stability and correctness of the photosensitive pixels and their circuits.A test on four samples of the module outline shows that splicing a large-scaled photosensitive array with lots of modules is convenient.

photoelectric conversion;parallel photosensitive array;ternary optical computer;module design

TP 311

A

1007-2861(2016)04-0449-12

10.3969/j.issn.1007-2861.2015.01.004

2014-12-17

国家自然科学基金资助项目(61073049);国家自然科学基金青年基金资助项目(61103054);上海市教委科研创新项目(13ZZ074,13YZ005);上海市自然科学基金资助项目(13ZR1416000);上海高校青年教师培养资助计划项目(ZZSD13035)

金翊(1957—),男,教授,博士生导师,研究方向为三值光学计算机和计算机体系结构. E-mail:yijin@shu.edu.cn