一种载波通信SOC信道交织/解交织器设计

2016-10-18戴澜,张扬

一种载波通信SOC信道交织/解交织器设计

电力线载波通信(PLC)是一种以现有低压电力网络作为通信媒介的有线通信方式。如果和加密技术相结合可以更好的保证信息的高效传输。现有电力线网络产品,无论是宽带电力线通信产品还是窄带电力线通信产品,随时都可以在智能控制、家庭物联网或者是远程抄表等生活的各个方面找到实际应用案例。通信信道特性一直是制约通信系统可靠性的主要因素。电力线载波通信非理想信道特性加上外部噪声干扰的影响,使得数字信号码元数据在传输的过程中质量变坏为了在信噪比已知的情况下,尽可能降低通信的误码率我们采取了相应的基带处理技术。对于叠加在信号的各种加性干扰噪声常采用差错控制编码技术来处理。

前向纠错编码技术(FEC)被广泛的研究,一般的前向纠错技术包括交织和编码以及解交织和译码技术等。本文是在参考了国际插座联盟协议以后,针对项目需要而设计的一种宽带载波通信SOC信道交织/解交织器。

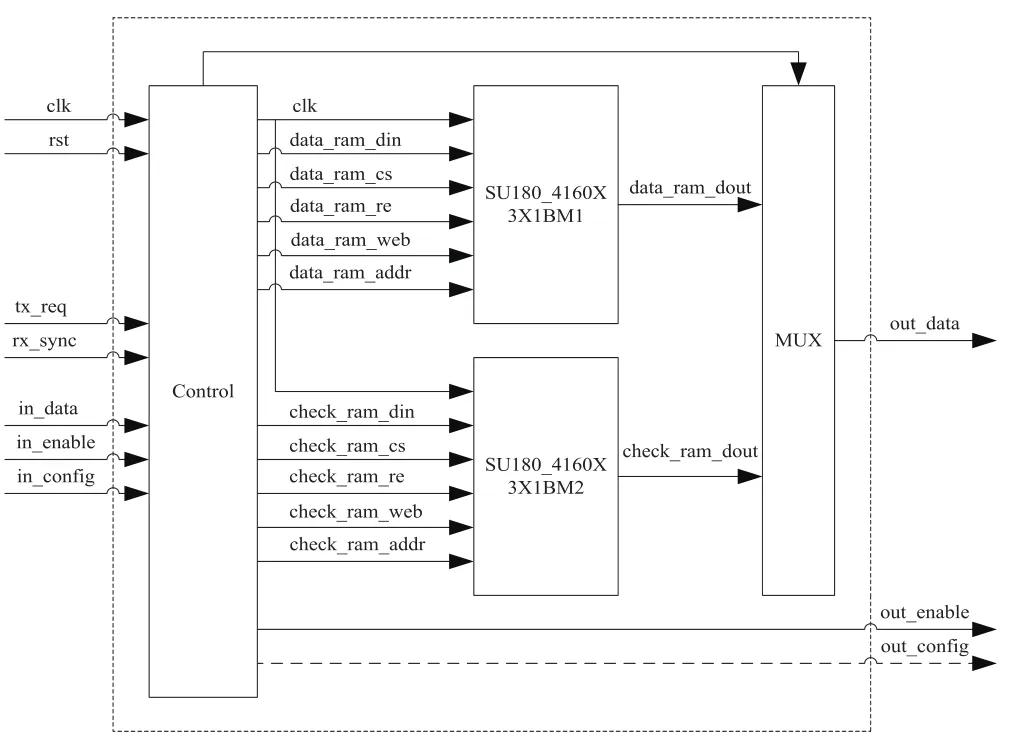

图1 载波通信SOC整体架构框图

载波通信SOC架构及其信道交织/解交织算法

载波通信SOC架构

上图1为载波通信SOC数据流处理架构图,信道交织/解交织分属发送和接收端的两个链路,在发送端信道交织器将Turbo编码器编码后的数据进行不同模式下的处理,以使不同类型的原有排序被不同程度的随机化打散,由信道到数据如果被连续的突发差错干扰,则原始顺序的数据只受到随机差错的干扰。在接收端,将被信道交织器打乱的原始数据进行解交织处理,恢复原有排序,再结合Turbo译码器进行随进差错的纠错,大大提高了通信的抗干扰能力,降低误码率,提高通信质量和效率。

信道交织/解交织算法

信道交织和解交织是一个互逆的过程,以下以信道交织为例说明交织器的设计原理:

Turbo编码产生的数据信息位、校验位与编码前的顺序相同,并且信息位在前,校验位在后(Turbo编码产生的两个校验位是p在前,q在后)。该数据要先进行信道交织,然后作星座点映射。

下面定义K为信息比特的数目,N-K则表示校验比特的数数目,可将K个信息比特分成4个子块,每个子块的大小为K/4比特,将N-K个校验比特同样分成4个子块,每个子块的大小为(N-K)/4比特,信道交织过程的的实现分为以下4个步骤:

(a)信息位的交织:将Turbo编码输出的信息码数据写入矩阵存储空间中,编码器顺序输出信息数据的第一块K/4比特到第一个子块Bank1中,第二块K/4比特到第二个子块Bank2中,依次类推,可以看作把信息比特存入一个K/4行4列的矩阵,第1列代表Bank1子块,第2列代表Bank2子块,依次类推。进行交织时每行的4个比特是同时读出的。从存储矩阵读取数据时,从第0行开始读取,从第二次开始每次读取数据的时候行地址均加上一个偏置参数StepSize,这样第一轮读的行地址顺序为(0,StepSize,2*StepSize,…[K/4]-StepSize),当读了[K/4]/StepSize行之后,就读到了矩阵存储器的尾部,然后读下一轮的行地址初始化为1,之后每次读的时候行地址加上参数StepSize,当读了[K/4]/StepSize行之后又到了行尾,这样第二轮读的行地址顺序为(1, 1+StepSize,1+2*StepSize,…[K/4]-StepSize+1),然后以后读取每轮结束,都对初始地址累计加1,依次类推,经过StepSize轮之后全部行的数据都被读出;

(b)校验码交织:从Turbo编码输出校验bits的第一块(N-K)/4bits到Bank1中,第二块(N-K)/4bits到Bank2中,第三块(N-K)/4bits到Bank3中,第四块(N-K)/4bits到Bank4中,可以看作把校验bit存入一个(N-K)/4行4列的矩阵,第1列代表Bank1,第2列代表Bank2,类似信息位的设定。对于1/2码率,校验bits的读法与信息bits的读法类似,不同的地方在于校验bits第一次读从偏移参数offset定义的行开始,步长参数还是StepSize ,可定义T=(N-K)/4,第一轮读出的行的顺序为(offset, (offset+StepSize)mod T,(offset+2*StepSize) mod T, …(TStepSize+offset) mod T),然后第二轮行初始值加1,再重复读取StepSize-1轮,经过共StepSize轮,每轮读出了T/StepSize行数据,一共读出T行数据。对于16/18码率,与1/2码率不同之处在于,每轮读完不用初始化行初始值为上一次初始化值加1,而是从开始就持续的读(offset, (offset+StepSize) mod T, (offset+2*StepSize)mod T,…),一直到T行读完。信道交织用到的参数如表1定义;

图2 信道交织/解交织设计框图

表1 信道交织参数

(c)信息码和校验码之间的交织: 对于1/2码率,输出的前4比特为信息码,接着4比特为校验码,以此类推。对于16/18码率,首先是3个4bits的信息bits,然后是4bits校验bits,最后是5个4bits信息bits,重复这一模式;

(d)半字节移位:半字节移位以4比特为单位进行移位,不论信息比特还是校验比特,每2个半字节调整一次顺序,规则如表2所示。

表2 半字节移位

上图中b0表示bit来自信息或者校验bits的Bank1,b1表示bit来自信息或者校验bits的Bank2,b2表示bit来自信息或者校验bits的Bank3,b3表示bit来自信息或者校验bits的Bank4。比特串行输出时,4bits中最左边的bit先输出,从左向右。当输出半字节序号为9时,重新从1开始继续循环进行半字节比特移位,直至完成所有输出码。

信道交织/解交织器RTL设计

设计采用两块3bit位宽,深度为4160的RAM分别进行发送/接收数据信息位/校验位的暂时存储。当工作在发射机状态时,本设计作为信道交织器工作,当工作在接收机状态时,本设计作为解交织器工作。图2为设计框图。

然后利用ModelSim仿真软件进行DC综合前的RTL仿真,进行DC综合然后利用DC综合生成的netlist网表进行仿真,验证仿真结果与Matlab建模处理的结果。可以得出网表仿真结果与RTL前仿结果功能一致。说明信道交织/解交织器RTL设计功能验证通过。

结语

本文在参考了电力线载波通信协议HomePlug AV 1.0的基础上,针对课题项目需要设计的一种应用于载波通信SOC的信道交织/解交织器,经过RTL设计与ModelSim仿真,初步验证功能和时序的正确性,通过采用SMIC 55nm工艺和Synopsys综合工具DC综合后的网表仿真,进一步验证了设计的正确性。设计过程中,采用RAM和其他相关电路资源共享的形式设计信道交织器和信道解交织器,在符合项目中信道交织/解交织模块在不同工作状态下的功能和速度要求的同时减小了资源消耗。为进一步的研究设计工作奠定了基础。

10.3969/j.issn.1001- 8972.2016.18.014