数字多波束发射终端的通道一致性研究

2016-09-22韩双林翟江鹏魏海涛

韩双林,翟江鹏,魏海涛

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

数字多波束发射终端的通道一致性研究

韩双林,翟江鹏,魏海涛

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

数字多波束天线的波束指向精度与发射终端通道一致性有密切关系。针对通道一致性问题从硬件和软件两方面对发射终端进行了设计。硬件方面主要是采用等长线的方法保证各个通道信号所经过的链路时延一致。软件方面设置相关参数使通道间时间同步和D/A同步,并通过标校校准每个通道的输出信号。试验结果表明,以上措施有效地减小了通道间幅度、相位和时延差异,提高了通道一致性。该研究也为其他阵列天线系统设计提供了有益的参考。

阵列天线;数字多波束;通道一致性;同步

0 引言

数字多波束发射系统结合了阵列天线和数字信号处理技术。数字多波束系统的基带信号产生和波束合成均在数字域实现[1],合成后的数字信号经过D/A和上变频变成模拟射频信号,经过天线阵元辐射,在空中形成相应波束。

由于整个发射系统需要多个阵元协同工作,而不同阵元通道间的软硬件不可能完全一致,从而造成通道间信号的幅度、相位和时延不一致,继而影响合成波束的指向精度[2]。

本文从硬件和软件两方面对多波束发射终端进行了重新设计。硬件方面,采用等长线设计将FPGA与D/A间走线以及D/A与上变频间走线设计为等长,使得所有通道的基带信号以及中频信号线时延尽量保持一致。同时,时钟芯片与多片D/A间走线等长确保了时钟到达D/A的线延迟一致。软件方面,设置时钟芯片AD9522工作在零延迟模式使输出时钟与输入时钟相位严格对齐[3]。D/A芯片AD9148工作在数据速率模式,在输入时钟同步的情况下,设置相关参数使多片D/A输出同步[4]。最后,将通道输出信号反馈到接收端进行幅度和相位标校。测试结果表明,以上措施有效地提高了发射终端的通道一致性。

1 数字多波束发射系统总体设计方案

数字多波束发射系统主要由上位机、发射终端、功放、阵列天线和小环终端组成,如图1所示。上位机下发工作参数至多个发射终端,发射终端根据下发参数产生1个或多个波束基带信号,并进行加权合成,合成后的波束基带信号通过DA变换、上变频被调制到射频载波,射频载波经过功放放大后传输到阵列天线。信号到达阵列天线后被分为2路:主路信号经过阵列天线辐射在空间形成相应波束;辅路信号经多选一开关反馈至小环终端用于通道一致性校准。

图1 数字多波束发射系统结构

2 数字多波束发射终端

数字多波束发射终端结构框图如图2所示。发射终端采用DSP+FPGA+DA架构,DSP主要用作信息交换,把上位机通过网口下发的数据写入FPGA,同时将本地工作状态上报给上位机。FPGA根据DSP写入的工作参数产生相应波束基带信号,并进行波束加权合成,合成后的波束基带信号送入D/A芯片,AD9148将数字基带信号进行数模转换后调制到中频载波,最后经过上变频器变成射频信号发送出去。时钟分配芯片AD9522负责将输入的1路时钟分成多路时钟,供FPGA及AD9148模块使用。

图2 数字多波束发射终端硬件结构

3 通道一致性研究

通道一致性主要由时钟同步、D/A同步和幅相同步这3个方面保证。基带信号的产生、数模转换以及上变频均和时钟相关,时钟不同步将直接导致通道间时延和载波相位不一致[5]。D/A同步指多片AD9148彼此同步,保证输出的中频载波信号相位一致。幅相同步是测量输出射频信号的幅度和相位,并根据结果对其校正使得最终输出信号幅相一致[6]。

如图2所示,每个发射终端产生8路通道信号经功放传输到对应的8个天线阵元,为了保证8路通道信号的一致性,从硬件和软件2个方面同时考虑。

3.1硬件

信号在传输线上传输时会产生时延。如果某一信号的传输距离较长,其时延也会较大,2个信号传输距离不同,它们之间就存在相对时延,这相当于其中一个信号发生了相移[7]。因此,通常需要对传输线进行等长处理。对于发射终端,硬件上要使每路通道信号所经过的电路传输距离尽量保持一致。主要包括以下几个方面:

① FPGA与4片AD9148间的PCB走线等长,保证8路基带信号从FPGA到AD9148所走过的路径基本相等;

② 时钟分配芯片AD9522输出至4个AD9148的参考时钟CLK2~CLK5彼此等长,保证时钟到达AD9148时相位一致,为多片AD9148同步做准备;

③ AD9148与上变频器间信号线等长,使输出的中频信号到达上变频器时相位一致。

3.2软件

3.2.1时钟同步

发射终端的工作时钟均由AD9522产生。外部时钟首先进入AD9522,在其内部经过倍频分频分路,最终由通道分路器输出时钟提供给终端其他模块使用。为了保证输出时钟与输入时钟相位严格对齐,使能AD9522的零延迟模式。零延迟模式通过将通道分路器0的时钟反馈至PLL,PLL自动同步输入的参考时钟相位和通道分路器0的输出时钟相位。因为AD9522的其他通道分路器输出与分路器0的输出同步[8],所以AD9522所有的输出均与输入参考时钟同步。

3.2.2D/A同步

FPGA输出的数字基带信号进入AD9148后经过预调制、插值和滤波,正交调制到中频载波,最后通过DAC转换成模拟中频信号。每个AD9148可以同时产生2路中频通道信号,4个AD9148共产生8路中频通道信号,为了保证8路中频信号相位关系稳定,4个AD9148需要同步工作。

AD9148支持数据速率同步和FIFO速率同步这2种同步模式,当使用芯片自带的时钟倍频器时,AD9148只能工作在数据速率同步模式[9]。数据速率同步模式下,默认AD9148的参考时钟输入作为同步信号。参考时钟到达多片AD9148的相位差应尽量小,细微的相位差直接导致输出的中频信号时序不一致[10]。发射终端的4个AD9148参考时钟均来自AD9522,其零延迟模式保证了AD9522输出的4个时钟彼此相位一致。等长的PCB走线将最大程度的减小到达AD9148的参考时钟相位差。

AD9148输入信号FRMAE及DCI均由FPGA提供,Frame信号用来复位DA内部FIFO的写指针,DCI是AD9148内部DAC的采样时钟。FPGA内部由同一个时钟源驱动4个DCI信号,保证了4个DCI信号的同步。

在满足上述条件下,执行如下同步步骤:配置数据速率模式,设置寄存器0x10值为0xC0;读取同步状态寄存器0x12,bit6为高电平表示芯片已经同步锁定;给予FRAME一个高脉冲以复位FIFO,可以保证写入FIFO的数据正确。完成此步骤后,所有AD9148均已同步。

3.2.3幅相同步

实际系统中受器件参数差异和工艺水平的制约,不能保证所有通道链路在硬件上完全一致,由此产生的通道不一致性可以通过标校手段加以校正[11-12]。

S(t)=R(t)cosθ(t)cosωct-R(t)sinθ(t)sinωct=

I(t)cosωct+Q(t)sinωct。

式中,I(t)=R(t)cosθ(t),Q(t)=-R(t)sinθ(t),分别为I和Q分量。换算得到:

由以上公式可知,通过调整I和Q的权值可以达到调整PSK调制信号的相位θ(t)和幅度R(t)的目的。

系统正式工作前会依次对所有通道进行标校,具体标校流程如图3所示。首先设置通道的工作参数,包括初始权值等,使通道n输出射频调制信号。小环终端收到通道n的反馈信号后测量其幅度和相位,并将测量结果上报给上位机,上位机比对上报的测量值和本地预存的基准值,若比对一致则进行下一个通道的标校,否则根据比对结果对权值进行修正,直至测量值和基准值比对一致,再进行下一个通道的标校。重复此过程完成所有通道的标校。标校过程中上位机会存储所有通道的标校参数,在系统正常工作时,上位机会在标校参数的基础上计算新权值,保证了所有通道幅相一致。

图3 标校流程

4 测试结果分析

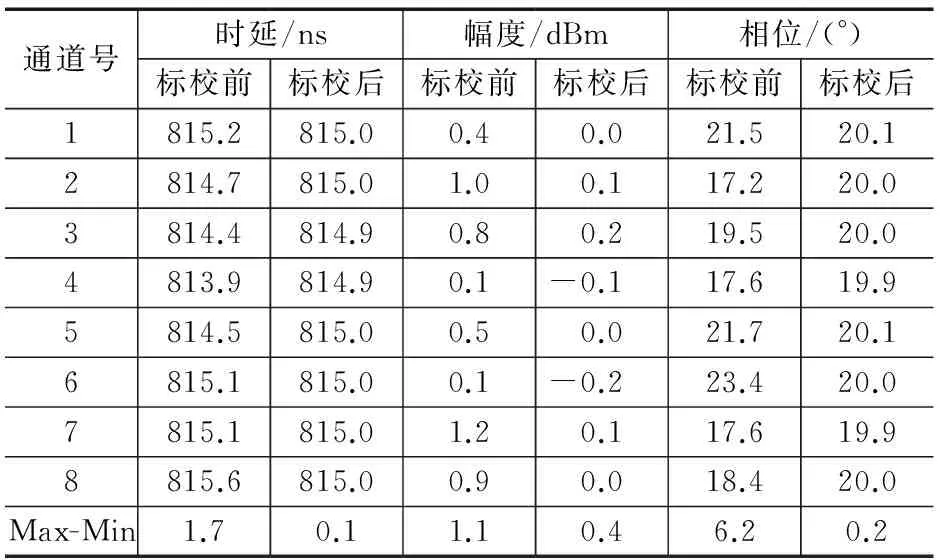

分别对标校前和标校后的数字多波束发射终端8个通道的时延、幅度和相位进行测量。结果如表1所示。

表1 发射终端标校前后数据对比

由表1可知,数字多波束发射终端通道时延波动范围由标校前的1.7ns减小到标校后的0.1ns,幅度波动范围由标校前的1.1dBm减小到标校后的0.4dBm,相位波动范围由标校前的6.2°减小到标校后的0.2°。测试结果表明,以上措施有效地提高了发射终端的通道一致性。

5 结束语

中对于通道一致性问题多是从软件方面进行校正,而本文从硬件和软件两方面同时考虑,在发射终端硬件设计之初就充分考虑了多个通道间的一致性问题。因此,在软件标校过程中会更快地实现标校目标,节约标校时间,加快系统重启进度。目前,该设计已应用在多波束发射系统中并取得良好效果。本文也为其他阵列天线的发射终端设计提供一种有益的参考。

参考文献

[1]江天洲.相控阵雷达发射数字波束形成的设计与实现[D].西安:西安电子科技大学,2014.

[2]见伟,张玉,韩名权.阵列天线通道误差对波束性能的影响分析[J].无线电工程,2014,44(11):45-48.

[3]Analog Devices.AD9522 Datasheet [S],2008.

[4]Analog Devices.AD9148 Datasheet [S],2010.

[5]贾向东,李凡,郑建光.智能天线基带幅度加权波束赋形及其CDMA应用性能分析[J].电波科学学报,2010,25(3):505-512.

[6]耿新涛.相控阵发射系统中幅相校准方法研究[J].无线电通信技术,2008,34(1):59-61.

[7]杨章平.高速PCB设计中的差分等长处理及仿真验证[J].通信技术,2015,48(5):626-630.

[8]贾振安,杨晓晶.浅析AD9522时钟分频电路原理[J].电子世界,2013(14):21-22.

[9]Analog Devices.AD9148 Quick Start Guide[S],2010.

[10]翟健.基于DDS的发射数字波束形成技术研究[D].南京:南京理工大学,2012.

[11]尹继凯,蔚保国,徐文娟.数字多波束天线的校准测试方法[J].无线电工程,2012,42(2):42-45.

[12]张晓,薛锋章.智能天线内置一体化合路校准网络[J].移动通信,2014,38(2):76-79.

[13]朱丽,龚文斌,杨根庆.多波束天线通道幅相一致性校正及实现[J].微计算机信息,2007(20):158-160.

韩双林男,(1985—),硕士,工程师。主要研究方向:卫星导航。

魏海涛男,(1979—),硕士,高级工程师。主要研究方向:卫星导航。

Study on Channel Consistency of Digital Multi-beam Transmitting Terminal

HAN Shuang-lin,ZHAI Jiang-peng,WEI Hai-tao

(The54thResearchInstituteofCETC,ShijiazhuangHebei050081,China)

The pointing accuracy of digital multi-beam antennas is closely related to the consistency of transmitting channels.To solve the problem of channels consistency,the design is made from two aspects includinghardware and software.In thehardware aspect,the method of equal-length circuit is used to ensure that the path that signal on every channel passes through is identical in time delay.In the software aspect,correlative parameters are set to synchronize time and D/A among channels,and the output signal of every channel is aligned by calibration.Experiment results show the measures above reduce the difference in amplitude,phase and time delay among channels,and improve the channel consistency.The study is a useful reference for other array antennas system.

array antennas;digital multi-beam;channel consistency;synchronization

10.3969/j.issn.1003-3106.2016.09.19

2016-05-27

国际合作课题基金资助项目(2013DFA10540);河北省“三三三人才”培养基金资助项目(A201400116)。

TP391

A

1003-3106(2016)09-0073-03

引用格式:韩双林,翟江鹏,魏海涛.数字多波束发射终端的通道一致性研究[J].无线电工程,2016,46(9):73-75,79.