基于相对比率的高帧频图像采集器设计与实现*

2016-09-16孙小进李平安黄秀亮湖南信息职业技术学院电子工程学院长沙410200

孙小进,李平安,黄秀亮(湖南信息职业技术学院电子工程学院,长沙410200)

基于相对比率的高帧频图像采集器设计与实现*

孙小进*,李平安,黄秀亮

(湖南信息职业技术学院电子工程学院,长沙410200)

为了在机器视觉应用中实现高动态范围HDR(High Dynamic Range)图像采集,提出一种基于检测像素相对比率的新型图像采集系统。提出的图像采集器使用全差分电路检测信号比,并通过基于数字计数器的紧凑列并行读出电路捕捉像素的脉冲宽度调制输出,系统设计了相应的光电流比检测像素方法,能独立地捕捉局部场景特征。实验结果显示:提出的COMS图像传感器性能较好,当标称帧频为9 600 frame/s时,提出的32像素×32像素阵列原型CMOS图像传感器消耗了4mW的功率;当最大帧频为24 000 frame/s时,此图像传感器消耗了6.8mW的功率。

CMOS图像传感器;高帧频;HDR;相对采集;机器视觉

遥感、生物医学成像、摄影和汽车等许多工业应用领域都需涉到及高动态范围HDR成像技术[1~3]。而具有高动态范围的机器视觉既能够分辨捕捉场景中照明好的区域,也能够分辨照明差的区域[4]。因此对于机器视觉应用来说,HDR也是关键的因素之一。

传统的CMOS图像传感器存在许多缺陷,其处理过程通常是将光生信号读出,作为电压值,然后通过集成发光二极体结电容上的光电流推算出电压值,其输出电压的最大值由像素和读出电路确定。因此,有用信号的物理饱和度限制了最大信号幅度,从而限制了动态范围。此外,由于集成了结电容上的光电流,有用信号的幅度也取决于发光二极体的积分时间。为了获得较好的图像信噪比SNR,可以通过调节积分时间,使带有最大信号幅度的像素接近于输出饱和。然而,如果被捕捉场景中的最大照明度变得非常高,黑暗区域对应像素的输出信号,很可能会降到噪声基底水平以下,从而无法捕获。此外,调节积分时间使帧频与传感器SNR之间达到一种权衡,这样捕捉出现明显移动的场景会成为问题。在许多应用中,针对移动场景情形去达到高动态范围是较难以实现的,其原因在于传统的采集系统读取的是绝对信号值;此外,影响传统CMOS图像传感器的动态范围因素还和单端工作电路有关,因为相较于微分电路,单端电路对工艺变化和装置不匹配更敏感。

总之,大多数传统传感器难以获取高动态范围的原因是使用单端电路对绝对信号值进行传统采集。针对这种情况,相关学者提出了一些方法,如将梯度采集相机用于讨论的动态范围高的应用[5]。相比较于绝对信号采集,信号梯度采集能够提供更好的结果,也能够使微分运算与现有空间边缘检测传感器的运算匹配[6,7]。然而,类似与传统基于强度的传感器,现有的相机仍会受到物理限制[8]。相较于场景的“黑暗”部分,相邻像素的信号强度在场景照明好的部分差异更大,也会导致饱和、SNR及帧频的权衡问题产生[9]。

针对上述问题,本文提出了一种空间像素相对采集方法,传感器能够直接检测水平方向上与垂直方向上相邻发光二极体输出强度之间的比率。检测时并未获得绝对信号值。从理论上说,如果捕捉场景的空间信息体现在像素比上,重建的场景是独立于实际的场景照明。此外,相较于检测绝对值,检测比率与超大规模集成电路VLSI(Very Large Scale Integration)设计的本质更相符。由于像素处理的原理跟传统的方法不同(没有“积分时间”),因此可以将场景的照明完全从可实现的帧频中解耦,从而进行高帧频操作。“相对像素”是全差分电路,可以降低对工艺变化的灵敏度。

1 相对成像的概念

图1为相对成像概念的原理图。图1(a)是一个来自传统CMOS图像传感器的长期曝光(即长积分时间)图像。长期曝光图像能够恰当地分辨出场景中的黑暗区域。但是,在明亮区域内,对应的像素会饱和,并且模式信息会丢失。短期曝光图像(即短积分时间,图1(b))可以分辨出明亮区域的式样,但是会丢失黑暗区域的信息。相对成像会检测出垂直方向上相邻像素和水平方向上相邻像素(发光二极体)的比率。我们对垂直比率与水平比率之间的平均值进行计算,图1(c)是结果,可以同时分辨出明亮区域和黑暗区域(两个矩形框)。由于传感器饱和(图1(a)中矩形),长期曝光图像无法分辨出明亮区域,而短期曝光图像无法分辨出黑暗区域(图1(b)、1(c)中矩形)。

图1 传统的CMOS图像传感器的图像和MATLAB模拟的相对成像

2 提出的基于相对比率的像素采集

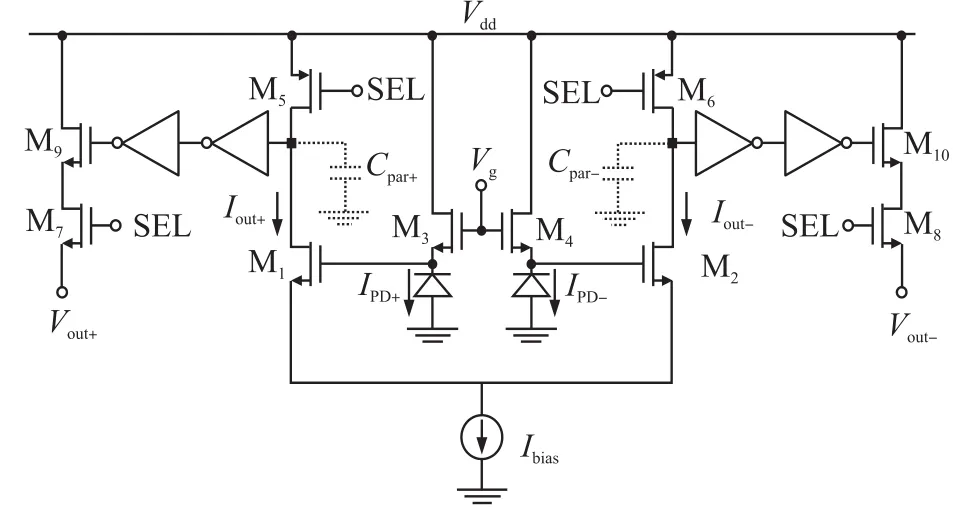

图2是相对比率像素采集的原理图。在每个像素内此原理图被复制两次,一次用于垂直方向,另一次用于水平方向。通过使用跨导线性电路技术,可以方便的实现连续时间模拟处理电路[10,11]。晶体管M1、M2、M3和M4构成了跨导线性环。在环内,MOS晶体管的栅源电压满足下列公式:

图2 相对比率像素采集的原理图

设所有晶体管(M1~M4)的漏源电流足够小(大约在10 nA范围内),所有4个晶体管在弱反型区下运作,则弱反型区工作的NMOS装置的漏源电流可表示为:

其中,nn是NMOS晶体管阈下的斜率系数,μn是电荷载子(电子)有效移动率,Cox是每个单位面积的栅氧化层电容,W是物理的NMOS栅宽,Leff是有效栅长,VT0是晶体管的阈值电压(室温下的标称值)。从公式(2),可得出下列2个公式:

联合式(1)、式(3)或式(4),可得出:

将跨导线性环晶体管M1~M4设计成相同的栅尺寸,从而I0,1=I0,2=I0,3=I0,4。因此有:

从图 2可看出,其中 IDS,1=Iout+、IDS,2=Iout-、

IDS,3=IPD+以及 IDS,4=IPD-(IPD+和 IPD-是对应的发光二极体电流)。因此,基于式(6),发光二极体电流之间的比率可表示为:

由于不存在传统的(发光二极体)积分时间。因此由输出电流(Iout+和Iout-)的比率确定像素输出,且输出电流(Iout+和Iout-)由偏置电流Ibias设置。因此可以在高速条件下可进行比率采集而不需要滚动快门输送像素积分次数(如同传统光栅扫描所做)。用列并行的方式读取像素,同时读取了像素的完整行。当选择读出像素的某一行时,设置选择信号为较高数值,并且关闭预先向寄生电容器Cpar+和Cpar-充电的晶体管。电流Iout+和Iout-开始向寄生电容器放电。当寄生电容器的电压到达了逆变器的切换点时,逆变器会转换输出电压。图3为对应的波形。假设IPD+>IPD-,意味着Iout+<Iout-,进一步表示为寄生电容器Cpar+放电的速度比寄生电容器Cpar-慢(见图3)。因此,通过电容器Cpar-的电压首先到达了逆变器的切换点(Vth)),在负像素输出条件下发生了转换。此转换向读出计数器发送信号开始计数过程(T0)。由于 Cpar+的放电速度比 Cpar-慢(因为IPD+>IPD-),通过电容器Cpar+的电压在Tc-r时间内到达了逆变器的切换点。当Cpar+电压到达了切换点时,逆变器会在正像素输出条件下发生转换,因此,向读出计数器发送信号停止计数过程。

图3 相对采集像素的波形

从选择信号的上升沿开始(选择信号见图3),通过寄生电容器Cpar+的电压到达逆变器切换点(以及停止计数)所需时间可表示为:

其中,Vdd是像素电源电压。同理,通过寄生电容器Cpar-的电压到达逆变器切换点(以及开始计数)所需时间可表示为:

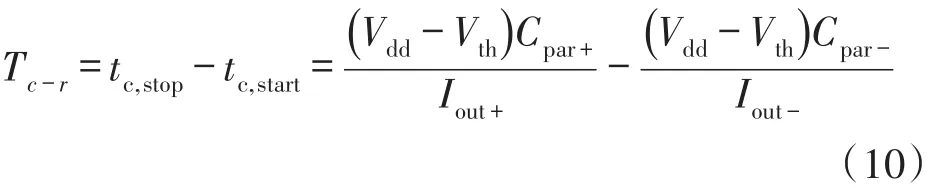

这样,由读出计数器测量的时间间隔(Tc-r=Tcount-ratio)为:

由于对称电路Cpar+=Cpar-=Cpar,由公式(10)得出:

式(11)也可表示为:

由于 Ibias=Iout++Iout-,如果将两个发光二极体电流之间的比率界定为:

并且时间常数τ为:

那么式(11)可表示为:

由式(15)得出下列二次方程:

解二次方程得出:

光电电流比可直接从测量(计算)的时间间隔Tc-r中推断出。由于Tc-r>>τ,式(17)可简化为:

因此,光电流比RF与测量的间隔Tc-r成正比(τ是常数)。即:如果Tc-r→0(当两边的电流相等时),从式(17)得出的比率等于1。图4为对应的像素输出转移函数,横坐标为读出计数器测量的间隔(标准化为τ),纵坐标为基于式(17)的光电流比。

图4 相对比率像素采集转移曲线:对应的输出光电流比RF与标准化为τ的测量时间间隔的对比

使用此技术测量的最短时间间隔(TLSB)与读出计数器的最低位LSB(Least Significant Bit)(或计数器时钟信号的周期)符合。TLSB的最佳选择为等于时间常数τ。,可独立设置TLSB和τ,且通常TLSB=λ·τ,其中λ≥1。由计数器的终值指定可获得的最长时间间隔(Tc-r,max)。因此,可获得的最大绝对像素比为:

将像素(i,j)的强度当作参考像素强度Iref,可检测到的像素(i,j)最小输出强度等于 Iref/RF,max。依此类推,可检测到的像素(i,j+1)最大输出强度等于 Iref·RF,max。因此,相邻像素(i,j+1)的动态范围等于:

对于本文使用的5 bit计数器,基于方程(19),如果TLSB>>τ,RFi等于31。然而,如果TLSB≈τ(或λ≈1),需要考虑FR曲线的非线性(见图4)。经TLSB检测的信号略高。当TLSB≈τ时,线性曲线的偏差最高。基于方程(17)(为Tc-r=TLSB=τ解答),可检测的最小比率等于1.62,并非如线性曲线预测的结果等于1。可检测的最大比率仍等于31,所以,RFi=31/1.62=19.14。因此,对于TLSB≈τ,理论上的像素动态范围最小,且等于:

动态范围值仅用于相邻像素邻域(像素(i,j+1))。将像素(i,j+1)强度作为参考,像素(i,j+2)的动态范围为51.28 dB。然而,如果初始像素(i,j)强度作为像素(i,j+2)的参考,可获得的动态范围为:

通过反复进行同一分析,像素(i,j+k)的动态范围导致DR=k·DRadj。从理论上说,对于大型的像素阵列,重构图像可以获得非常高(与场景相关)的动态范围。

3 相对成像的硬件实现

将相对比率像素采集方法应用于检测相邻发光二极体生成的光电流比率(邻近强度的比率)。其中,每个像素包括两组发光二极体:一组用于垂直方向,另一组用于水平方向,如图5所示。像素基于跨导线性电路原理运行,并检测发光二极体电流的比率。如第3节所述,相对像素提供了脉冲宽度调制输出,其中脉冲宽度与发光二极体电流之间的比率成正比。每个像素列都需要两个5 bit的输出计数器,主要用于测量脉冲宽度:一个计数器测量水平方向的脉冲宽度,另一个测量垂直方向的脉冲宽度。对于包括32×32相对像素的系统,64列平行的输出计数器由控制逻辑电路实施和控制。

图5 相对比率像素成像的版图设计

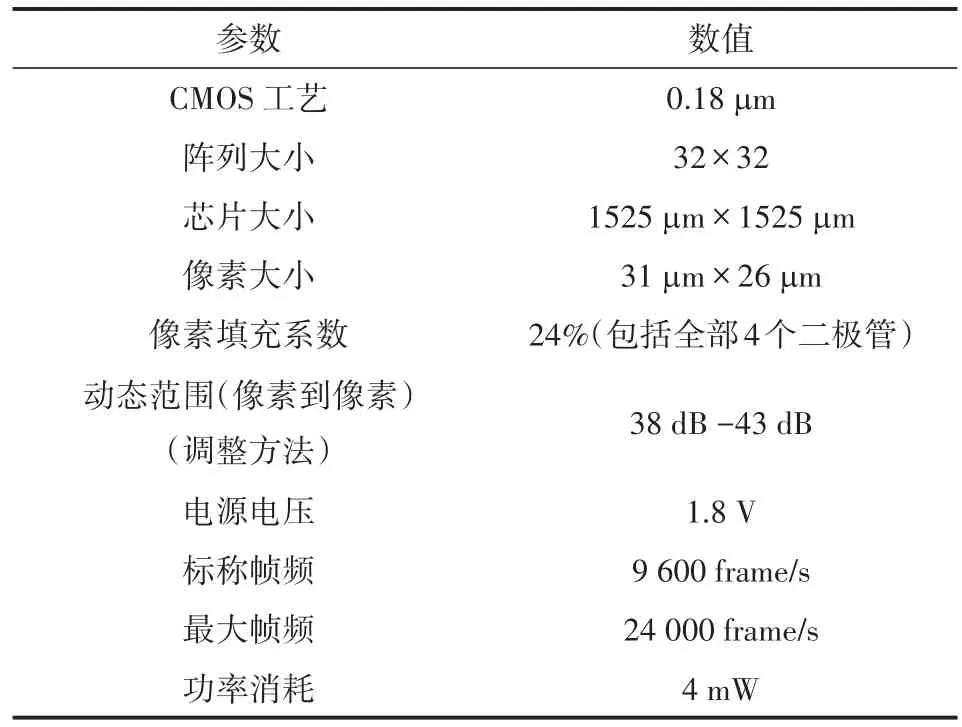

完整的模具大小为1 525μm×1 525μm,主要由32×32的相对采集像素阵列组成。单像素大小为31μm×26μm,其中光检测的有源区为24%。每个像素都进行了较弱的强度采集,动态范围为38 dB~43 dB,在内部发光二极体之间相对引用此动态范围。将包含控制逻辑、读出计数器及行译码器的完整数字模块组合成单块并嵌入像素阵列之下。

4 测量结果

本设计的行选择缓冲器用于驱动行选择线[12]。测量结果表示:当帧率为9 600 frame/s,且电源为1.8 V时,完整的设计会消耗4mW的功率(未带有I/O单元)。在帧频为9 600 frame/s的条件下,大多数功率是由列和行驱动缓冲器消耗,总共消耗了2.8mW。像素阵列消耗了540μW,主要是静态功率,而数字逻辑电路大约消耗了600μW。设计中测量的最高运行帧频为24 000 frame/s,对图像质量未造成严重影响。在帧频24 000 frame/s的条件下,成像器的测量功耗为6.8mW。

图6是完整的测量装置。芯片直接与PCB邻接,且在界线上涂有保护胶。带有金属桶和红外线滤波的小型镜头(标准的M12×0.5尺寸)安装在传感器的顶部。镜头的有效焦距长度为15.8mm,且镜头的焦距比数为2.0(有效孔径为7.9mm)。使用赛灵思的Virtex-5 LX FPGA捕捉到了传感器的数据流。图6是完整的装置。将带有传感器的PCB连接至赛灵思评估平台。让数据进一步从FPGA传送至PC,或通过DVI端口直接传送至显示器。

图6 相对比率图像采集成像装置

图7是传感器在帧频为9 600 frame/s时获得的单独的帧。在此次实验中,传感器捕捉到了印刷在一张白纸上的“相对成像”文本。图7(a)描述了像素偏置电流大约设置为20 nA时传感器的合并原始输出。通过计算比率之间的平均值获得描述的输出,比率源于每个像素的发光二极体的上下对和左右对(见图5)。在此标称模式下,像素跨导线性环MOSFET装置在弱反型下运行。检测了像素到像素的比率,因此,分辨出了对应字母的边缘。3个单独的因素有助于强度波动,表现为背景的总噪声。其中2个因素与传统噪声有关,特别是固定模式噪声FPN(Fixed Pattern Noise)和暂态像素级噪声。弱反型运行对装置不匹配敏感,原因在于阈值电压变化上漏极电流的指数相关性。为了减弱不匹配造成的影响,将跨导线性环晶体管(M1~M4,见图2)分成2个指幅(每个指幅为2μm× 1μm,总共有8个指幅),加上每边的4个假程序。

可在像素布局的中部观察到的如图5所示。FPN的另一个来源是Cpar+和Cpar-之间的不匹配(见图2)。为了实现高帧频,寄生电容必须小,因此,相对电容变化大。有助于整个FPN的第3个因素是背景(白纸)实际上是不均匀的。连同印刷字母的边缘,传感器捕捉了不均匀的纸表面上的反射比。图7(b)描述了当重复同一实验时传感器的原始输出,实验中像素偏置电流大约设置为100 nA。对于超过100 nA的偏置电流,通常跨导线性环晶体管会偏离弱反型运行。像素的转移曲线变得相当非线性,且传感器开始检测强度水平而不是比率。换句话说,照明度越高,比率会越明显。由于偏置电流更高,传感器在非线性运行模式下获得了更高的SNR。尽管此特性可划归为本文提出的像素拓扑的副作用,在许多潜在应用程序中,非线性运行模式是有用的。

图7 从9 600 frame/s的帧频视频流选择的帧,由相对成像传感器捕捉

为了预估和消除不均匀的白色背景造成的影响,本文进行了不同的实验。在实验中,将文本“相对成像”印刷在透明正片上;将传感器设置为固定,且传感器捕捉了印刷文本和固定的背景。在数字领域进行了背景估计和背景减除,作为后处理步骤。图8是通过传感器传送的原始输出帧。背景减除之后,字母的边缘更加明显。

图8 用于捕捉幻灯片上字母的捕获帧

图8(a)是与发光二极体的左右对(左右比)相符的检测到的光电流比。图8(b)是与检测到的上下比相符的原始输出。图8(c)是合并的最终输出,推导出作为上下和左右比之间的平均值(通过算出图8(a)和图8(b)中两个帧的平均值获得图8(c)中的帧)。由于减弱了背景不均匀造成的影响及FPN噪声,通过暂态噪声控制图8中的剩余噪声,在帧频非常高的情况下对暂态噪声做出的预测。对于9 600 frame/s条件下图8中的场景及照明条件,图9是单一像素比检测的SNR与像素偏置电流的对比。

图9 当帧频为9 600 frame/s时,图8场景和实验设置中测量的SNR

当帧频为9 600 frame/s时,测量的总噪声RMS等于1.6 LSB;当帧频为24 000 frame/s时,测量的总噪声RMS等于2.1 LSB。因此,当帧频为9 600 frame/s时,对应的测量像素到像素动态范围等于43.11 dB;当帧频为24 000 frame/s时,对应的测量像素到像素动态范围等于38.39 dB。

表1是相对成像器的特点总结,而表2是与类似特征提取设计作出的对比。

表1 相对比率图像采集器芯片的特点

表2 与类似特征提取设计的比较

5 结论

相对比率图像采集几乎能够排除局部场景照明的干扰,捕捉其场景特点和式样,使其十分适用于了许多HDR(如机器视觉)等工业应用,基于此,本文提出一种基于相对比率的非传统图像采集硬件设计。设计包含了全差分、光电比检测像素,可以忽略对传统光电流集成的需要。将像素采集所需的时间完全从场景照明中解耦,帧频独立于照明水平,因此可以实现非常高的帧频(多达24 000 frame/s)。实验表明:当帧频为9 600 frame时,完整的32像素×32像素原型CMOS图像传感器设计仅消耗了4mW的功率。

[1] 陈德美.基于CMOS图像传感器的高速图像采集与传输系统的研究设计[D].浙江工业大学,2013.

[2] 黄建元,赵新荣,张长顺,等.基于CMOS成像器件的手指静脉图像采集方法及装置[J].红外技术,2009(1):51-56.

[3] 杨会玲,王军,杨会伟.高帧频CMOS实时图像采集系统设计[J].微计算机信息,2008,30:309-311.

[4] 周立波.基于FPGA的高速图像号码识别系统研究与实现[D].湖南大学,2011.

[5] 王旭东.基于FPGA的PCB光电检孔机高速图像采集系统[D].电子科技大学,2011.

[6] 梁爱华,付钪.近红外指静脉图像采集系统设计[J].传感器与微系统,2014(1):113-115+119.

[7] Kim D,Culurciello E.A Compact-Pixel Tri-Mode Vision Sensor[C]//Circuitsand Systems(ISCAS),Proceedingsof2010 IEEE International Symposium on IEEE,2010:2434-2437.

[8] 董大波,王湘云,赵柏秦,等.基于单片机的低成本CMOS图像采集系统[J].仪表技术与传感器,2014(2):45-49,70.

[9] GottardiM,Massari N,Jawed SA.A 100$mu$W 128$times$ 64 Pixels Contrast-Based Asynchronous Binary Vision Sensor for Sensor Networks Applications[J].Solid-State Circuits,IEEE Journalof,2009(5):1582-1592.

[10]TakahashiN,Fujita K,Shibata T.A Pixel-Parallel Self-Similitude Processing for Multiple-Resolution Edge-Filtering Analog Image Sensors[J].Circuits&Systems IRegular Papers IEEE Transactionson,2009,56(11):2384-2392.

[11]孙佳帝.基于SOPC的图像采集及传输系统设计[J].电子器件,2014,37(6):1116-1120.

[12]李华.基于FPGA的高精度图像采集系统设计[J].电子器件,2014,37(5):840-843.

孙小进(1977-),男,汉族,湖南省长沙人,硕士,高级实验师,主要研究方向为机器人控制技术,sunxiaojin151@sina.com;

李平安(1976-),男,汉族,湖南省邵东人,硕士,讲师,湖南信息职业技术学院电子工程学院教师,主要研究方向为信号与信息处理;

黄秀亮(1978-),男,汉族,湖南省怀化人,硕士,高级实验师,湖南信息职业技术学院电子工程学院教师,主要研究方向为模式识别与智能控制。

The Design of High Frame Rate Image Acquisition System Based on Relative Ratio

SUN Xiaojin*,LI Pingan,HUANG Xiuliang

(School ofElectronic Engineering,Hunan College of Information,Changsha 410200,China)

In order to achieve high dynamic range(HDR)image acquisition inmachine vision applications,a novel image acquisition system based on the relative ratio of detection pixels is proposed.The proposed image acquisition device uses a fully differential circuit to detect the signal ratio,and the pulsewidthmodulation output is captured by a compact column parallel readout circuitbased on digital counter.And themethod based on optical flow ratio is designed to detect the pixel,It can capture the local sceen features independently.The experimental results show that the proposed CMOSimage sensor is ofgood performance,when the nominal frame rate is 9600 frame/s,the consumed power of the 32 pixel×32 pixel array prototype CMOS image sensor is 4mW;while themaximum frame rate is24 frame/s,the consumed power of this sensor consumed is 6.8mW.

CMOSimage sensor;high frame rate;HDR;relative acquisition;machine vision

TP752;TP391.41

A

1005-9490(2016)04-0957-07

项目来源:湖南省教育厅科学研究项目(15C0978)

20115-08-22修改日期:2015-10-19

EEACC:6140C10.3969/j.issn.1005-9490.2016.04.039