遥测PCM数据收发接口模块设计

2016-09-16任勇峰李辉景中北大学仪器科学与动态测试教育部重点实验室电子测试技术重点实验室太原030051

王 闯,任勇峰,李辉景(中北大学仪器科学与动态测试教育部重点实验室,电子测试技术重点实验室,太原030051)

遥测PCM数据收发接口模块设计

王闯,任勇峰*,李辉景

(中北大学仪器科学与动态测试教育部重点实验室,电子测试技术重点实验室,太原030051)

为了实现无线遥测PCM数据的备份,设计了基于FPGA的PCM数据收发接口模块。该模块包括RS-422命令下发接口、PCM码接收接口、LVDS数据回收接口和与存储器数据交换接口。配合单元测试设备和存储器,通过上位机软件对回收数据进行解包分析,用以检验接收到的PCM码的误码与丢帧,判断设备的工作情况。该模块采用独立帧结构,PCM数据完全由后续上位机处理,因而具有极强的通用性。经过反复测试验证了数据收发接口模块工作的可靠性与设计的合理性。

无线遥测;通用;独立帧结构;PCM;FPGA

在飞行器的研制试飞试验中,常常需要通过遥测的方法来获取系统内部设备的一些关键参数[1]。由于遥测系统工作的可靠性问题,需要对遥测数据进行备份。

针对需要获取的数据包含的信息量多,为了方便的解包出原始数据,减小硬件消耗,使用PCM(脉冲编码调制)就显示出其优越性。PCM就是对一个连续的模拟信号进行采样、量化,成为离散的数字信号。将数字信号按一定帧格式编码,送入信道传输。为了保证回收后的数据能够正确地解包还原出原始模拟信号,需要在每一帧数据当中插入帧同步码,作为一帧数据的起始或结尾[2]。

1 总体设计

PCM数据收发接口模块作为遥测PCM数据备份的通信接口,可以接收PCM数据并发往存储设备,并在单元测试时,读取存储数据发送给单元测试设备。PCM数据收发接口作为该系统的重要组成部分,包括RS-422命令下发接口、PCM码接收接口、LVDS数据回收接口和与存储器数据交换接口。单元测试设备接收上位机通过USB总线下发的命令,将命令发送给数据收发接口模块,同时模拟PCM码信源产生PCM码流,通过RS-422接口发送给数据收发接口模块;数据收发接口模块响应命令,接收数据并转存到存储模块,或者读取存储数据并通过LVDS接口发送给单元测试设备;单元测试设备将回收数据经USB总线发送给上位机,通过上位机获取数据并分析,可以检验PCM数据传输的可靠性。总体框图如图1所示。

图1 系统总体框图

2 芯片选择及硬件电路设计

硬件系统使用FPGA作为中心逻辑控制器,完成PCM信号的接收和数据存储、回收的功能。

2.1PCM数据接收接口设计

PCM数据接收使用高速光耦进行数据解码译出及电气隔离,接口电路如图2所示。选用仙童半导体的 FODM8071,速度达到 20 Mbit/s,且对共模干扰具有很好的抑制作用。当光耦合器输入端发光二极管的阳极对阴极的压差达到其正向导通压降(典型值1.35 V),发光二极管导通,输出端光敏三极管接受光照后导通,将输出(5脚)拉低到地;当光耦合器输入端发光二极管的阳极对阴极的压差未达到使发光二极管导通的阈值电压,输出端光敏三极管关断,将输出(5脚)拉高到3.3 V。即PCM数据接收为反相接收。

图2 PCM数据接收接口电路

光耦合器传输信号是经过电-光-电转化来实现的,输入、输出端电路没有直接的电气连接,从而避免了输入信号带来的干扰影响内部电路的正常工作。同时由于其为电流传输型器件,可以有效地消除传输线上串扰对于数据传输的影响[3]。

2.2命令接收接口设计

数据收发接口模块需要响应命令,并进行相对应的操作。使用RS-422接口来接收命令,电路原理图如图3所示。使用差分线可以消除共模干扰,但是对于印制电路板设计提出了以下几点要求:(1)两根差分线保持等长,以减小信号传输的延时差;(2)差分线对之间保持等距,保证差分阻抗的连续性,减少反射;(3)印制电路板的叠层设计要合理,差分线保持在同一地平面上,避免跨地平面布线,引入干扰[4]。

图3 命令接收接口电路

DS26C32差分线端接1个100Ω电阻,这是因为差分线作为传输线,其末端电压为源端向负载传输的电压与负载反射的叠加。为了消除反射,要求负载阻抗等于传输线的特性阻抗。而差分线的特性阻抗一般控制在100Ω左右,故在靠近 DS26C32末端的差分线上跨接一个100Ω电阻,以保证差分线末端电压完全降落在电阻两侧[5-6]。

2.3LVDS数据回收接口设计

数据回收使用SN65LV1023A作为差分驱动芯片,将并行的 10 bit数据差分化。SN65 LV1023A是数据位宽 10 bit,外部时钟频率为10MHz~66 MHz的LVDS并串转化器,数据传输速率达到100 Mbps~660 Mbps。针对LVDS驱动能力不足的缺点,使用串行数据电缆驱动器CLC001作为LVDS数据的输出驱动芯片。原理图如图4所示。

SN65LV1023A输出驱动为约3.5mA的恒定电流源,在靠近CLC001输入端跨接一个100Ω电阻,电阻两侧形成±350mV电压,以作为传输线路高低逻辑的判断。CLC001输出源端端接49.9Ω电阻,主要作用是消除末端反射。105电容用以隔离CLC001差分线上约800mV~1000mV直流电压分量。

图4 数据回收接口电路

2.4与存储器数据交换接口设计

使用并行总线分时复用的方式来进行数据的存储及回收,节约了数据线,减少了硬件消耗。在进行数据存储时,发送相关指令跟数据;在数据回收时,接收存储器数据跟返回存储器当前工作地址。

3 逻辑实现

中心逻辑控制器FPGA被动接收PCM数据,控制Flash读写,响应单元测试设备下发的命令并回传数据,其程序原理框图如图5所示。

图5 FPGA程序原理框图

3.1PCM接收模块

单元测试设备发送的模拟遥测PCM码流采用同步时钟方式,既有PCM数据流,也有同步采样时钟,传输速率为10 Mbit/s。由于码元数据同步于时钟的上升沿,故使用时钟下降沿进行解码。PCM数据接收时采用一个8 bit的寄存器,在每一个PCM时钟下降沿依次移入一位数据,完成8 bit数据的接收后,发送给4K异步FIFO,判断FIFO半满之后,从FIFO取数并进行后续的转存处理[7],PCM数据接收接口模块的工作时序如图6所示。

图6 PCM数据接收接口模块程序原理图

异步FIFO的引入,使跨时钟域的通信变得更加有效和可靠。上电配置后即使能FIFO,发送写FIFO时钟(上升沿),即将寄存器当中8 bit数据写入FIFO低地址(由“000000000000”开始);每当写完8 bit数据,写地址加1。由于FIFO异步的特点,需要判断FIFO中是否有数据,引入FIFO半满信号(half=写 FIFO地址-读 FIFO地址),仅当half>2 K时,才开始从当前读FIFO地址开始取数;否则等待。同时为了避免写FIFO的速度太快而覆盖之前的数据,要求读FIFO的速度要比写FIFO的速度快。

3.2LVDS-422控制模块

该模块接收单元测试设备包括复位、记录、读数、停止读数、请求有效、请求无效等命令,为了保证命令的可靠响应,按表1所示的帧结构校对命令,通过依次判断帧头、命令长度、命令高低位交换两次判定、校验两次命令累加和,有效地防止了因为命令错误响应而造成的设备工作状态混乱[8]。

表1 命令帧结构

在接收到读数控制命令时,根据对FIFO半满信号的判断来读取FIFO当中的数据。以TCLK的上升沿作为一次并行数据发送的标志。

3.3M em接口模块

Mem接口模块响应记录命令,接收来自FIFO 的PCM数据,将数据通过数据总线发送给存储模块;响应读数命令,接收来自存储模块的数据,将数据发送给LVDS-422控制模块的FIFO。

4 帧同步的实现

帧同步的作用是通过对数据进行位同步、字同步、帧同步,以解包出原始数据。帧同步的方法一般是通过在数据序列中加入帧同步码的方式来实现的[9]。

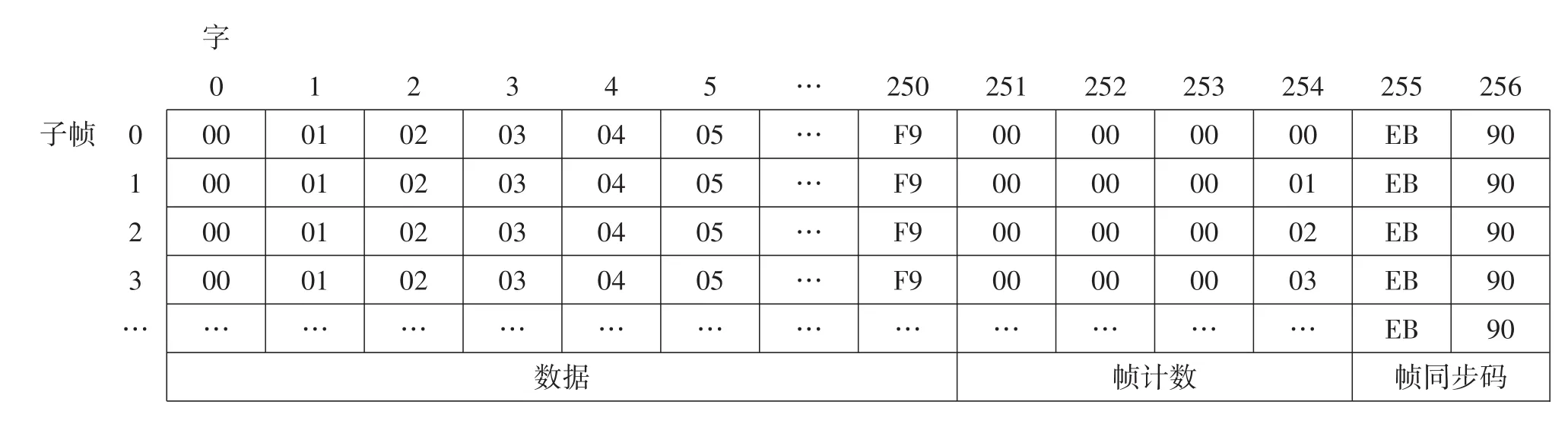

单元测试时,单元测试设备发送递增数或递减数,PCM码流与采样时钟从第1个时钟即同步传输,且在时钟下降沿按位接收,并以每8 bit数据为一个字节转存,故其帧结构始终是同步的,数据递增帧格式如表2所示。

接收遥测PCM时,为了适应不同帧格式PCM数据接收的要求,数据收发接口模块不进行帧同步的判断,而以上电配置完成后接收到的第1个时钟下降沿所对应的数据作为PCM数据的起始,并仍然按表2所示的帧格式转存。硬回收后,回读数据到上位机,根据数据收发接口模块的帧格式,可以解包出原有的遥测PCM数据。使用这种方式各种帧格式的遥测PCM数据均可以正常收发,后续仅需要修改上位机软件对于遥测PCM数据帧同步码的判断逻辑,就可适用于新的帧结构,这极大地提高了设备通用性。

表2 PCM数据递增帧格式

使用单元测试设备来模拟这种情况。如图7(a)所示为没有进行帧同步的递减数据,通过上位机软件对数据依次移位(循环左移或右移)来搜索数据码流当中的帧同步码“1110101110010000”(EB、90)。采用多次判定的方法,即搜索到帧同步码之后,在后面一帧同样位置检测是否为该帧同步码,经过3到5次的判断,可以提高数据还原出来的准确性。如图7(b)所示,为将接收到的数据左移2 bit,得到的还原之后的数据。

图7 数据还原

5 试验结果与结论

为了验证该接口模块工作的可靠性,使用单元测试设备对其进行反复测试。对回收之后的PCM数据经上位机软件显示后如图8所示,EB、90即为帧同步码,在其之前 4 byte数据为帧计数,每帧数据从00递增至F9,没有误码和丢帧,且与单元测试设备发送的数据帧格式一致。

图8 解码接收数据

该PCM数据收发接口模块,整体满足设计要求,实现接收遥测系统以10 Mbit/s速率发送的PCM数据,并在硬回收后获取数据;能够配合单元测试设备及存储器,完成对设备工作状况的检验。该设计方案能够适应不同帧格式PCM数据备份的需求,具有极大的可移植性,对其它PCM数据回收设备的设计也具有一定的参考价值。

[1] 张鹏,陈鸿,武锦辉.基于FPGA的PCM码收发模块设计[J].计算机与数字工程,2011,39(7):190-192.

[2] 夏利利,刘冰,周江,等.PCM遥测帧同步技术性能分析[J].电讯技术,2014,54(6):803-807.

[3] 李丹荣,王新第,杜维.光电耦合器的实用技巧[J].自动化仪表,2003,24(6):58-61.

[4] 吴健,孔德升.高速数据采集卡的信号完整性分析[J].仪表技术与传感器,2013(12):93-96.

[5] 张婧.高速数字电路信号完整性仿真设计与验证[D].西安:西安电子科技大学,2012.

[6] 罗映红,张博.传输线端接阻抗对线间串扰的影响研究[J].郑州大学学报(工学版),2009,30(4):120-122,127.

[7] 裴向东,陈箫,谭秋林,等.基于USB-FIFO的FPGA与上位机通信的设计与实现[J].计算机测量与控制,2012,20(4):1073-1075.

[8] 周涛,李辉景,任勇峰,等.长线422高速传输中的收发模块设计[J].科学技术与工程,2014,14(35):68-71.

[9] 甄国涌,林华亮.串行PCM码流解码电路设计与应用[J].航空计算技术,2005,35(1):79-81.

王闯(1990-),男,汉族,四川南充人,中北大学,硕士研究生,主要研究方向为嵌入式电子电路系统,wangchuangqq123@ 163.com;

任勇峰(1968-),男,汉族,山西中阳人,中北大学,教授,博士研究生导师,主要研究方向为微电路系统、电路系统检测与诊断技术,renyongfeng@nuc.edu.cn。

Design of Telemetry PCM Data Transceiver Interface Module

WANG Chuang,REN Yongfeng*,LI Huijing

(Key Laboratory of Instrumentation Science&Dynamic Measuremen(tNorth Uniυersity of China),Ministry ofEducation;Scienceand Technology on Electronic Testand Measurement Laboratory,Taiyuan 030051,China)

In order to achieve the backup ofwireless telemetry PCM data,a PCM data transceiver interfacemodule is designed based on FPGA.Thismodule includes a sending command interface using RS-422,a receiving interface of PCM code,a data receiving interface using LVDS and a data exchange interface with the storage device. Workingwith the unit testequipmentand storage device,it can be used to check out the biterror and the lost frame of the

PCM code to judge theworking condition of the equipment through using the host computer software to unpack and analyze the recycling data.Thismodule uses independent frame structure.All the PCM data is dealt with the host computer,thus ithas strong generality.Through repeated test,itverifies theworking reliability and design rationality of the data transceiver interfacemodule.

wireless telemetry;generality;independent frame structure;PCM;FPGA

TN914

A

1005-9490(2016)04-0861-05

2015-09-15修改日期:2015-10-26

EEACC:7210G10.3969/j.issn.1005-9490.2016.04.022