基于CPCI的信号采集板卡设计*

2016-09-16韩朝辉孟令军中北大学仪器科学与动态测试教育部重点实验室电子测试技术国家重点实验室太原0005

韩朝辉,孟令军,文 波(中北大学仪器科学与动态测试教育部重点实验室,电子测试技术国家重点实验室,太原0005)

基于CPCI的信号采集板卡设计*

韩朝辉1,孟令军2*,文波3

(中北大学仪器科学与动态测试教育部重点实验室,电子测试技术国家重点实验室,太原030051)

基于CPCI总线和信号采集的相关技术,提出了一种以FPGA为核心的CPCI信号采集板卡的设计。该板卡主要由电源模块、时钟网络、DDRII高速缓存阵列、CPCI通信单元、FMC子卡接口等单元组成。详细描述了板卡软硬件实现的原理,提出了流水线的设计思路,着重介绍了基于乒乓结构的高速DDRII缓存阵列以及CPCI总线的设计思路和实现方式。通过实验验证,高速DDRII缓存阵列可以达到400Mbit/s的传输速率,PLX9656可工作在66MHz的时钟下,并且板卡具有较高的稳定性。

CPCI;信号采集;FPGA;DDRII;PLX9656

随着航空航天技术的不断发展,人们在科学研究中对信号采集和处理的要求变得越来越严格。尤其在雷达、飞行器、运载火箭等高精度设备中,由于其对信号处理的特点是:数据量大、运算复杂,而且稳定性要求很高。这就要求必须设计一种兼具高速而且稳定的信号采集方案。

CPCI(Compact PCI)是国际工业计算机制造者联合会提出的一种总线接口标准。在电气特性上,CPCI总线以PCI电气规范为基础,同时在接口等地方做了重大改进。在机械结构上,CPCI总线结构使用了欧卡连接器和标准3U、6U板卡尺寸。由于其良好的抗震性和通风性,而且还可以热插拔,广泛运用于雷达、飞行器等空间探测领域。

1 CPCI信号采集板卡方案设计

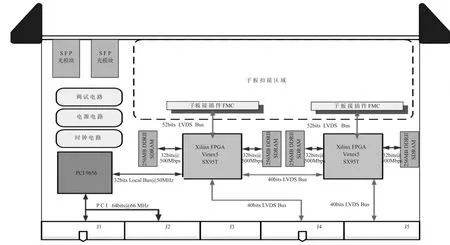

目前工控设备上所使用的CPCI接口板卡一般有3U和6U两种规格,按插卡方式又可分为前插板和后插板。而后插板主要用来信号数据的采集。本文讨论的核心就是CPCI接口的信号采集后插板,通过对PLX9656芯片使用DMA的操作方式,解决了FPGA与PC工控机之间的高速数据传输问题。本板卡主要由电源模块、时钟网络、DDRII高速缓存阵列、CPCI通信单元、FMC子卡接口等单元组成(为了后续的扩展使用,模块还设计了两路高速SFP光模块)。系统原理框图如图1所示。

信号采集板卡系统工作流程:PC工控机通过CPCI总线发送操作指令到信号采集板,板卡上的CPCI接口控制器将上位机发送的指令以桥接的方式传送到FPGA,FPGA接受到指令后,对FMC接口的子卡进行信号采集(由于采样的数据量大、采样率高,这里为每个FPGA设计了2簇32 bit的DDRII缓存阵列),两片FPGA通过虚拟的PCI总线和主控机进行通信(将40对LVDS信号线进行协议转换,达到两片FPGA可以同时和CPCI主机进行通信)。并将采集到的信号通过CPCI总线上传到工控机的磁盘存储阵列上,以便工控机的后续处理。

图1 信号采集板卡系统框图

2 板卡硬件电路的设计

2.1电源模块的设计

在由FPGA、DDRIISDRAM和PLX9656构成的CPCI高速信号采集板卡中,使用电源的种类较多。主要有:DDRIISDRAM需要0.9V和1.8V直流稳压电源;PLX9656需要3.3V直流稳压电源;主控芯片Virtex-5系列FPGA可兼容多种I/O电压,内核和I/O单独供电,内核供电电压为1.0V,FPGA参考电压为2.5 V。DDRIISDRAM用到I/O板块的供电电压为1.8 V,PLX9656用到I/O板块的供电电压为3.3V。板卡由工控机主机供电,输入5V的直流电源,这就需要电源模块对输入电源进行专门的转换和处理才能使用。

图2为FPGA内核电源模块的电路原理图。设计使用的电源模块为TI公司的PTH08T250WAD。该模块作为高性能的降压模块,输入电压范围为4.5 V~14 V,输出电压范围为0.7 V~3.6 V,实际转换效率可以达到96%。在实际的设计中,只需要对Rset偏置电阻进行不同的设置,就可以满足不同电平标准的电压输出。

图2 Virtex 5 FPGA内核电压模块设计电路图

2.2时钟网络的设计和实现

高速信号的采集,对于时钟的要求是非常苛刻的,精度一般要求在百万分之一,这就需要十分精准的晶体振荡器或专用的时钟芯片。同时,由于板卡上集成了两片FPGA,两路FMC子卡接口、以及CPCI桥芯片。为了能够满足各个模块能够协调工作,需要较为合理的对不同模块进行时钟单元的分配。图3为时钟网络设计框图。

图3 CPCI采集板卡时钟网络结构图

设计中使用两片SI530B100高精度时钟单元分别作为两片FPGA的参考时钟。为了满足FPGA同CPCI主机交互通信,需要两者有相同的参考时钟,这里采用了高质量的时钟扇出芯片DS90LV110T,该芯片最多能将单一的输入时钟扇出成10对同频同相的LVDS参考时钟,能够很好的满足设计需求。

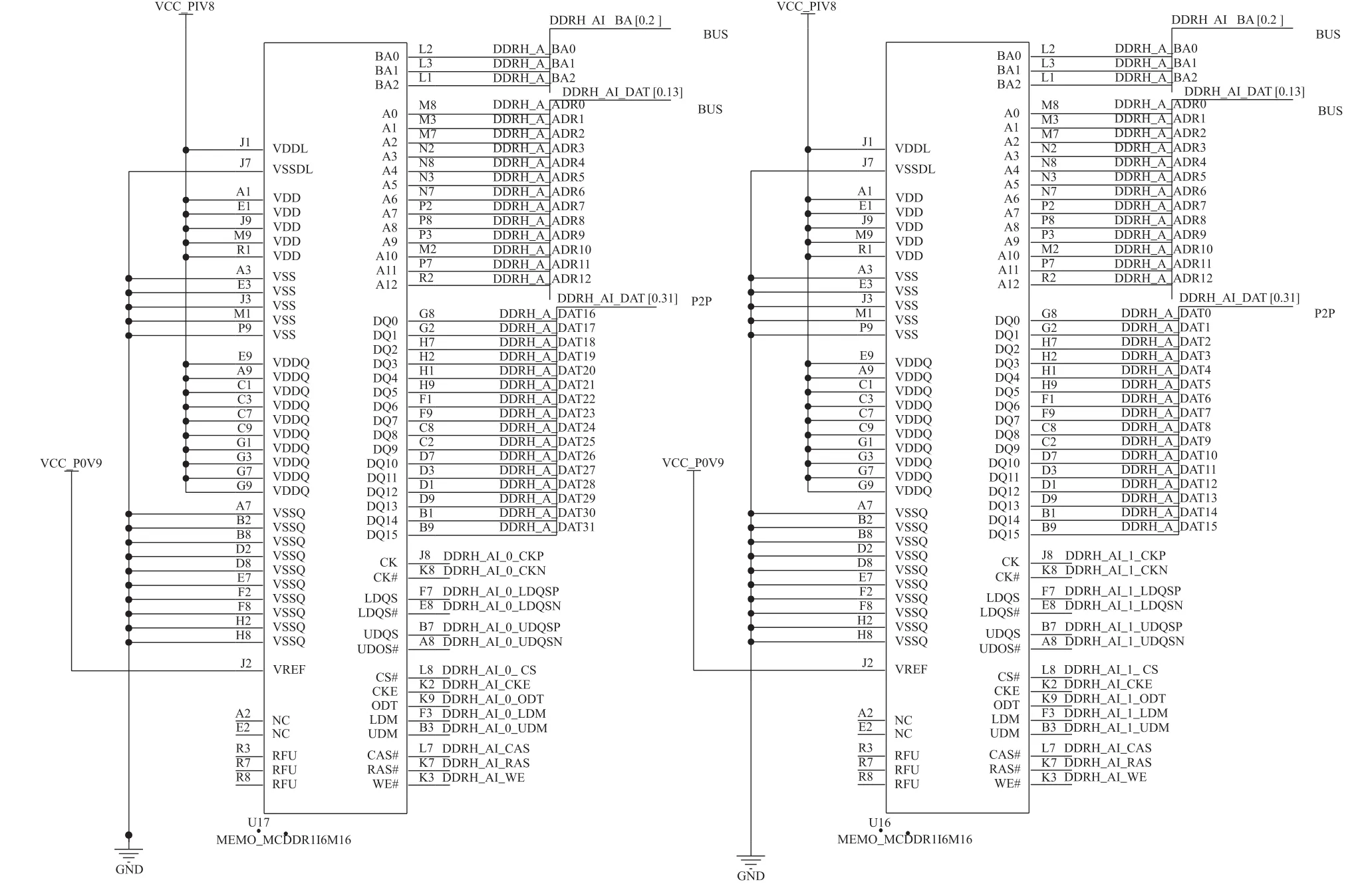

2.3DDRII模块电路的设计

设计一个处理数据能力强、功能复杂的系统,就必须大幅提高系统的工作时钟频率。系统工作频率的提高使得DDRIISDRAM的工作频率也随之变高,更高的工作频率对DDRIISDRAM的工作稳定性提出了更高的要求。DDRIISDRAM比传统的SDRAM和DDR SDRAM有更短的建立时间和保持时间、更准确的参考电压,而且需要合适的匹配终端电阻。图4为两片DDRII组成的一簇32 bit数据位宽的高速缓存单元的原理图。

图4 DDRII高速缓存单元电路设计原理图

在DDRII的设计中,布局布线尤为关键。根据DDRII的工作过程进行分析可知,数据信号线工作在2倍时钟频率下,布线时应优先考虑数据信号线,设计中按照以下顺序进行了布线:数据信号线、地址/命令信号线、控制信号布线、时钟信号线、反馈信号布线。同时,数据信号DQ、数据选通信号DQS和数据屏蔽信号DM长度应不大于25mil。

3 采集板卡各模块的实现过程

3.1PLX9656的DMA方式的设计和实现

PLX9656是PLX公司开发的一款CPCI的桥接芯片,其总线操作包括PCI总线操作和本地总线操作两个部分。在PCI端数据总线可设置为64 bit,本地LOCAL端数据总线为32bit,系统工作时钟可达到66MHz。

PLX9656有3种配置模式,分别为M模式(主要用于Motorola公司的MPC850、MPC860接口)、C模式(地址和数据总线非复用使用)、J模式(地址和数据总线复用)。为了更高效的利用FPGA的逻辑资源,方案使用的是J模式配置。通过该模式可以和IBM公司的PowerPC等设备直接互联。

PLX9656的数据传输分为单周期读/写、突发传输和DMA3种模式。由于板卡传输的信号为高速、大容量数据,所以这里选用DMA操作方式。PLX9656集成了两个相互独立的DMA通道,而且支持硬件EOT/Demend传输模式,对于开发使用非常合适。

为了方便用户的应用程序的开发,PLX公司还为开发者提供了PLX9656芯片相应的驱动开发包:PLX_SDK。其丰富的函数库可以使用户更方便地开发上位机界面程序。

板卡在上电工作时,用DMA方式上传数据的同时将数据存储到大容量硬盘,实现高速数据流持续地在采集卡和硬盘之间传输。

图5为PLX9656的在DMA方式下的仿真时序图。

DMA方式的操作时序为

(1)PXL9656置高LHOLD,申请局部端总线局部逻辑仲裁允许总线申请。

(2)置高LHOLDA,PLX9656送出地址信号,同时ADS变低,LW/R变为低电平,BLAST为高电平,数据在每个时钟的上升沿进行传输。

(3)PLX9656中BLAST信号变低,表示最后一个数据传输完成。

(4)LHOLD变为低电平,放弃对总线的占用,LHOLDA信号随后也变为低电平,将总线的使用权收回。

图5 PLX9656工作在DMA方式下的仿真时序图

3.3DDRIISDRAM乒乓缓存单元设计与仿真

乒乓缓存作为流水线设计的一种数据缓存方法,其实现原理如图6所示。

图6 DDRIISDRAM乒乓缓存结构图

其具体工作流程如下:数据逻辑控制器完成对整个缓存数据的接收和合理化分配,系统上电后,DDRIISDRAM控制器对DDRIISDRAM进行初始化,初始化完成后DDRIISDRAM处于空闲状态,当数据逻辑控制器接收到数据时,片选 DDRII SDRAM1的同时发送写请求,并将数据写入输入数据FIFO中,等待DDRIISDRAM1写应答,DDRII SDRAM1控制器收到写应答后使能读写地址发生器1,发送DDRIISDRAM1的写地址命令,同时开始计数,控制1读取输入FIFO中的数据,将输入数据写入到DDRIISDRAM1中,当达到设定的存储容量时给出DDRIISDRAM1满信号。数据逻辑控制器判断DDRIISDRAM1满标志有效时,使能DDRII SDRAM1读请求,同时使能DDRIISDRAM2写请求,DDRIISDRAM1控制器写地址计数器1清零,等待DDRIISDRAM1读应答,收到应答后使能读写地址发生器1,读取DDRIISDRAM1中的数据送入到存储单元进行存储。当DDRIISDRAM1读取完成后等待DDRIISDRAM2写满,当DDRIISDRAM2写满后将接收到的数据写入到DDRIISDRAM1中,同时读出DDRIISDRAM2中的数据送入到存储单元中进行存储。从外部看输入输出的数据是连续的,能够避免数据丢失,实现数据的无缝缓冲。

图7为乒乓缓存模块在modelsim中的仿真结果。从图中放大后可以看到写入数据的时序,先写入命令到TCFIFO中,然后写入数据。同理,放大后可以看到读出数据的时序,先写入命令到TCFIFO中,等命令解析之后RXFIFO就会接收到读出的数据。

图7 DDRII_module读写时序仿真图

4 总结

本文详细介绍了CPCI高速信号采集板卡的软硬件组成和各功能模块的设计。首先根据电路的需要设计了供电电源,并给出了电路原理图。根据高速信号对时钟信号和电源的苛刻要求,采用专用的高精度时钟晶体SI530提供时钟,并详细说明了整个设备时钟网络的设计;缓存单元采用两片DDRIISDRAM芯片构成乒乓缓存,设计了乒乓缓存的数据流程和操作方法。同时,文中还通过Verilog硬件描述语言对FPGA的CPCI总线接口和DDRII缓存单元进行了仿真分析。图8为设备板卡的实物图,通过实际验证,该板卡能满足设备所需要的各项技术指标。

图8 CPCI信号采集板卡实物图

[1] PLX Technology.PCI9656BA Data Book[S].2011.

[2] 代云启,李智.PCI总线高速连续采集控制逻辑研究[J].国外电子测量技术,2009,28(3):34-37.

[3] 金显峰,邱春玲,田地.嵌入式PCI总线主模式设计[J].计算机测量与控制,2005(8): -.

[4] 李建东.移动通信[M].西安:西安电子科技大学出版社,2010.

[5] 王炜.CPCI总线在北斗信号源中的应用[J].电子测量技术,2009,32(8):126-129.

[6] 陈政平,何玉珠,李建宏.基于PCI总线的电子干扰吊舱自动检测系统研究[J].电子测量技术,2009.

[7] 夏宇闻.Verilog数字系统设计教程[M].北京航空航天大学出版社,2010.

[8] 连红运,屈芳升,王书双.基于PCI总线的超声显微镜研究与设计[J].电子测量与仪器学报,2009,23(4):86-91.

韩朝辉(1989-),男,汉族,山西晋城人,中北大学仪器与电子学院,硕士研究生,主要研究方向为电路与系统,hanzhaohui-1@163.com;

孟令军(1969-),男,通信作者,汉族,山东青岛人,中北大学仪器与电子学院,硕士生导师,副教授,主要研究方向为集成测量系统及仪器、微纳仪器及测试技术。

Design of Signal Acquisition Board Based on CPCI*

HAN Zhaohui1,MENG Lingjun2*,WEN Bo3

(North Uniυersity of China Key Laboratory of instrumentation Science&Dynamic Measurement;Ministry of Education,National Key Laboratory for Electronic MeasurementTechnology,Taiyuan 030051,China)

Based on the relevant technology of CPCIbus and signalacquisition,a CPCIsignal acquisition board design is proposed with the FPGA as the core.The board is composed of a powermodule,a clock network,a DDRII cache array,a CPCI communication unit,a FMC sub card interface,and so on.This paper gives aminute description of the implementation methods of software and hardware boards,and the design idea of the pipeline is put forward,Ithighlights the structure based on ping-pong of the high-speed DDRIIcache array and the design ideas and implementation of CPCIbus.Through experiments,High speed DDRII cache array can achieve the transmission rate of400Mbit/s,PLX9656 can alsowork under the clock of66MHz,and the board hasa high stability.

cpci;signalacquisition;fpga;ddrii;plx9656

TP23

A

1005-9490(2016)04-0851-05

项目来源:基于工业CT固体火箭发动机缺陷定位与分割技术研究项目(61171177)

2015-08-22修改日期:2015-09-26

EEACC:7220;614010.3969/j.issn.1005-9490.2016.04.020