OTP存储器存储单元内寄生电容对读取阈值的影响

2016-09-14毛冬冬曾昆农李建军

毛冬冬,曾昆农,李建军

(电子科技大学 电子薄膜与集成器件国家重点实验室,四川 成都 610054)

OTP存储器存储单元内寄生电容对读取阈值的影响

毛冬冬,曾昆农,李建军

(电子科技大学 电子薄膜与集成器件国家重点实验室,四川 成都610054)

在OTP存储器的设计中,基于得到OTP存储器存储单元编程后尽可能大的读取阈值的目的,以提高OTP存储器的编程效率和芯片成品率,采用了消除存储单元内寄生电容的方法,通过对OTP存储器存储单元内带寄生电容和不带寄生电容两种情况下的仿真以及对比,可以发现存储单元内寄生电容的存在会使OTP存储器编程后的读取阈值减少8 kΩ左右,所以在OTP存储器的设计中,应尽可能消除掉存储单元内的寄生电容,获得尽可能大的读取阈值。

OTP存储器;存储单元;寄生电容;读取阈值

OTP(one time programmable)存储器[1]作为只可以编程一次的非易失性存储器具有集成度高、存取速度快等特点,在航空航天、军工等对抗辐照、保密特性要求很高的领域中,起着不可替代的作用[2]。OTP存储器的种类很多,很多是基于熔丝和反熔丝,本文介绍的OTP存储器基于反熔丝结构[3]。在反熔丝OTP存储器中,通过对选中单元的编程改变了存储单元内部的结构。理想的读机制下,没有编程的存储单元读取时会读出‘0’,而通过编程的存储单元在读取时会读出 ‘1’。反熔丝单元在编程前相当于一个电容,编程后相当于一个电容并上一个电阻,OTP存储器读取阈值的定义就是使读出Data从‘1’变为‘0’时对应的电阻值,编程后电阻如果超出这个值,就无法正确读取‘1’,读操作失效[4]。读取阈值对整个读出电路乃至整个OTP存储器都至关重要。反熔丝存储单元采用的反熔丝结构都会通过大量的测试来得出它击穿后电阻的最大值和最小值,一般情况下,电路设计时要求达到的读取阈值都要比这个最大值大出很多,这是为了防止对反熔丝存储单元编程时由于击穿不充分导致编程后电阻很大,从而无法正常读取‘1’。较大的读取阈值可省去对未成功编程单元的再次编程,大大提高芯片的编程效率以及读出的准确率。然而,在特定情况下,比如采用的存储单元中反熔丝的特殊结构或者出于存储单元内管子耐压的考虑,反熔丝存储单元选通管的漏端节点会有寄生电容,从而对读出阈值造成较大影响,文中通过理论分析及大量仿真(仿真在SMIC 0.5 um工艺仿真库下进行,芯片工作电压为5 V)详细阐明反熔丝存储单元选通管漏端节点的寄生电容对OTP存储器读取阈值的影响。

1 读出系统简介及灵敏放大器功能

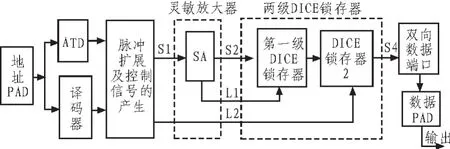

读出系统包括地址PAD输入、地址检测、脉冲扩展、灵敏放大器、第一级DICE锁存器、第二级DICE锁存器、双向数据端口、数据PAD输出。各个模块的连接关系如图1所示。

图1 OTP存储器读出系统框架图Fig.1 The read system frame of the OTP memory

其中,灵敏放大器是整个读出电路的核心,灵敏放大器的简单示意图如图2所示。

图2 灵敏放大器结构示意图Fig.2 The frame of the sense amplifier

INV为关键反相器,其翻转阈值是确保正确读取的关键因素。反相器的翻转阈值定义为Vin=Vout点的电压值,此VDS= VGS时,P管和N管均处于饱和状态。假设电源电压足够高且两个器件都在速度饱和的状态下(VDsat<VM-VT),再忽略沟道调制效应可得到一个反相器翻转阈值的简化公式(2):其中WP和WN分别是反相器P管和N管的宽长比。

图2中P1为预充电管,开启时对位线进行充电[5],此间放电管N1关闭,位线通过选中的存储单元放电,P1管起始时工作在饱和区,饱和电流IDsat为:

BL是位线,本文中位线共挂有256个负载,包括一个选中的要进行读取的存储单元还有255个未被选中的作为负载的存储单元,所以一根位线上总的负载电容为选中单元的电容并上255个负载单元的电容。总电容为:

选中的存储单元中,C1是反熔丝;C2是选通管漏端节点寄生的电容,文中主要就是研究该寄生电容对读取阈值的影响;N4、N5为选通管,处于开启状态。未选中的存储单元中选通管N4、N5处于关闭状态。

反熔丝编程前等效于一个电容,本文中其大小为4 F,编程后等效于电容并上一个电阻,如图3所示。

图3 编程前、后存储单元的结构图Fig.3 The structure of the un-programmed and programmed anti-fuse

位线充电后通过选中单元放电[6],现在分别对未编程和已编程(将R取为3 kΩ,假设电路设计要求读出阈值至少为3 kΩ)这两种情况进行仿真(未特殊注明下,仿真均在TT工艺角、27℃下进行),得出位线放电的情况,进而说明灵敏放大器的工作原理。

图4 编程前、后位线放电图Fig.4 The discharge of the bit line with un-programmed and programmed anti-fuse

图4中3个信号线从上到下依次是充电信号、放电信号和位线。可见位线经过未编程的存储单元放电到3.492 V,经过已编程的存储单元则放电到2.528 V。关键反相器的翻转阈值是确保正确读取数据的关键因素,如果电路设计要求的读出阈值至少为3 kΩ(读取阈值可能大于3 kΩ),则反相器的翻转阈值必须处于2.529 V和3.492 V之间,才能确保灵敏放大器可以准确无误的读取‘0’和‘1’。翻转阈值最好能够处于两个电平的平均值左右,比如3 V左右,这样对于编程和未编程的存储单元都有足够的余量,才能最大限度的确保各种工艺角和温度下读出数据的准确性。

2 寄生电容对位线放电的影响

很多情况下,存储单元内选通管N4、N5的漏端节点会有寄生电容,比如现采用的反熔丝结构的编程电压在10 V左右,而N4、N5漏端耐压的典型值为11 V,由于比较接近,为了提高可靠性,需要对N4、N5漏端进行低掺杂处理,提高其耐压值[7],如图5所示。

图5 选通管漏端低掺杂示意图Fig.5 The sketch map of low doping for the drain of the choosing transistor

这样低掺杂和P衬底间就会产生寄生电容,寄生电容C为:

其中,C0是单位结面积上的电容值,S是寄生PN结的结面积,a、b、c分别为结长、结宽、结深,S近似为5个结面的面积和。经过计算其最大值为13.3 F,这里就将C2取为13.3 F,现对未编程存储单元在带寄生电容和不带寄生电容这两种情况下进行仿真,从而观察寄生电容对位线放电的影响。

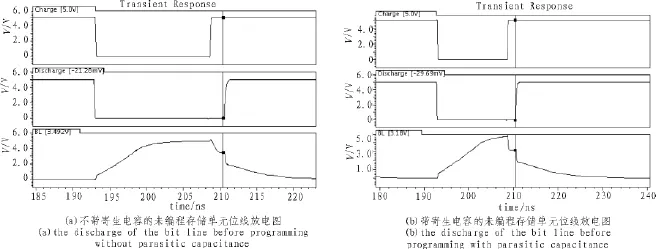

位线放电结果如图7所示。

图中3个信号线从上到下依次是充电信号、放电信号和位线。可见在存在寄生电容的情况下,位线通过存储单元放到更低的电位,从3.492 V降到了3.18 V。此种情况下,为了得到反相器翻转阈值和3.18 V之间充足的余量,以保证各种工艺角和温度下未编程存储单元能够正确读取‘0’,就需要降低反相器的翻转阈值,进而就会影响到电路的读取阈值。

图6 未编程存储单元带和不带寄生电容位线放电的仿真图Fig.6 The discharge of the bit line before programming with and without parasitic capacitance

3 寄生电容对OTP存储器读取阈值的影响

由于寄生电容的存在,会使位线放到更低的电位,此时为了保证未编程存储单元能够正确读取‘0’,就需要对关键反相器的翻转阈值进行调整。

通过对未编程存储单元在15种不同温度和工艺角下的仿真,最终将关键反相器的翻转阈值定在2.77 V,倘若翻转阈值高于2.77 V,未编程存储单元在SF工艺角、150℃这种条件下将最先不能正常读取,会将原本要读出的 ‘0’读成‘1’,这种情况下的仿真结果如图7所示,五个信号线从上到下依次是充电信号、放电信号、位线、第二级锁存信号、Data输出。注意数据Data的每次读取是在第二级锁存信号Lock2结束后才读取的,可见读出结果是‘1’。

将关键反相器的翻转阈值设为2.77 V后,未编程存储单元在不同工艺角和温度下的读取结果都是‘0’,可见可以正确读取。

图7 SF工艺角、150摄氏度下未编程单元读取的仿真图Fig.7 The reading simulation of the un-programmed bit line under SF section and 150 degree centigrade

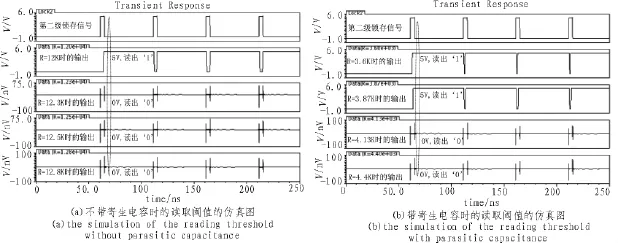

在确定好关键反相器的翻转阈值之后,将在存储单元内没有寄生电容和有寄生电容这两种情况下对电路的读取阈值进行仿真,从而观察寄生电容对读取阈值的影响。具体做法是将反熔丝存储单元编程后的电阻值设为变量R,然后对其进行扫描,观察读出Data的值,由于存储单元编程后正确读取时是读出 ‘1’,所以读出Data从‘1’变为‘0’所对应的R值就是所要的电路的读取阈值。两种情况下的仿真结果如图8所示。

图8 寄生电容对读取阈值影响的仿真图Fig.8 The simulation of the influence of the parasitic capacitance on the reading threshold

观察图中的两个图可以看到反熔丝存储单元中寄生电容对电路读取阈值的影响,注意Data的读取是发生在第二级锁存信号结束后。A图为存储单元没有寄生电容时的仿真结果,从上到下的5个信号分别是第二级锁存器的锁存信号、R=12 kΩ时Data的输出、R=12.3 kΩ时Data的输出、R= 12.5 kΩ时Data的输出、R=12.8 kΩ时Data的输出,可见R= 12 kΩ时读出的是‘1’,说明电路的读取阈值可以达到12 kΩ,R=12.3 kΩ时读出的是 ‘0’,说明电路的读取阈值达不到12.3 kΩ,所以存储单元没有寄生电容时电路的读取阈值在12.1 kΩ左右。B图为存储单元有寄生电容时的仿真结果,从上到下的五个信号分别是第二级锁存器的锁存信号、R= 3.6 kΩ时 Data的输出、R=3.87 kΩ时 Data的输出、R= 4.13 kΩ时Data的输出、R=4.4 kΩ时Data的输出,可见R= 3.87 kΩ时读出的是 ‘1’,说明电路的读取阈值可以达到3.87 kΩ,R=4.13 kΩ时读出的是‘0’,说明电路的读取阈值达不到4.13 kΩ,所以存储单元存在寄生电容时电路的读取阈值在4 kΩ左右。

这充分说明了反熔丝存储单元内寄生电容对电路读取阈值的影响,寄生电容的存在使电路的读取阈值大概从12 kΩ减到了4 kΩ。倘若编程时反熔丝存储单元击穿的不充分,导致编程后电阻在4 kΩ到12 kΩ之间的话,便不能正常读出‘1’,这就需要对这些编程不充分的存储单元进行二次编程,这将大大降低我们的编程效率,给OTP存储器用户带来很大的不便。所以本文中通过略微降低编程电压的方法省去了对选通管漏端进行低掺杂这一环节,从而消除了寄生电容,最大程度保证了存储器的读取阈值。可见消除反熔丝存储单元内的寄生电容至关重要,这可以最大程度的保证OTP存储器的读取阈值,提高编程效率,提高芯片成品率。

4 结束语

理论分析及仿真表明,OTP存储器反熔丝存储单元内寄生电容的存在将使灵敏放大器中的位线放到更低的电位,为了保证未编程存储单元的正确读取,将不得不调低灵敏放大器中关键反相器的翻转阈值,这就会大大降低OTP存储器的读取阈值,从而降低编程效率,给芯片使用者带来不便,所以要尽量消除存储单元内寄生电容的影响,就像本文中通过略微调低编程电压,消除存储单元内的寄生电容,达到设计要求。

[1]F.Li et al.,"Evaluation of Si02 antifuse in a 3D-OTP memory,"IEEE Transactions on Device and Materials Reliability,2004,4(3):416-421.

[2]黄科杰.基于标准CMOS工艺的非易失性存储器的研究[D].杭州:浙江大学,2006.

[3]焦俊陶.反熔丝型存储器设计技术研究[D].成都:电子科技大学,2011.

[4]YANG B-D,KIM L-S.A low-power ROM using single charge-sharing capacitor and hierarchical bit line[J].IEEE Transactions on Very Large Scale Integration Systems,2006,14(4):313-322.

[5]张效通,万青,陈岚,等.一种高速自控预充电灵敏放大器的设计[J].微电子学,2009,39(6):815-818.

[6]王艺燃,于宗光.一种应用于DPS嵌入式存储器的灵敏放大器设计[J].微电子学,2010,40(2):212-216.

[7]李彦旭,巴大志,成立.静态存储单元电路设计工艺的研究[J].电子元件与材料,2002(12):13-16.

Influence of parasitic capacitance upon the reading threshold of OTP memory

MAO Dong-dong,ZENG Kun-nong,LI Jian-jun

(State Key Laboratory of Electronic Thin Films and Integrated Devices,University of Electronic Science and Technology of China,Chengdu 610054,China)

To obtain the largest reading threshold of the programmed one time programmable memory during the design of the one time programmable memory,this paper takes the method of eliminating the parasitic capacitance in the memory cell.By the simulation and comparison of the reading threshold with and without the parasitic capacitance,this paper finds out that the existence of the parasitic capacitance leads to the decrease of the reading threshold about 8k ohm.So the designer should eliminate the parasitic capacitance in the memory cell to get the largest reading threshold during the design.

one time programmable memory;memory cell;parasitic capacitance;reading threshold

TN432

A

1674-6236(2016)02-0082-04

2015-07-29稿件编号:201507187

国家自然科学基金项目(61404021)

毛冬冬(1990—),男,河南开封人,硕士研究生。研究方向:大规模数字集成电路。