基于MSl的数字时钟的电路设计

2016-08-31黑龙江大学150080

郑 旭(黑龙江大学,150080)

基于MSl的数字时钟的电路设计

郑 旭

(黑龙江大学,150080)

数字时钟的特点是以数字显示秒、分、时,它是一种相较于传统机械时钟更准确、更直观的时钟装置,数字时钟也不需要机械传动装置,所以被广泛使用。在日常生活中我们随处可见数字时钟,数字电子钟以两种方式实现:单片机控制,数字集成电路构成。本次设计是由数字集成电路构成的数字电子时钟。

MSI;数字时钟;电路设计

1 数字时钟设计功能要求

该设计的电子钟应该能够准确计时,并将时间以数字形式显示。在电路中,可以利用NE55振荡电路提供的脉冲信号。同时在计时出现误差时电路还可以完成校时、校分和校秒功能。具体要求如下:

(1)用NE555芯片产生时钟脉冲;

(2)用数码管显示时间数字;

(3)数码管显示时、分、秒;

(4)具有校时功能。

2 设计方案

2.1方案概述

此次设计的电子钟电路主要由以下几部分组成:脉冲基准电路,计数器,译码器,时钟显示数码管,校时器。

(1)脉冲基准电路:它是数字钟的核心,由它产生时间基准源信号,提供给计数器,它的精确度决定了时间的精准。

(2)计数器:对基准信号进行计数。

(3)译码器:将计数器的输出转换成数码管的驱动信号。

(4)时钟显示:将经过译码的数字显示出来。

(5)校时器:调整时钟的时间。

本数字钟的工作原理如下:

由NE555电路产生1Hz的脉冲信号作为时间基准,提供给计数器计数,当秒计数器达满60的时候向分计数器进位,并且秒计数器清零,当分钟计数器达满60的时候向时计数器进位,并且分钟计数器清零,当时计数器满24的时候时计数器清零。当时间与现实时间出现误差的时候可以通过校时器进行校时。

2.2方案设计

2.2.1脉冲基准电路设计

本次设计采用NE55与电容电阻组成的多谐振荡电路来产生1Hz的脉冲信号输送给计数器。

NE555(Timer IC)为8脚时基集成电路,它只需简单的电阻器、电容器,即可完成特定的振荡延时作用。其延时范围极广,可由几微秒至几小时之久;.它的操作电源范围极大,可与TTL,CMOS等逻辑电路配合,也就是它的输出电平及输入触发电平,均能与这些系列逻辑电路的高、低电平匹配;其输出端的供给电流大,可直接推动多种自动控制的负载;它的计时精确度高、温度稳定度佳,且价格便宜。

NE555管脚介绍:

Pin 1 (接地) -地线(或共同接地) ,通常被连接到电路共同接地。

Pin 2 (触发点) -这个脚位是触发NE555使其启动它的时间周期。触发信号上缘电压须大于2/3 VCC,下缘须低于1/3 VCC 。

Pin 3 (输出) -当时间周期开始555的输出脚位,移至比电源电压少1.7伏的高电位。周期的结束输出回到0伏左右的低电位。于高电位时的最大输出电流大约200 mA 。

Pin 4 (重置) -一个低逻辑电位送至这个脚位时会重置定时器和使输出回到一个低电位。它通常被接到正电源或忽略不用。

Pin 5 (控制) -这个接脚准许由外部电压改变触发和闸限电压。当计时器经营在稳定或振荡的运作方式下,这输入能用来改变或调整输出频率。

Pin 6 (重置锁定) - Pin 6重置锁定并使输出呈低态。当这个接脚的电压从1/3 VCC电压以下移至2/3 VCC以上时启动这个动作。

Pin 7 (放电) -这个接脚和主要的输出接脚有相同的电流输出能力,当输出为ON时为LOW,对地为低阻抗,当输出为OFF时为HIGH,对地为高阻抗。

Pin 8 (V +) -这是555个计时器IC的正电源电压端。供应电压的范围是+4.5伏特(最小值)至+16伏特(最大值)。

根据NE555内部管脚图和所设计的NE555外部电路可知,C1是外接定时电容,R1、R3是充电电阻,并且R3又是放电电阻。C2用于防干扰。接通电源后,电源通过电阻对C充电,充电至当Thold=2/3的Vcc时, A1输出为1,比较器A2输出高电平,输出端3输出低电平,放电三极管T导通,电容C又要通过R2、T放电,Vcc下降,当Vcc下降至1/3Ucc时,VT截止,C又重新充电,以后恢复以上过程。其震荡周期为:

在实验的时候选择1M的电阻为R1、R3,由公式可以计算出电容。

2.2.2计数器电路设计

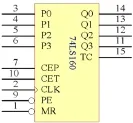

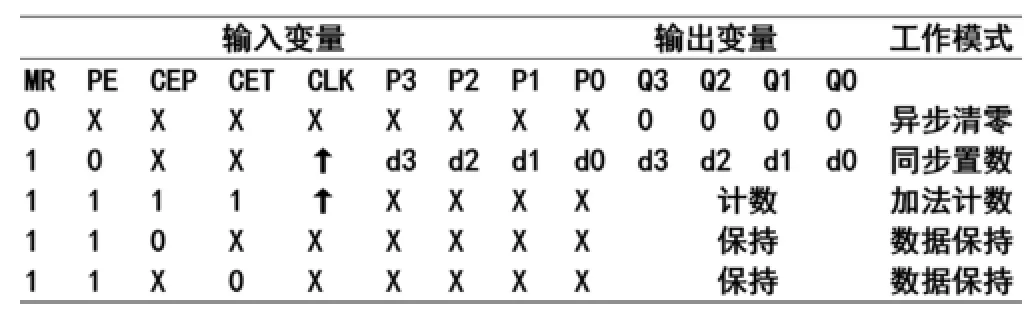

本设计时分秒的计数器选用十进制计数器74LS160。按照时间显示的要求,秒的个位部分为逢十进一,十位部分为逢六进一,从而共同完成60进制计数器。74LS160实现60进制的方式有两种:异步清零、同步置数。它的引脚图如图3所示,工作真值如表1所示:

图3 74LS160的引脚图

表1 74LS160工作真值表

秒计数器的个位和十位由两个74LS160芯片组成,个位的74LS160计数范围为0~9,因此将个位的74LS160计数器计满十的时候的进位作为十位的计数器的计数信号,即将个位的74LS160的TC脚接到十位的74LS160的7脚和10脚,将秒的时钟信号接到十位的74LS160的2脚CLK上,当个位的74LS160产生进位的时候十位的7脚和10脚为1,其处于加法技术的工作模式下,在时钟高电平脉冲的作用下,十位的计数器74LS160计数加1。因此通过此种方式对秒计数器的十位进行计数。

2.2.3时钟显示电路设计

本设计中计数器的输出为BCD码,需选用一个译码器来实现数字的显示,这里选用74ls47 bcd译码器。74LS47是BCD-7段数码管译码器/驱动器,74LS47的功能用于将BCD码转化成数码块中的数字,通过它解码,可以直接把数字转换为数码管的显示数字。74LS47是输出低电平有效的七段字形译码器,与它配合的是共阳七段数码管,因为共阳数码管直接与电源相连因此在数码管的输入与74LS47输出之间应该并联330欧的电阻来进行限流。

2.2.4校时器电路设计

在校时的时候我们必须模拟一个时钟信号来时计数器进行加1计数,在校时的时候为了防止我们模拟的时钟信号与正在运行的各个计数器系统的CLK信号发生冲突,因此在校时的时候应该断开时钟信号的输入,此时可以将NE555产生脉冲和校时设置按键的信号进行相与,当校时按键按下的时候,与电路输出0时秒计数器停止运行。本设计的与门采用四2输入与门芯片74ls09。

当进行校时的时候按键被按下74LS09的12脚接地为0,因此不管时钟脉冲为什么电平,74LS09的11脚输出都为0,因此这种情况下可以屏蔽时钟脉冲,为了防止在未按下校时按钮的时候,按了三个时分秒其中的一个修改按键对,时钟的时间产生影响,因此在校时按钮未被按下的时候三个时分秒三个按键必须是失效,因此可以采用74ls09的一个与门来实现屏蔽在正常模式下,时分秒三个按键被误按下时对时钟工作的影响。

3 结语

本次设计了一个数字集成电路构成的数字电子钟,设计的电子钟主要由下面这几部分电路组成:脉冲基准电路、计数器电路、译码器电路、时钟显示数码管电路、校时器电路,实现了数字钟显示时间、计数、校时等功能。

[1]康华光.电子技术基础.数字部分 北京:高等教育出版社,2000

[2]陈坚.电力电子学[M].北京:高等教育出版社,2002

[3]高吉祥.电子技术基础实验与课程设计.电子工业出版社,2002

Circuit design of digital clock based on MSI

Zheng Xu

(Heilongjiang University,150080)

In daily life,we can see the digital clock,digital clock in two ways:single chip microcomputer control,digital integrated circuit.The design is a digital electronic clock which is made up of digital integrated circuits.

MSI;digital clock;circuit design