基于FPGA的高速AD7903驱动设计与实现

2016-06-18合肥工业大学仪器科学与光电工程学院安徽合肥230009

苏 锐 合肥工业大学 仪器科学与光电工程学院 安徽合肥 230009

基于FPGA的高速AD7903驱动设计与实现

苏 锐 合肥工业大学 仪器科学与光电工程学院 安徽合肥 230009

【文章摘要】

高速AD采集目前在激光干涉位移测量中起到重要作用,AD采集的速度以及分辨率直接决定了干涉测量的分辨率。本文设计了一种基于FPGA驱动的高速AD7903采集系统,包括硬件以及软件设计,并最终对采样数据进行比较,通用性较强。

【关键词】

AD7903;高速采集;FP

引言

随着电子技术发展,高速数据采集系统对科学研究以及工业生产有着重要的作用,其中高速AD就是实现数据采集的主要方式之一。本文使用全差分双通道AD7903实现数模转换,该芯片最高采样率1Msp,采用串行数据接口,FPGA提供采样时序控制。在设计过程中,首先使用Modelsim仿真,之后在硬件平台实测,使用singal tap观测采集的数据。

1 系统硬件设计

AD7903是一款全差分双通道的高速AD,内部2个ADC采用单电源(VDDX)供电。整个AD外围电路包括前端运放驱动,参考电压输入,电源模块以及AD7903。其中前端运放选用的是ADA4941,参考电压选用的是ADR435,图1是设计的电路前置运放部分的原理图,主要是为了将单端信号输入变成差分信号给后端AD使用,电阻取值可以按照信号输入范围来确定,本文中信号Vpp=10V,差分信号范围是0~5V,具体可参考ADI公司的CN0032电路笔记。

图1 电路前置运放部分原理图

图2 3线无繁忙模式时序

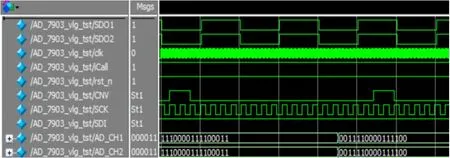

图3 modelsim仿真时序图

2 AD7903控制时序设计

AD7903是一款集成多功能串行端口接口(SPI)的器件,并且在使用独立电源VIOx时,与1.8V、2.5V、3.3V以及5V逻辑电平兼容,本设计采用的是3.3V逻辑电平,VIOx接入的是3.3V。工作模式有CS以及链模式2种,本文程序控制使用的是3线无繁忙指示CS模式,使用的是Verilog硬件语言。图2是3线无繁忙接口时序。

以下是产生CNV,SCK时序部分的Verilog Code

此种模式下,SDI=1,主要控制CNV以及SCK,SCK下降沿依次从SDO读取数据。图3是modelsim仿真时序图。

3 AD7903采集测试结果

将综合完成的Verilog代码在JTAG模式下写入FPGA开发板中,在输入直流电压3V时,使用Singal tap查看AD7903的数据采集情况,如图4所示。

图4 Singal tap 数据采集

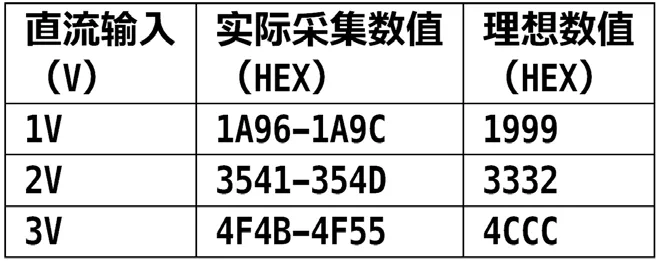

表1是Vref=5V情况下不同直流输入采集的数据。

表1 AD7903直流电平采集数据结果

4 结论

本文基于FPGA设计了AD7903高速AD的采集系统,涵盖硬件电路以及软件编写,并最终给出了modelsim下的仿真结果以及实际测试的AD采集数据。同时最终的实验数据表明,整个设计方案有效,且调试灵活,适用范围广。

【参考文献】

[1]何乐年,王忆.模拟集成电路设计与仿真[M].北京:科学出版社,2010

[2]夏宇闻编著. Verilog数字系统设计教程[M].北京航空航天大学出版社,2003

[3]http://www.analog.com/media/cn/ technical-documentation/data-sheets/ AD7903_cn.