不同栅压应力下1.8V pMOS热载流子退化机理研究

2016-05-31刘斯扬于朝辉张春伟孙伟锋张爱军刘玉伟吴世利何骁伟

刘斯扬,于朝辉,张春伟,孙伟锋,苏 巍,张爱军,刘玉伟,吴世利,何骁伟

(1.东南大学国家专用集成电路系统工程技术研究中心,江苏南京210096; 2.华润上华半导体有限公司,江苏无锡214000)

不同栅压应力下1.8V pMOS热载流子退化机理研究

刘斯扬1,于朝辉1,张春伟1,孙伟锋1,苏巍2,张爱军2,刘玉伟2,吴世利2,何骁伟2

(1.东南大学国家专用集成电路系统工程技术研究中心,江苏南京210096; 2.华润上华半导体有限公司,江苏无锡214000)

摘要:本文详细研究了不同栅压应力下1.8V pMOS器件的热载流子退化机理.研究结果表明,随着栅压应力增加,电子注入机制逐渐转化为空穴注入机制,使得pMOS漏极饱和电流(Idsat)、漏极线性电流(Idlin)及阈值电压(Vth)等性能参数退化量逐渐增加,但在Vgs=90%* Vds时,因为没有载流子注入栅氧层,使得退化趋势出现转折.此外,研究还发现,界面态位于耗尽区时对空穴迁移率的影响小于其位于非耗尽区时的影响,致使正向Idsat退化小于反向Idsat退化,然而,正反向Idlin退化却相同,这是因为Idlin状态下器件整个沟道区均处于非耗尽状态.

关键词:热载流子;不同栅压应力;正反向退化

1 引言

随着器件尺寸不断缩小,电源电压并未随之等比减小,这就导致沟道区的横向和纵向电场显著增加[1,2].强电场使小尺寸器件的热载流子效应非常严重,制约了电路的可靠性和寿命.n型金属氧化物半导体晶体管(nMOS)因其热载流子效应严重而得到了广泛的研究,而p型金属氧化物半导体晶体管(pMOS)因其热载流子效应相对较弱而被人们所忽视.但是随着器件尺寸减小,pMOS器件的热载流子退化已经严重影响了器件和芯片的寿命[3~5],所以,需要对小尺寸pMOS器件的热载流子效应有更多的关注和研究.

目前,对pMOS器件热载流子效应的研究多关注于某一应力情况下pMOS热载流子退化机理及其退化模型的研究[6~10],尚未有关于pMOS器件热载流子退化的系统性研究.本文系统性的研究了1.8V低压pMOS在不同栅压应力下的热载流子退化机理,并解释了造成不同栅压应力下热载流子退化现象不同的原因;此外,对pMOS在高栅压应力下正反向漏极饱和电流(Idsat)和漏极线性电流(Idlin)的特殊退化趋势进行了研究.本文的研究为小尺寸pMOS器件热载流子可靠性寿命模型的研究也提供了支持和参考.

2 实验说明

本文中所研究的器件为带有LDD(Lightly Doped Drain)的1.8V pMOS,其剖面示意图如图1所示.该器件的阈值电压(Vth)为-0.7V,工作时的漏源电压(Vds)和栅源电压(Vgs)均为-1.8V,关态击穿电压(BV)为-4V.实验中固定器件漏端加速应力电压为Vds= -2.8V,从低栅压到高栅压选取不同的栅压应力(Vgs= -1.15V、-1.3V、-1.5V、-1.7V、-2V、-2.2V、-2.4V、-2.5V、-2.6V、-2.7V、-2.8V)来研究该器件不同栅压应力下的热载流子退化情况.应力过程中对器件的正反向漏极饱和电流Idsat(测试条件为Vds= Vgs=-1.8V)、正反向线性电流Idlin(测试条件为Vds= -0.1V,Vgs=-1.8V)及阈值电压Vth(在Vds=-0.1V条件下根据最大跨导法提取得到)的退化情况进行了监测.需要说明的是上述反向电流指pMOS源漏互换后所检测到的漏极电流.

3 不同栅压应力时pMOS退化机理研究

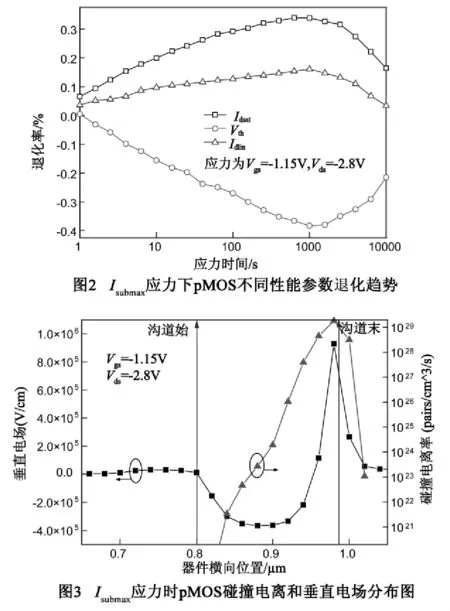

最大衬底电流应力下(Vgs=-1.15V,Isubmax),pMOS 的Idsat、Idlin及Vth退化情况如图2所示.可以看出,Idsat、Idlin随着时间的增加先增加后减小,而Vth绝对值却随着时间的增加先减小后增加.

为了研究pMOS在Isubmax条件下的退化机理,采用Sentaurus软件对pMOS器件表面的碰撞电离率和垂直电场进行了仿真.图3为pMOS在Isubmax应力时器件表面碰撞电离分布和垂直电场分布情况.从仿真结果可以看出,沟道末端的碰撞电离率最大,且其垂直电场方向为正(电场指向器件体内).强碰撞电离产生的具有高能量的热电子,在垂直电场的作用下注入栅氧化层并被电荷陷阱俘获,从而导致在应力初始阶段Vth绝对值减小,且因为注入的热电子在栅氧下方感应空穴,增加了空穴浓度,结果使得Idsat和Idlin增加.然而,随着注入到氧化层中热电子的积累,陷阱电荷势垒随之增大,阻止了电子的进一步注入,注入量呈现饱和趋势,这解释了Vth、Idsat和Idlin的退化在一定时间后开始饱和的现象.再者,在沟道末端的强碰撞电离区内界面态随着应力时间的增加而不断增加,最终会主导器件的退化,而界面态提高了空穴散射概率,降低了空穴迁移率,Idsat和Idlin会逐渐减小,同时显正电性的界面态使Vth绝对值增加.注入电子与界面态相反的作用效果,使得pMOS在Isubmax应力时表现出较小的退化量.

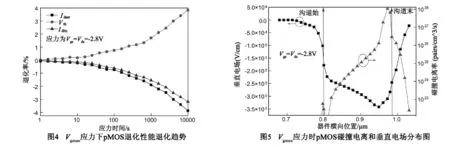

最大栅压应力下(Vgs=-2.8V,Vgmax),pMOS的Idsat、Idlin和Vth的退化情况如图4所示.可以看出,与Isubmax应力下退化趋势不同的是,Idsat和Idlin随时间逐渐减小,而Vth绝对值随时间逐渐增加.

图5为Vgmax应力下pMOS器件表面碰撞电离分布和垂直电场分布图.pMOS沟道末端因碰撞电离较大,为主要退化区域.在此区域内,有利的纵向电场方向使得热空穴注入栅氧化层,造成参数Idsat、Idlin减小而Vth绝对值增加.这与界面态对三个参数的作用效果相同,两种机制相叠加,以致使Idsat、Idlin和Vth退化更加严重.

其余不同栅压下pMOS不同参数的退化趋势如图6、7所示.从图中可以看出,pMOS器件Idsat和Idlin退化量均随着栅压的增大而增大,但是在Vgs=-2.5V时出现了一个小的转折.

根据前面的分析我们知道,低栅压应力下pMOS退化量小是因为电子注入表现出与界面态相反的作用效果,高栅压应力下pMOS退化量大是因为空穴注入表现出与界面态相同的作用效果.所以电荷注入(纵向电场方向的变化)是引起退化变化的主要原因,如图8所示,我们仿真了不同栅压下的电场,得出纵向电场随栅压的增加而逐渐由指向体内转变为指向栅氧层,在Vgs=-2.5V时纵向电场几乎为零.

由前面分析可知,在低栅压时器件沟道末端存在热电子注入栅氧化层,随着栅压的增加,正向的垂直电场强度逐渐减弱,从而电子注入逐渐减少,当Vgs= -2.5V时,垂直电场强度很小,载流子注入可以忽略,退化主要来自界面态的影响.考虑到衬底电流Isub的大小可反映器件碰撞电离率的大小,由图9所示的Isub-Vgs曲线可以看出,Vgs=-2.4V时的碰撞电离率大于Vgs=-2.5V时的碰撞电离率,所以前者中界面态产生量大于后者,则前者电流退化量应大于后者,这与图6、7中退化现象相符,即Vgs=-2.4 V的Idsat和Idlin退化量大于Vgs=-2.5V时的退化量.随着栅压继续增加到-2.6V,碰撞电离率继续减小,垂直电场向负向变化,使空穴注入栅氧层,并与界面态的作用相叠加,使得Vgs=-2.6V时Idsat和Idlin退化量大于Vgs=-2.5V时电流退化量,从而出现Vgs=-2.5V时的退化转折现象.

4 电流正反向退化讨论

pMOS器件是对称结构的,它经常会工作于双向导通模式,因此对器件正反向电参数热载流子退化的研究显得尤为重要.这里我们选择了器件电流能力作为研究对象.

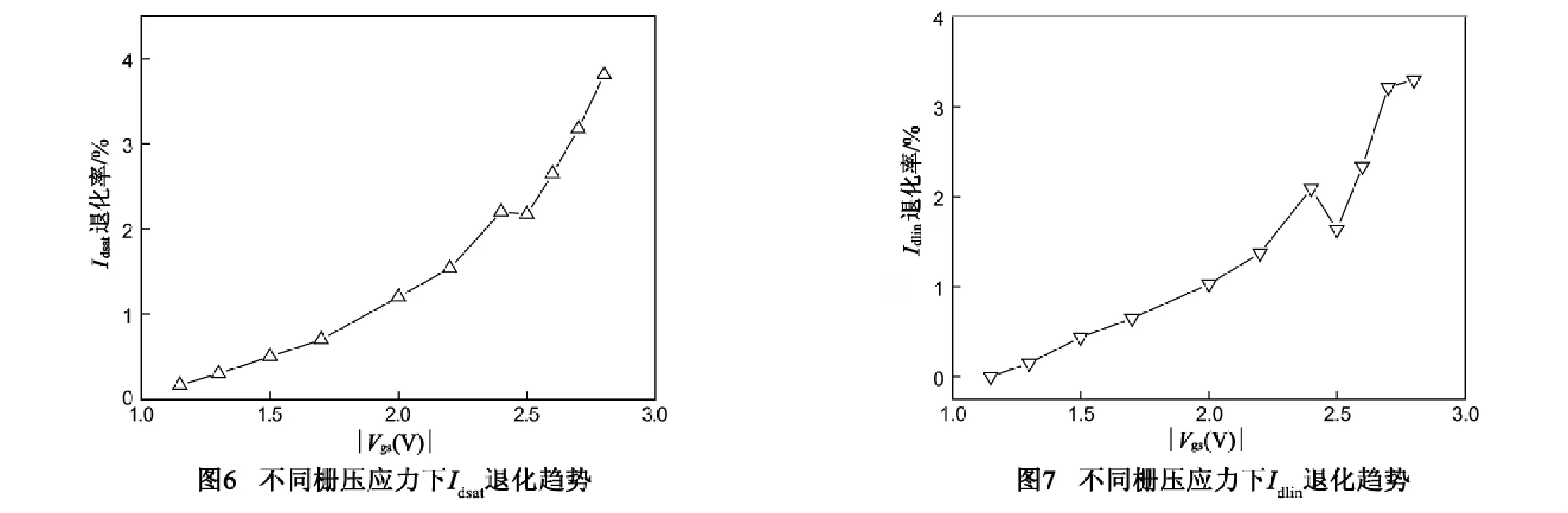

实验过程中我们发现,器件的反向Idsat退化比正向Idsat退化大,而反向Idlin的退化与正向Idlin退化相同.以Vgmax条件下的退化为例,其退化结果如图10和图11所示.应力退化实验过程中监测正反向Idsat和Idlin退化情况,可见,反向Idsat比正向Idsat退化严重,而反向Idlin与正向Idlin退化相同.

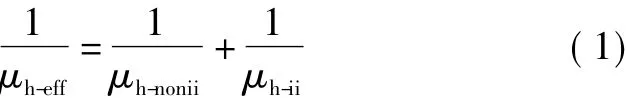

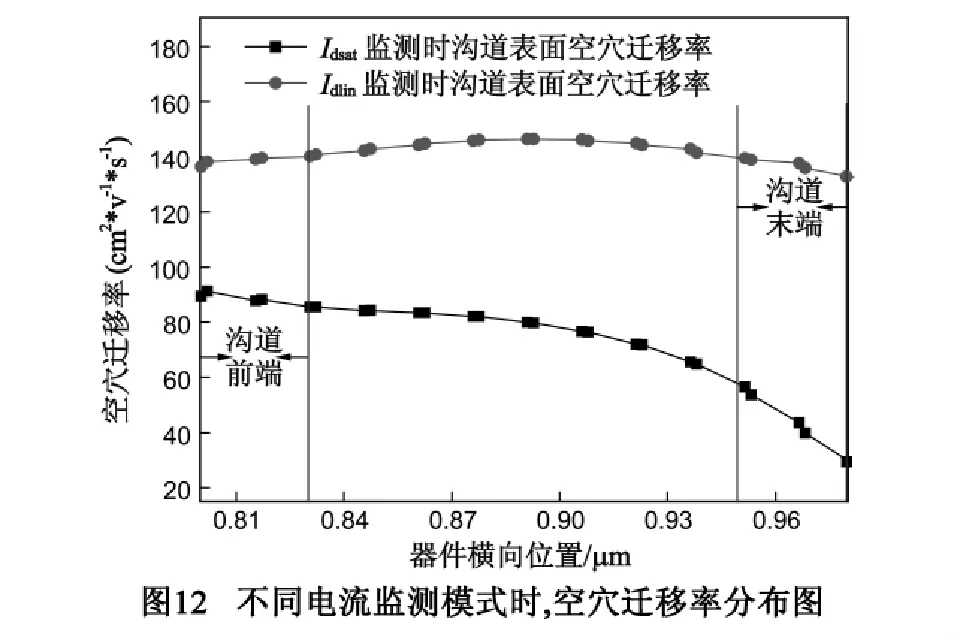

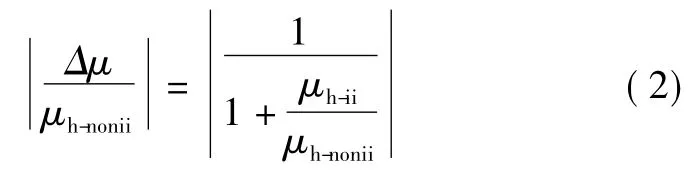

为了理解上述退化现象,我们对Idsat和Idlin两种模式时整个沟道内的空穴迁移率进行了仿真,结果如图12所示.

空穴有效迁移率因热载流子效应而发生变化,根据散射概率叠加的原理,沟道末端存在界面态后空穴的最终有效迁移率可表示为:

其中μh-eff为空穴最终有效迁移率,μh-nonii为空穴未受界面态影响的原始效迁移率,μh-ii为受界面态影响的空穴迁移率.

则由于界面态,空穴有效迁移率的变化百分比为:

根据式(2)我们知道,空穴原有效迁移率μh-nonii越大,其最终有效迁移率μh-eff就越容易受界面态影响.由图12可知,正向Idsat监测模式时沟道前端(如图1所示,靠近源端的一侧)的空穴迁移率大于沟道末端(靠近漏端一侧)空穴迁移率较多,且我们知道Idsat正向监测模式时,界面态位于沟道末端,Idsat反向监测模式时,界面态相当于位于沟道前端(反向监测时器件源极,漏极,沟道前端和沟道未端的位置不变),所以,界面态对反向Idsat影响较为严重,导致器件的反向Idsat退化较为严重.然而在Idlin条件下,整个沟道内空穴的迁移率变化不大,所以界面态对其影响程度相同,以致使正反向Idlin退化几乎相同.

5 结论

本文详细研究了不同栅压应力条件下1.8V pMOS热载流子退化,研究发现pMOS在Isubmax应力下沟道末端存在具有相反作用效果的热电子注入与界面态产生两种机制,导致器件退化量较小;在Vgmax应力下,空穴注入与界面态作用效果相叠加使得pMOS退化量较大.随着栅压的增加,注入电荷发生变化,pMOS的退化量逐渐增加,但在Vgs=-2.5V时因可以忽略载流子注入造成的影响,器件退化出现转折.此外,研究还发现,由于界面态对非夹断区空穴迁移率比夹断区空穴迁移率影响大,以致器件的反向Idsat退化比正向Idsat退化大,而对于Idlin,界面态对整个沟道内空穴迁移率影响几乎相同,所以反向Idlin与正向Idlin退化相同.本文揭示了小尺寸pMOS不同栅压应力下的热载流子退化机理,为其热载流子退化应力条件的选取和热载流子退化寿命模型的建立提供了支持与参考.

参考文献

[1]Joly Y,Lopez L,Portal J M,et al.Matching degradation of threshold voltage and gate voltage of NMOSFET after hot carrier injection stress[J].Microelectronics Reliability,2011,51(9) : 1561-1563.

[2]Bravaix A,Huard V,Goguenheim D,et al.Hot-carrier to cold-carrier device lifetime modeling with temperature for low power 40nm Si-bulk NMOS and PMOS FETs[A].IEEE Conference Publications[C].Washington: 2011.27.5.1-27.5.4.

[3]Huang L X,An X,Tan F,et al.Investigation on channel hot carrier degradation of ultra deep submicron SOI pMOSFETs[A].IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT)[C].Washington: 2012.1-3.

[4]Song Z,Chen Z,Yong A Z,et al.The failure mechanism worst stress condition for hot carrier injection of NMOS [J].ECS Transactions,2013,52(1) : 947-952.

[5]Song Z,Chen Z,Yong A Z,et al.The failure mechanism worst stress condition for hot carrier injection of NMOS [J].The Electrochemical Society (ECS) Transactions,2013,52(1) : 947-952.

[6]Cho M,Roussel P,Kaczer B,et al.Channelhot carrier degradation mechanism in long/short channel n-FinFETs[J].IEEE Trans on Electron Devices,2013,60 (12) : 4002 -4007.

[7]Antoniou M,Udrea F,Tee E K C,et al.Interface charge trapping and hot carrier reliability in high voltage SOI SJ LDMOSFET[A].Power Semiconductor Devices and ICs (ISPSD)[C].Washington,2011.336-339.

[8]Keane J,Kim T H,Kim C H.An on-chip NBTI sensor for measuring PMOS threshold voltage degradation[J].IEEE Trans.on Very Large Scale Integration (VLSI) Systems,2010,18(6) : 947-956.

[9]Magnone P,Crupi F,Wils N,et al.Impact ofhot carriers on nMOSFET variability in 45-and 65-nm CMOS technologies[J].Electron Devices,IEEE Transactions on,2011,58 (8) : 2347-2353.

[10]Kim T H,Yu C G,Park J T.Concurrent NBTI andhotcarrier degradation in p-channel MuGFETs[J].IEEE E-lectron Device Letters,2011,32(3) : 294-296.

刘斯扬男,1987年生于安徽合肥.东南大学电子科学与技术学院博士.研究方向为功率集成电路可靠性.

于朝辉女,1988年生于河北石家庄.东南大学集成电路学院研究生.研究方向为功率半导体器件可靠性.

孙伟锋(通信作者)男,1977年生,江苏人.博士生导师,本科、硕士、博士均就读于东南大学.主要研究方向包括新型功率器件设计、功率集成电路、功率器件模型和射频器件设计.

E-mail: swffrog@ seu.edu.cn

Investigation on the Hot-Carrier-Induced Degradation for 1.8V pMOS Under Different Gate Voltage Stresses

LIU Si-yang1,YU Chao-hui1,ZHANG Chun-wei1,SUN Wei-feng1,SU Wei2,ZHANG Ai-jun2,LIU Yu-wei2,WU Shi-li2,HE Xiao-wei2

(1.National ASIC System Engineering Technology Research Center,Southeast University,Nanjing,Jiangsu 210096,China; 2.CSMC Technologies Corporation,Wuxi,Jiangsu 214000,China)

Abstract:According to the experimental measurement results,combining with the technology computer aided design (TCAD) simulations,the hot-carrier degradations of 1.8V pMOS under different gate voltages are investigated in this paper.The results show that,with the gate voltage increasing,the electron injection mechanism changes to the hole injection mechanism,leading to the increases of the saturation drain current (Idsat),linear drain current (Idlin) and threshold voltage (Vth).However,because there is not any carrier injection,the degradation trend begins to change at Vgs=90%* Vds.Moreover,the study also discovers that the generated interface states have more impact on the hole mobility in the depletion region than that in the non-depletion region.As a result,the degradation of forward Idsatis bigger than the degradation of reverse Idsat.However,the degradations of forward Idlinand reverse Idlinare same since the whole channel is not depleted under Idlincondition.

Key words:hot-carrier; different gate voltage stresses; forward and reverse degradations

作者简介

基金项目:航空科学基金(No.20122469) ;东南大学无锡分校科研引导资金

收稿日期:2014-06-19;修回日期: 2014-11-14;责任编辑:蓝红杰

DOI:电子学报URL: http: / /www.ejournal.org.cn10.3969/j.issn.0372-2112.2016.02.015

中图分类号:TN386.1

文献标识码:A

文章编号:0372-2112 (2016) 02-0348-05