基于CPLD的线阵CCD信号采集系统设计

2016-04-14高鹏飞

董 勇,瑚 琦,高鹏飞

(上海理工大学 光电信息与计算机工程学院,上海 200093)

基于CPLD的线阵CCD信号采集系统设计

董勇,瑚琦,高鹏飞

(上海理工大学 光电信息与计算机工程学院,上海200093)

摘要文中基于复杂可编程逻辑器件设计一款高分辨率的线阵CCD信号采集系统。利用Verilog硬件描述语言进行了CPLD控制模块以及逻辑单元的程序设计,由图像专用A/D芯片中的相关双采样等特殊功能,实现了对CCD输出信号的噪声处理和模数转换,通过USB2.0接口实现了计算机终端采集和控制指令的实时传输。采用CPLD的设计方法具有驱动时序精确、采样速率快、抗干扰性强和输出信号稳定等特点。仿真结果证明,系统总体性能较好,上位机能正确显示采集到的CCD数据,噪声在允许的范围内,在不同的工作环境下,系统性能稳定。

关键词线阵CCD;复杂可编程逻辑器件;Verilog HDL

Design of Linear CCD Signal Acquisition System Based on CPLD

DONG Yong,HU Qi,GAO Pengfei

(School of Optical-Electrical and Computer Engineering,University of Shanghai for Science and Technology,Shanghai 20093,China)

AbstractA high resolution linear array CCD signal acquisition system based on complex programmable logic device is designed in this paper.The Verilog hardware description language is employed in the CPLD control module and the logic unit of the program design.The special features of the A/D chip in the CCD are used to realize output signal processing and analog digital conversion.Real-time transmission is achieved through the USB2.0 interface.The design method of CPLD has the characteristics of high accuracy,fast sampling rate,strong anti-interference and stable output signal.The simulation results show that the overall performance of the system is good stable under different working conditions with noise within the range of the system and correct display of the CCD data by the computer.

Keywordslinear CCD;complex programmable logic device;Verilog HDL

电荷耦合器件(Charge-Coupled Device,CCD),又称图像传感器,广泛应用在天文观察、卫星成像、医学摄像等领域[1]。在实际应用中,线阵CCD驱动信号一般为复杂的周期信号,导致其驱动电路复杂多样,易受外界干扰,工作不稳定。CCD成像电路的设计重点在于对CCD输出的模拟信号进行放大、相关双采样、A/D转换等,转换为数字信号后再进行处理[2]。高速线阵CCD采集系统,设计难度大、电路实现复杂,采用CPLD(Complex Programmable Logic Device)可解决这一难题,应用Verilog HDL语言进行逻辑功能模块的设计,以产生CCD的驱动时序、A/D转换的时序以及采集的数据存储与传输的控制信号[2]。该设计发挥了CPLD高速并行且“可编程”的特点,简化了硬件设计上的难度,能实现CCD的高速采集,成本大幅降低[3]。

1总体设计

本系统采用外接DC 19 V电源供电,再通过DC/DC电压转换芯片转换到各模块所需的电压。使用自然光作为线阵CCD的光源,通过CCD信号处理及A/D转换电路,将CCD的RGB三通道的数据通过USB2.0接口实时传至PC上位机,以Altera CPLD为控制核心,系统框图如图1所示。

图1 CCD采集系统框图

2硬件设计

2.1CCD驱动电路设计

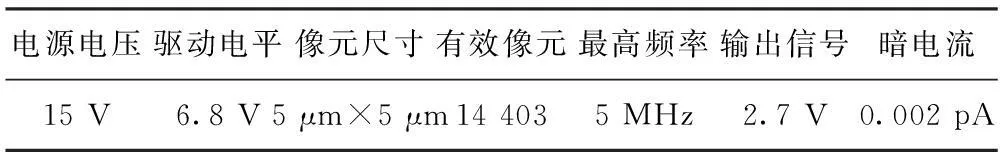

线阵CCD生产厂家众多,例如SONY、Toshiba、Kodak、DALSA等。不同厂家的CCD工作原理与驱动时序大致相同,因此在设计上有一定的通用性。综合考虑光谱响应度、性能、价格等方面因素,设计采用Kodak的RGB三色线阵CCD KLI14403作为感光元件,该元件具有高灵敏度、低暗电流的特点[4],主要特性参数如表1所示。

表1 CCD主要特征参数

KLI14403是一个三通道单边输出二相驱动的线阵CCD器件,对于RGB中的任何一个通道而言,光敏元直接与一个移位寄存器相连接,在时钟信号的驱动下,像元逐个移位输出。常用的线阵CCD驱动方案有两种,即采用单片机驱动,或采用PLD驱动,单片机驱动电路编程灵活,调试简单,但驱动速度慢、效率低。而采用PLD器件,由于其高速并行的特性,能灵活实现CCD的驱动,并且能实现高速采样、存储、通信。本系统采用Altera MAX II 系列的EPM1270T144C5芯片[5]。

参照KLI14403的数据手册,通过RTL网表设计,实现了KLI14403的驱动时序,其Modelsim仿真图如图2所示[6]。h1a和h1b信号是CCD的相时钟1信号,h2a和h2b信号是CCD的相时钟2信号,两个相时钟的相位相差180°,时钟频率为500 kHz。tg_sig控制CCD的积分时间,通过改变tg_sig信号的周期可改变CCD的积分时间[7]。

图2 KLI14403驱动时序仿真图

2.2ADC电路设计

在CCD输出的模拟信号中,电荷包在沟道转移和复位过程中均会引入噪声。如图所示,CCD输出信号的每个像素周期都分为复位电平、参考电平和视频信号电平3部分,每部分均包含有噪声,实践证明,采用相关双采样(Correlated Double Sample,CDS)技术来抑制噪声是最有效的手段。目前采用双采样A/D器件AD9826集成了相关双采样电路,可配置增益放大电路等,完成对CCD信号的模数处理等功能[8]。

AD9826可配置成6种不同的操作模式,设计采用3-channel CDS模式。AD9826同时采样RGB三通道的输入电压,即CCD的RGB三通道的输出电压。每个相关双采样的采样点分别由CDSCLK1和CDSCLK2时钟控制,频率为1 MHz,CDSCLK1时钟的下降沿采样CCD输出的参考电平,CDSCLK2时钟的下降沿采样CCD输出的信号电平,每个CDS放大器输出CCD复位电平和信号电平的差值。ADCCLK控制A/D转换后数据的输出,频率为3 MHz,ADCCLK的上升沿和下降沿分别输出RGB三通道的高8位和低8位数据,其Modelsim仿真图如图3所示。

图3A/D时序仿真图

2.3USB2.0通信接口的实现

在完成CCD的图像采集系统之后,需将采集到的数据信息实时传输至上位机以便上位机进行图像处理。其次,通过上位机发送指令实现CCD的采集控制。在此采用了Cypress公司的USB2.0控制器CY7C68013来实现数据通信[9]。CY7C68013基于Cypress公司的EZ-USB FX2架构,其内部集成了1个USB2.0数据收发器、1个增强型的8051、1个智能USB串行接口引擎等。USB2.0支持3种速率:低速1.5 Mbit/s,全速12 Mbit/s和高速480 Mbit/s。本设计中采用Slave FIFO从机方式实现CPLD对FX控制并采用高速模式[10]。当CCD一帧数据采集完成后,则将采集数据写入USB的FIFO中,上位机接收FIFO中的数据,然后通过一些算法对信号进行处理,软件编写不做过多阐述。

3实验结果与分析

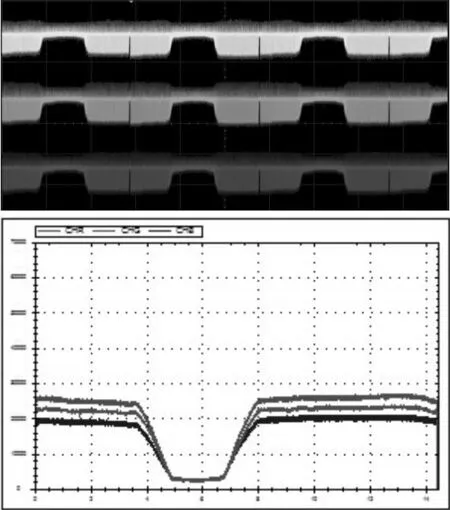

为验证设计方案的正确性,将CCD的RGB三通道输出的模拟信号和上位机显示的波形(从上至下分别是R、G、B通道信号)进行对比。图4是实验1的信号波形对比图,CCD的中间部位没有光照射,其余部位用同等强度的光照射。根据相关双采样的原理,CCD的输出模拟信号的中间部位出现一个“凸”字形的波形,因此处的光照较弱,参考电平和信号电平几乎相同,两者的差值基本为零,因而上位机显示的波形中间会显示一个“凹”字形的波形。图5是实验2的信号波形对比图,对整个CCD采用相同强度的光照射,以R通道为例,参考电平和信号电平的差值电压近似为0.75 V,通过16位的A/D转换后的数值应为24 576,上位机显示的R通道的数字信号值近似为24 500,两者误差不足1%,因此该方案具有一定的可行性且精度较高。

图4 实验1的信号波形对比图

图5 实验2的信号波形对比图

4结束语

系统总体性能较好,上位机能正确显示采集到的CCD数据,噪声在允许的范围内,在不同的工作环境

下,系统性能稳定。这得益于CPLD的高速并行处理能力,从而能成功实现数据的高速采集。最终通过USB2.0接口实现数据的高速传输,保证了通信速度的要求。同时,本设计具有一定的通用性,只需在程序上稍作改动便可适用于其他多款型号的CCD,有一定的科研价值。

参考文献

[1]王庆友.图像传感器应用技术[M].北京:电子工业出版社,2003.

[2]黄正瑾,徐坚.CPLD系统设计入门与应用[M].北京.电子工业出版社,2002.

[3]于庆广,张晓明,王浩,等.CCD视频采集系统设计和实现[J].仪器仪表学报,2006(S2):1365-1366.

[4]贲永志,陈丽娟.彩色线阵CCD三通道数据采集系统[J].仪器技术与传感器,2008(2):30-31,33.

[5]EDA先锋工作室.Altera FPGA/CPLD设计:高级篇[M].北京:人民邮电出版社,2005.

[6]付天舒,赵春晖.基于Verilog的线阵CCD驱动时序设计[J].光学技术,2010,36(5):740-743.

[7]喻川,邹建.基于CPLD的可调积分时间线阵CCD驱动的设计[J].四川兵工学报,2008,29(3):94-96.

[8]侯新梅,李自田,胡炳樑.AD9822及其在面阵CCD系统中的应用[J].现代电子技术,2010,33(20):191-193,196.

[9]萧世文.USB2.0硬件设计[M].北京:清华大学出版社,2002.

[10]谭安菊,龚彬.USB2.0控制器CY7C68013与FPGA接口的Verilog HDL实现[J].电子工程师,2007,33(7):52-55.

中图分类号TN911.73

文献标识码A

文章编号1007-7820(2016)03-154-03

doi:10.16180/j.cnki.issn1007-7820.2016.03.040

作者简介:董勇(1991—),男,硕士研究生。研究方向:光电检测,嵌入式应用等。

收稿日期:2015- 07- 30