3 A/40 V新型肖特基势垒二极管的设计与研制

2016-04-14王富强马行空瞿宜斌

王富强,马行空,瞿宜斌

(93856部队,甘肃 兰州 730070)

3 A/40 V新型肖特基势垒二极管的设计与研制

王富强,马行空,瞿宜斌

(93856部队,甘肃 兰州730070)

摘要为提高传统肖特基二极管的击穿电压,减小了器件的漏电流,提高芯片利用率,文中设计研制了适合于裸片封装的新型肖特基势垒二极管(SBD)。利用Silvaco Tcad软件模拟,在器件之间采用PN结隔离,器件周围设计了离子注入形成的保护环,实现了在浓度和厚度分别为7.5×1012cm-3和5 μm的外延层上,制作出了反向击穿电压45 V和正向导通压降0.45 V的3 A/45 V肖特基二极管,实验和仿真结果基本吻合。此外,还开发了改进SBD结构、提高其电特性的工艺流程。

关键词肖特基势垒;结隔离;保护环;击穿电压

Design and Fabrication of 3 A/40 V Schottky Potential Barrier Diode

WANG Fuqiang,MA Xingkong,QU Yibin

(Troop 93856,PLA,Lanzhou 730070,China)

AbstractA novel Schottky potential barrier diode (SBD) suitable for die package has been successfully designed and fabricated to increase the breakdown voltage,decrease the leakage current and improve the utilization ration of chip area.The PN junction isolation is performed by simulation in Silvaco Tcad between devices surrounding which a protecting ring is designed using implantation technique.A 3 A/45 V Schottky diode with breakdown voltage of 45 V and forward voltage of 0.45 V was fabricated on 5 μm epitaxial layer doped at N-concentration of 7.5×1012cm-3.The simulated characteristics of SBD are verified by the measurement results.The structure and technological processes for improving the performances of SBD are also presented.

KeywordsSchottky potential barrier diode;junction isolation;protecting ring;breakdown voltage

随着电子科技技术的不断发展,电子产品更加小型化、便携化。整机设计尺寸的变小,要求内部芯片占用比例缩小。传统肖特基二极管阳极和阴极分别位于硅片两侧,芯片厚度较大,同时多个肖特基二极管串并联占用空间较大。因此,在保证设计要求的前提下,采用肖特基二极管裸片封装很有必要[1-4]。

本文设计和试制了反向击穿电压45 V和正向导通压降0.45 V的肖特基二极管,提出了利用PN结隔离的方法。在同一个芯片内部集成多个靠近结终端处结构彼此基本相同、远离终端处结构相似的肖特基二极管小单元(称为元胞),各元胞之间利用结隔离的方法实现电学绝缘[5-7]。另外,利用穿通光刻工艺将二极管产品的负极引到正面,将正、负两极间隔布置,做在芯片的同一平面上,减小了单个二极管的厚度,也便于多个晶体管连接,实现了整片封装。再通过对比各种终端设计,最终选择了工艺简单利于实现的离子注入保护环的方法来提高击穿电压,减小边缘泄漏电流。

1器件结构设计

传统的肖特基二极管采用金属半导体形成肖特基势垒,如图1所示[8-9]。(1)阳极和阴极位于硅片两侧,所以肖特基二极管的阴极位于芯片底部,是连成一片的,不能做隔离设计实现裸片封装;(2)大规模集成电路需整个硅片集成上万个二极管,若将各个独立的二极管串联或并联起来,必将占用较大空间。另外,阳极和阴极的金属层增加了芯片的厚底,不利于大规模集成电路最小空间的设计;(3)没有场限环的设计,导致此类结构反向耐压一般不超过20 V,甚至低6~7 V。

图1 传统肖特基二极管结构

1.1隔离结设计

以P型Si为衬底,设计反向耐压为45 V的肖特基二极管。若两个肖特基二极管或其他两个器件互相毗邻,其会因外延层相同而彼此影响,产生寄生电容、寄生晶体管等,降低了反向耐压,增大了漏电流,甚至会因彼此穿通短路而失效[10]。为了将不同的元器件隔离开,常用的隔离方法有PN结隔离、介电质隔离和沟槽隔离。

然而,介质隔离和沟槽隔离均要进行表面刻蚀,需要多次光刻,也就需要更多的光刻掩膜板,易导致沟槽表面形貌发生变化。一些原来位于体内的缺陷逐渐显露到硅片表面,造成晶格缺陷,在沟槽表面处电势线较为集中,导致漏电增大,且器件在减薄之后器件厚度小,再进行刻槽工艺会增大碎片率。两种方法均增大了工艺难度,并增加了成本。

选用P型抛光片,如图2所示。再进行 N 型扩散。在 N 型扩散之后,在晶片的表面通过外延生长一层 N 型的外延层。该埋层作为肖特基二极管的阴极区。为了引出肖特基二极管阴极区,需要通过将N+埋层上推和外延层向下扩散对接形成。外延层生长后,将其氧化并在埋层的两边各光刻一个小孔。同时要进行P型掺杂步骤,并使其达到P型晶片的表面和接通P型衬底。通过以上步骤,每边P型掺杂区和底部P型晶片形成了一个U型包围圈,将外延层孤立成一个 “N 型小岛”,同一个芯片上的多个在“孤岛”上所形成的元器件就被相互隔离开了。因连在电路中的 PN 结处于反向模式状态,实现了电学绝缘。

图2 N型外延结隔离结构

与传统PN结隔离工艺方法相比,该结构工艺简单。在保证击穿电压达到50 V的情况下,这种结构可做到fT≥200 MHz。由于与传统工艺具有较好的兼容性,因而易于实现,是一种较理想的结构。

由于扩散工艺时间长,存在横向扩散,扩散深度杂质分布较难控制,不能保证阴极是否连通,因此采用穿通光刻和离子注入工艺。本文设计的肖特基二极管是通过离子注入生成阴极区,通过穿通光刻引出阴极引线。

1.2结终端设计

由于肖特基势垒结属于浅结,边缘处曲率半径很小,击穿电压很低,在实际测试中击穿电压多为十多伏。为解决这一问题,一般对结的终端进行造型处理,常用的结终端技术主要有:场板、场限环、可变表面掺杂、斜表面和耗尽层腐蚀等。

由于小尺寸裸片封装要求占用芯片面积小,对寄生参数影响尽可能小,在工艺上并不复杂,所以该器件中采用保护环技术,如图3所示。电极是由多层金属溅射淀积而成。

图3 结构截面示意图

利用Silvaco Tcad软件模拟在正向导通和反向击穿两种情况,其中外延层厚度为5 μm,掺杂浓度为8×1012cm-3和5 μm,氧化层厚度为1.6 μm。仿真曲线如图4和图5所示,左图为线性曲线图,右图为相应半对数曲线图。从4图中可看出,当纵坐标IF=0.1 A(电极长度为1 500 μm)时,施加阳极电压从0 V按步进0.05 V增大至1 V,在VAnode≈0.425 V时,二极管导通,即器件正向导通压降约为0.425 V。从图5中可以看出,施加阴极电压从0 V按步进2.5 V增大至50 V,在Vcathode=48.5 V时,器件电流瞬间增大,表明此时器件已击穿,击穿电压约为50 V,且漏电流几乎为0 V,符合设计要求。

图4 肖特基二极管正向导通特性曲线

图5 仿真的反向击穿特性曲线

2实验及结果

2.1制备工艺

(1)在P型抛光片生长N+埋层;(2)通过二次氧化、二次光刻、腐蚀、扩散形成隔离结;(3)通过三次氧化、三次光刻、腐蚀、扩散形成阴极区;(4)采用四次光刻、腐蚀、B离子注入形成保护环。另外,为了将击穿限定在主结,在芯片其他处不出现击穿点甚至是高场的集中区,提高可靠性,做一次补P场控注入。

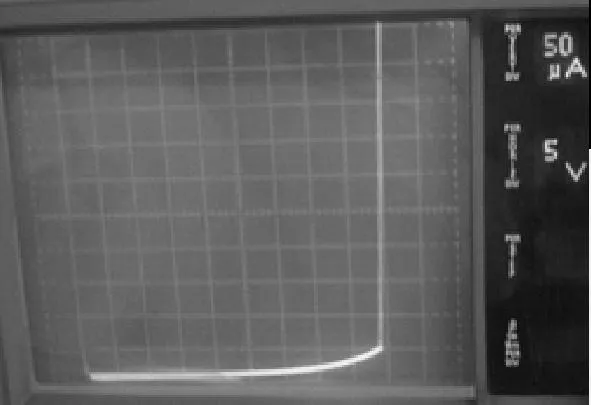

2.2实验测试结果

图6为正向导通测试结果,图7为反向击穿测结果。可看出二极管反向击穿电压为45 V,符合设计要求的3 A/40 V。在图7正向测试电压中,在3 A下的正向导通压降是0.45 V,也符合设计要求。与Silvaco Tcad仿真结果基本吻合,但由于模拟仿真为理想化状态仿真,正向导通压降略低于实验结果,反向击穿电压略高于实验结果,故仿真结果优于设计目标。

图6 正向压降测曲线

图7 反向击穿特性

3结束语

本文采用N型外延结隔离和离子注入保护环结构试制了一种新型3 A/45 V的肖特基二极管。Silvaco Tcad软件仿真和实验测试表明击穿电压提高、漏电流明显较小,达到了设计目标。测试和仿真结果基本吻合,适合于裸片封装。提出的器件设计方法、结构和工艺对生产实践有一定的指导意义。

参考文献

[1]欧宏旗,刘伦才,胡明雨,等.一种PN结隔离互补双极工艺[J].微电子学,2007,37(4):548-552.

[2]李俊楠,战可涛.新型4H-SiC肖特基二极管的仿真与分析[J].北京化工大学学报:自然科学版,2012,39(4):117-121.

[3]孟庆巨,刘海波,孟庆辉.半导体器件物理[M].北京:科学出版社,2005.

[4]宁宝俊,赵忠礼.金属硅化物—硅功率肖特基二极管[J].北京大学学报:自然科学版,1993,29(1):71-78.

[5]Manual A U.Silvaco international[M].CA:Santa Clara,2000.

[6]赵普社,王因生,傅义珠.对功率器件击穿电压的模拟优化[J].电子与封装,2007,7(10):40-43.

[7]Cheung S K,Cheung N W.Extraction of schottky diode parameters from forward current-voltage characteristics[J].Applied Physics Letters,1986,49(2):85-87.

[8]王晨飞.半导体工艺中的新型刻蚀技术——ICP[J].红外,2005(1):17-22.

[9]卢宝文,徐学科,余祥,等.不同沉积速率下热蒸发银膜的光学性能和结构分析[J].光学学报,2010(1):283-286.

[10]孙卯秋.肖特基二极管多层金属化技术[J].济南大学学报:自然科学版,1999,9(5):47-49.

中图分类号TN311+.8

文献标识码A

文章编号1007-7820(2016)03-134-03

doi:10.16180/j.cnki.issn1007-7820.2016.03.034

作者简介:王富强(1988—),男,硕士。研究方向:器件和集成电路设计。

基金项目:国家自然科学基金资助项目(61366006);甘肃省科技支撑计划项目(1304GKCA012)

收稿日期:2015- 08- 12