一种高速交叉通道数据链路的设计研究

2016-04-07何小亚李成文解文涛高杨湛文韬杨

何小亚 李成文 解文涛 高杨 湛文韬 杨涛

摘要:交叉通道数据链路是机载容错计算机系统中很重要的数据交换方式,其可靠性和传输速率影响整个系统的容错性能。该文在核心处理机应用背景下,从编码方式,同步机制,差错控制和数据传输等角度进行分析对比,并设计出基于FPGA和MAX3491驱动器的一种高可靠性的高速交叉通道数据链路(CCDL)。

关键词:交叉通道数据链路;机载容错计算机;FPGA;MAX3491

中图分类号:TP393 文献标识码:A 文章编号:1009-3044(2016)03-0004-02

核心处理机采用容错系统结构,双通道热备份方式,每个通道具有独立的相同的数据处理模块,两通道之间通过实时通信实现任务同步的热跟随处理模式[1]。

目前广泛用于容错系统实时通信方案的实现方式和优缺点如下[2-4]:

1)网络技术方式,优点是技术比较成熟,但占用系统资源,硬件集成难度大,传输速率也比较慢。

2)双端口RAM方式[5],优点是能将控制逻辑与存储器集成在一片大规模集成电路内,实现真正的双端口异步操作。缺点是硬件布线开销较大,且每个RAM芯片只能连接两个CPU。

3)总线方式,优点是接口比较统一且易于实现,但数据传输速率就比较慢。

由于32位的数据线和32位的地址线在机箱母板上实现起来过于密集,软硬件复杂度都太大,故不选用双端口RAM方式。网络通讯方式占用系统资源,硬件开销大,传输速率也比较慢,也不能采用。相对而言总线技术较为合适本系统,只要设法提高传输速率就可以满足系统要求。如图1所示[1],核心处理分机由两个VME总线将数据处理模块等各功能模块组成两套独立的工作单元,两个工作单元之间通过各自的数据处理模块引出CCDL信号线采用RS422串行总线通过母板与对方交叉互联。

数据处理模块内部的CCDL逻辑电路是完成数据发送和接收的功能载体,是整个CCDL链路的核心,下面从编码方式选择、同步机制、差错控制和数据传输原理等方面对CCDL电路设计方案进行对比研究,最后给出设计结果。

1 编码方式

CCDL采用MAX3491驱动器以差分串行方式传输数据,串行数据位需要进行编码才能正确传输。不归零编码是将二进制数字0、1分别用两种电平来表示,方法简单容易实现,编码效率也非常高,缺点是会产生直流分量的积累,使信号失真。采用电荷泵锁相环(CPPLL)里的鉴频鉴相器(PFD)完成时钟数据恢复电路在没有数据跳变的时候不发生错误的比较,并提供正确的时钟输出。

2 同步机制

在串行数据传输中,发送方和接收方依据各自的时钟周期来确定发出和接收数据的每一位时间的长短。这就需要收发双方进行同步来保障二者有一致的时钟周期。目前主流同步方法有位同步、帧同步、字符同步。

字符同步方式控制简单,可靠性高且实现成本低,故在此采用字符同步方式。将数据字符定义为1位起始位、16位数据位、1位校验位和1位停止位。起始位用低电平表示,停止位用高电平表示。由于字符之间的间隔不确定,为了正确判别每个字符的到来,线路平时保持高电平,一旦出现了一位低电平,就表示数据传输开始了(这位称为起始位),接着传数据位和校验位待传输完毕后,再加上1位的高电平(即停止位)表示数据传输结束。

3 差错控制

CCDL 可靠性至关重要,因此设计中除了要尽量避免错误出现,还要考虑差错控制问题。在CCDL电路设计中,采用如下措施避免错误出现:

1)双通道数据处理模块尽可能近放置(两个数据模块调整放在中间)和远离干扰源(如远离电源模块和音频告警模块)以减少干扰;

2)CCDL串行数据以RS422差分方式传输,差分线等长并行走线而且用地包;

3)逻辑设计中计数器编码使用采用格雷码[7]代替普通的二进制编码,格雷码计数器输出每次只有一位数据产生变化,可以消除竞争冒险产生的条件,避免逻辑设计中毛刺的产生;

4)另外逻辑设计中尽可能用D触发器输出,这样可以减少由于信号延时不一致而可能产生的逻辑毛刺。

以上虽然采取了一些措施来避免错误,但是无法消除错误,这需要一套机制来实现差错控制。目前差错控制方法有三中取二[8和检、纠错码。三中取二传输效率太低。常用的检错码主要是循环冗余编码和奇偶校验码。循环冗余编码需要较多的附加信息效率低。因此选择奇偶校验码进行检错,检测出来错误后使用拉回式重传机制纠正错误。

4 数据传输原理

数据传输工作过程是系统上电复位后,CCDL的收发中断处于禁止状态,由应用软件来使能中断。系统收到发送中断后查询发送FIFO是否空,如果空就往发送FIFO写数据。写完后CCDL就进行数据发送。系统在中断服务程序中从接收FIFO中读数据。接收方每接收到一个字符都要进行奇偶校验检查,一旦检测到校验错误就给发送方发回错误数据编码然后进行拉回重发。接收逻辑收到数据后先解析包头,把数据长度寄存器中用于数据传输检查,数据接收完后向系统发出中断请求。

5 硬件设计

数据处理模块的CCDL逻辑电路需要完成数据的发送和接收的功能,主要由FPGA和MAX3491驱动器组成。

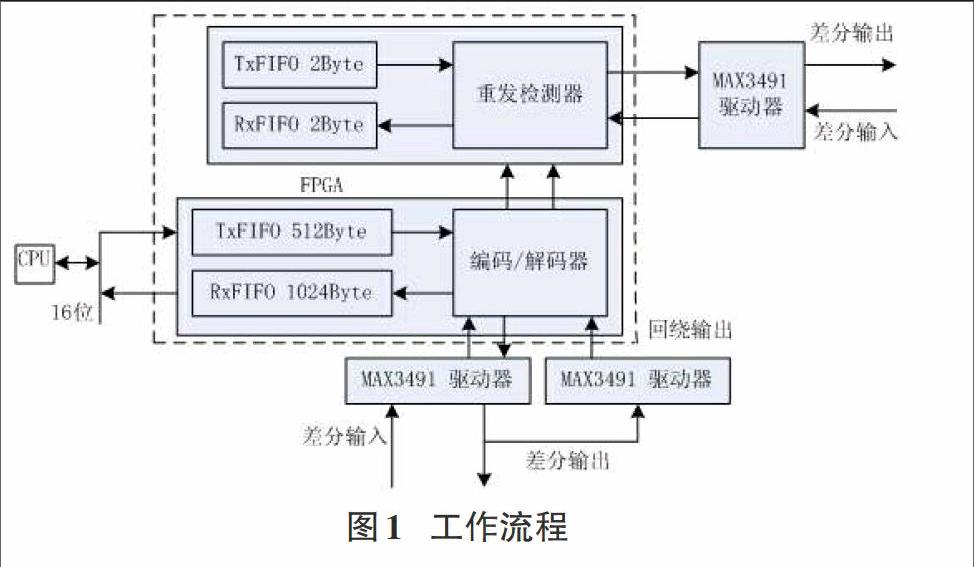

CCDL电路设计0.5KB发送FIFO和1KB接收FIFO,为了支持拉回重发纠错机制和双通道同时交换数据的需要,增加1路2B发送FIFO和2B接收FIFO用于传输错误数据编号。

根据热跟随处理模式,数据处理模块所有对外接口应该完全一致。但两个数据处理模块内部实现可以采用异构方式提高系统可靠性,也可采用同构方式来降低成,本系统的两块数据处理模块内部结构完全相同,其数据传输的工作流程也完全相同,具体如图1所示。

6 结束语

本文详细介绍了一种基于FPGA和MAX3491驱动器的一种高可靠性的高速交叉通道数据链路(CCDL)的设计思路和设计结果,这种实现方式简单可靠,且具有可扩展性,在其他容错系统中有广泛的应用,现在很多工业系统都是采用余度容错技术来提高系统的可靠性。对于其他要求可靠性高的余度容错处理系统中,该CCDL实现方式同样有着良好的应用前景。

参考文献:

[1] 牛文生.机载计算机技术[M].航空工业出版社,2013.

[2] 潘计辉,张盛兵,张小林,等.三余度机载计算机设计与实现[J].西北工业大学学报,2013(5):708-802.

[3] 芶冬荣,刘海清.双机容错计算机系统的设计与实现[J]. 计算机工程,2008(15):255-258.

[4] 闫稳.机载供电系统双余度控制器的容错控制[J]. 航空计算技术,2010(40):86-88.

[5] SDRAM Device Operation,Samsung Inc,1998.

[6] 江力,吴海红,等.通信原理[M].北京:清华大学出版社,2007:63-70.

[7]吴晓建,谢明,邱香,等.格雷码性质研究[J],机电工程技术,2010(9):80-82.

[8]柳孔明,黄俊.无人机多余度航空电子系统研究与应用[J].计算机测量与控制,2012(5):1340-1343.