基于FPGA的数字下变频设计

2016-03-24李飞冯晓东刘其超

[李飞 冯晓东 刘其超]

基于FPGA的数字下变频设计

[李飞 冯晓东 刘其超]

摘要

数字下变频是软件无线电的关键技术之一,在分析数字下变频基本原理的基础上,给出了一种数字下变频的设计方案,然后基于Xilinx Vivado开发平台对各个模块进行设计,最后借助Modelsim 10.1a和Matlab对方案进行仿真验证,结果表明本文方案是正确可行的。

关键词:软件无线电 数字下变频 FPGA 数字滤波器

李飞

重庆邮电大学通信与信息工程学院,硕士,主要研究方向为数字接收技术,数字信号处理。

冯晓东

重庆邮电大学通信与信息工程学院,高级工程师,主要研究方向为射频微波接收技术。

刘其超

重庆邮电大学通信与信息工程学院,硕士,主要研究方向为光纤通信。

0 引言

软件无线电的基本思想是构造一个通用的硬件平台,将各种通信功能通过软件控制来实现,这就摆脱了传统无线电面向硬件的设计方式,很大程度提高了开发效率[1]。数字下变频(DDC)是软件无线电的关键技术之一,被广泛应用于数字接收机中,DDC模块在AD模块后面,把高速数字信号转化成低速数字信号,以便后续模块对信号进行实时处理,DDC的设计将直接影响接收机接收性能的好坏。

1 数字下变频原理

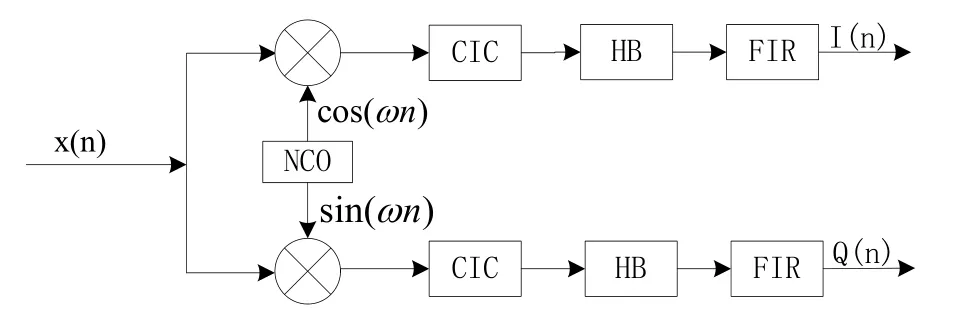

本文的DDC设计方案如图1所示,包括正交混频和抽取滤波两部分,其原理过程为经过A/D转换后的数字信号x(n)与数字振荡器(NCO)产生的正余弦波相乘进行正交混频,混频后的信号经过积分梳状(CIC)滤波器和半带(HB)滤波器进行抽取滤波,最后通过FIR滤波器进行整形滤波,输出 I(n)和Q(n)两路基带信号[5]。

图1 DDC原理框图

2 数字下变频的设计

本文DDC中各模块的设计大部分采用Xilinx IP Core完成的,Xilinx公司把一些功能模块进行高效设计然后封装成IP Core,像乘法器和FIR滤波器等,开发者进行FPGA开发时可以直接调用这些IP Core,这样做可以缩短开发周期,提高开发效率。

2.1 混频模块设计

混频模块主要包括数字振荡器NCO和乘法器,NCO的主要功能是产生稳定的、正交的、频率可控的正弦和余弦信号,它是影响DDC性能的主要因素之一,其离散序列表达式如式(1)所示:

其中fLO是NCO产生的本振频率,fclk为系统参考时钟。

NCO实现方法很多,最常用的方法是查找表法(LUT),其结构如图2所示:

图2 NCO结构图

由图2可知,NCO主要由相位累加器、相位寄存器和波形储存器三部分组成[4],它的工作原理是:每来一个系统时钟fclk,相位累加器就把频率控制字累加一次,然后用得到的相位累加值作为地址,根据地址查找相应的幅度值,最终输出相应的波形。系统时钟fclk、相位累加器的位数N、频率控制字K的大小共同决定NCO的输出频率fout,三者的关系如式(2)所示。

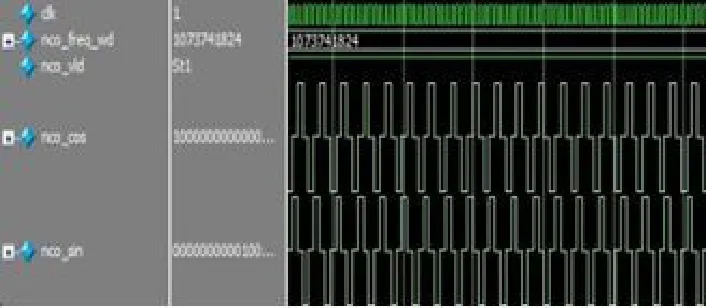

本设计系统时钟fclk=128MHz,N=32,输出频率为out=32MHz,由(2)式可得频率控制字K=1073741824,仿真波形如图3所示。

图3 NCO输出波形仿真图

2.2 抽取滤波模块设计

低通滤波器组的主要作用是低通滤波,一般由FIR滤波器实现。但是,由于FPGA接收的AD采样数据具有很高的采样率,不适合实时处理,因此,该低通滤波器组还需实现降低采样率这一功能。同时,高采样率的数据会增加FIR滤波器的设计难度,使得资源消耗过多、功耗过大,因此在使用FIR滤波之前,需要使用抽取滤波器组来降低采样率。本文采用积分梳状滤波器和半带滤波器进行抽取滤波。

2.21 CIC滤波器

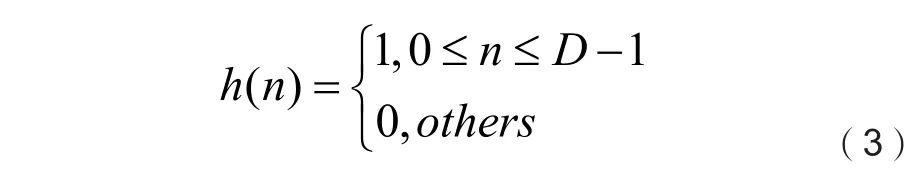

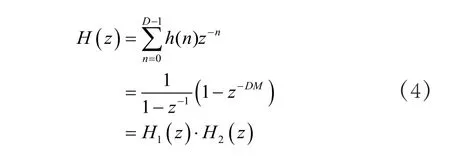

积分梳状滤波器(Cascaded Integrated Comb,CIC)的冲激响应为:

其中D为CIC滤波器的阶数(即抽取因子)。由冲激响应可见,CIC滤波器其实是一种具有线性相位的特殊FIR滤波器[3],其Z变换如(4)式:

图4 CIC滤波器的结构图

由图4可见,CIC滤波器由积分器H1(z)、梳状滤波器H2(z)和抽取器组成,其结构简单,无需一般FIR滤波器所需的乘法运算,这不仅提高了实时性,而且也简化了硬件,适合于工作在高采样率条件下,因此CIC滤波器在多速率信号处理中具有特别重要的位置[2]。

由于单级CIC滤波器的阻带衰减很差,只有13.46 dB,所以工程常用多级CIC滤波器级联。

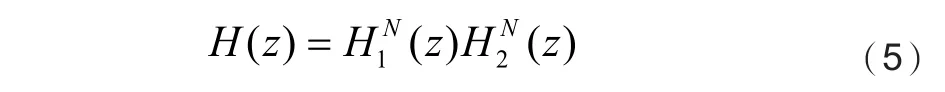

N级CIC滤波器的传递函数为:

每增加一级CIC滤波器,则旁瓣电平衰减增加13.46 dB。本设计中使用5级级联CIC滤波器,频谱特性如图5所示,其具有67.3dB的阻带衰减[3],基本能满足实际要求。

图5 级联5级CIC滤波器幅频曲线

本文的CIC滤波器是借助Xilinx LogiCORE IP CIC Compiler实现的[7],在IP Core中可以配置相应的抽取率和级联数。

2.22 HB滤波器

半带滤波器(Half-Band,HB)适合于实现D= 2M倍(2的幂次方倍)的抽取或内插。其冲激响应为:

从公式(6)可以看出,HB滤波器的冲激响应除了h(0)为1外,在其他偶数点的取值均为零,即滤波器近一半的系数为零,这就节省了一半的运算量,具有很高的实现效率,适合于进行实时处理。

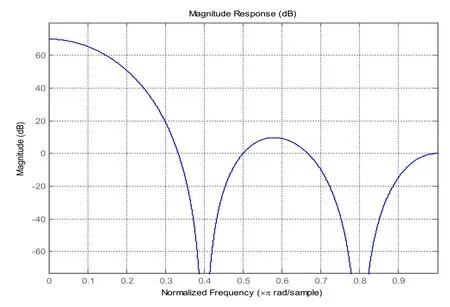

其幅频特性如图6所示:

图6 半带滤波器幅频响应示意图

半带滤波器的频率响应满足以下关系:半带滤波器的阻带宽度π−ωs与通带宽度ωp是相等的,且通带和阻带波纹相等[2]。

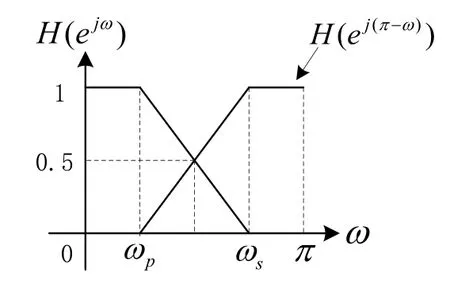

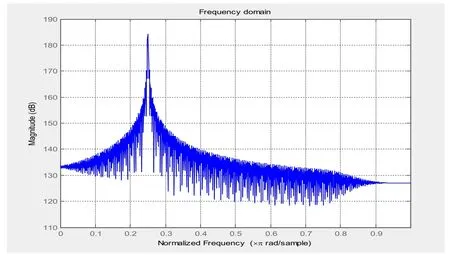

本文设计用Matlab中的FADTool来设计HB滤波器的,把生成的滤波器系数导入到FPGA的FIR IP Core中[6]。幅频响应曲线如图7所示,HB滤波器的阶数为16,截止频率为0.3Fs,阻带衰减为110dB。

图7 HB滤波器幅频响应曲线

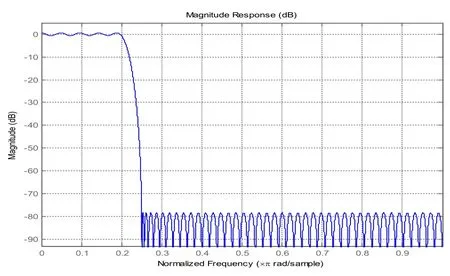

2.23 FIR滤波器

在数字下变频模块中,HB滤波器后面需要增加一个FIR低通滤波器进行整形滤波,由于这时信号经过抽取后速率变得较低,所以可以适当提高FIR的阶数来减少过渡带宽,提高滤波性能。本文FIR滤波器是通过Matlab FADTool工具设计的,如图8所示,该滤波器阶数为100阶,阻带衰减为80dB,通带宽度为0.2Fs。

3 FPGA仿真结果

系统验证对频率为1MHz信号的数字下变频,本文设计采用的系统时钟为128MHz,中频频率为96MHz,用系统时钟对中频信号进行采样,由带通采样定理可知,在32MHz处会出现基带信号的镜像信号,把FIR滤波器的Fs设为8MHz,采样时钟从128MHz变到8MHz,抽取率为16,所以CIC滤波器抽取率为8,HB滤波器为2。

图8 FIR滤波器幅频响应曲线

系统输入97MHz余弦信号,经过采样后镜像信号出现在33MHz处,然后与NCO产生的32MHz正交信号进行混频,通过抽取滤波后最终应该存在1MHz的信号不被滤掉。

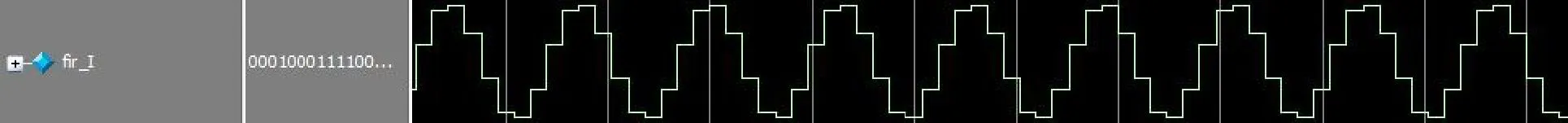

取I路信号进行观察,混频Modelsim仿真图如图9所示,经过FIR输出的时域信号如图10所示。

把FPGA中FIR输出的数据导入到Matlab中可得归一化频谱图如图11所示,从中可看出1MHz信号没有被滤除。

结合图9、10、11可以看出,本设计方案准确完成了1MHz信号的数字下变频。达到了预期的效果。

4 结语

本文基于FPGA设计了一种数字下变频的方案,设计方案采用高效滤波器进行抽取滤波,可以节省一定的资源。同时,大部分模块的实现采用了Xilinx IP Core,这样做可以简化设计流程和缩短开发时间,从最后的结果可以看出本设计方案是正确可行的,可以应用到中频接收机中,具有良好的应用前景。

图11 输出信号归一化频谱图

图9 混频信号仿真图

图10 输出信号时域仿真图

参考文献

1杨小牛, 楼才义, 徐建良. 软件无线电原理与应用[M]. 北京:电子工业出版社, 2001

2徐小明, 蔡灿辉. 基于FPGA的数字下变频(DDC)设计[J].通信技术,2011,44(10)

3陈斌, 杜仲, 周世君,等. 一种基于FPGA的数字下变频算法设计[J]. 电视技术,2011,35(13)

4罗琳.基于FPGA的数字下变频的研究与分析[D].西安:西安电子科技大学,2013

5苏晓晓.数字化接收机的FPGA设计[D].哈尔滨: 哈尔滨工业大学,2012

6Xinlinx Inc, LogiCORE IP FIR Compiler v6.3 DS794, March 1, 2011

7Xinlinx Inc, LogiCORE IP CIC Compiler v3.0 DS845, June 22, 2011

收稿日期:(2015-11-22)