100MHz带宽数字存储示波器的模拟通道设计

2016-03-22辽宁工业大学电子与信息工程学院孟丽囡孙福明

辽宁工业大学电子与信息工程学院 王 浩 孟丽囡 孙福明

100MHz带宽数字存储示波器的模拟通道设计

辽宁工业大学电子与信息工程学院王浩孟丽囡孙福明

【摘要】本文采用分立元件设计了一种应用于100MHz带宽的数字存储示波器的模拟通道。为克服传统模拟通道中存在的固有缺点,使用了VGA与固定增益级联的方法。所设计的模拟通道主要由信号垂直调理电路、触发电路、通道控制与校正电路组成。方波增益测试和频率响应测试验证了本文设计的有效性。

【关键词】模拟通道;信号垂直调理;VGA;触发

注:本文受辽宁省高等学校优秀人才支持计划资助(LR2015030)。

1 引言

示波器可将人眼看不见的电信号转化为图像信息,方便人们对电信号的测试和研究。为了更加直观和深入理解被测对象,所以常需要借助示波器进行[1]。采样率和模拟带宽是评价数字示波器的两个重要指标。模拟带宽容易受外界环境干扰,特别是高带宽示波器更易受系统中的地弹、串扰以及其他多种影响。本文设计的数字示波器的模拟通道,主要的技术指标要求包括:(1)模拟带宽:100MHz;(2)垂直通道档位:5mV/div-5V/ div (1-2-5步进);(3)输入阻抗:1MΩ/150Ω可选;(4)触发类型:边沿触发;(5)触发源:外部触发、通道1信号、通道2信号、交流信号(50Hz)。

2 系统设计方案

2.1总体方案

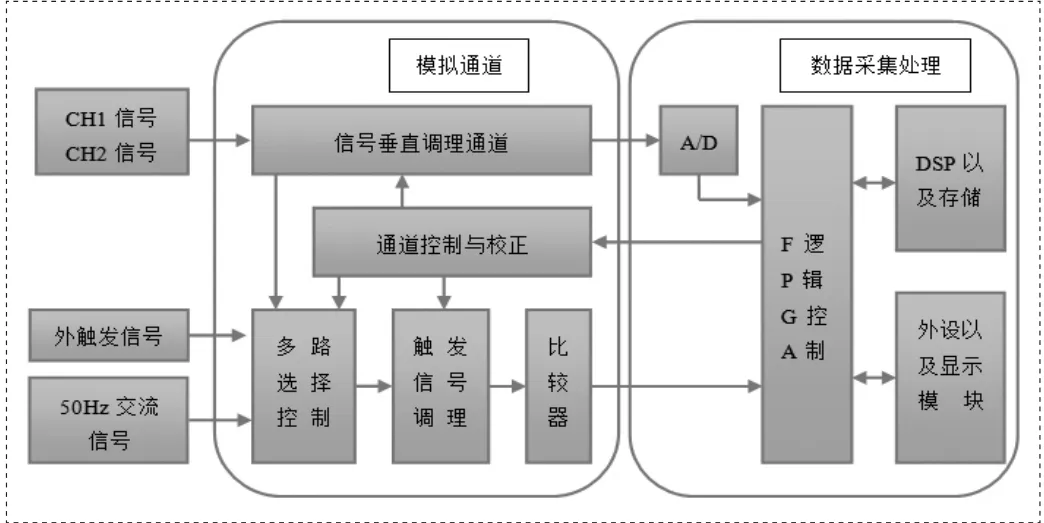

数字存储示波器的整体设计框图如图1所示。

图1 数字存储示波器总体方案

模拟通道包含信号垂直调理通道和触发通道。前者是限制数字示波器带宽的关键。通常,ADC的输入范围比较窄(一般少于1Vpp),所以采用信号调理电路对输入信号进行调整。为保证波形信号稳定地显示,每次的开始扫描的位置都必须是周期信号的同一点。

2.2信号垂直调理通道方案

信号通道由CH1、CH2通道组成,两路通道完全相同。由于外接信号幅度不定,所以首先对其进行衰减。带宽限制是为减少高频噪声。阻抗变换可减小后级直流偏移量。增益控制是对信号幅度进行增益和衰减,这可使ADC逼近满量程。输出驱动环节实现信号单端转差分和加垂直偏移调节,外部输入信号经此通道进入AD进行处理。

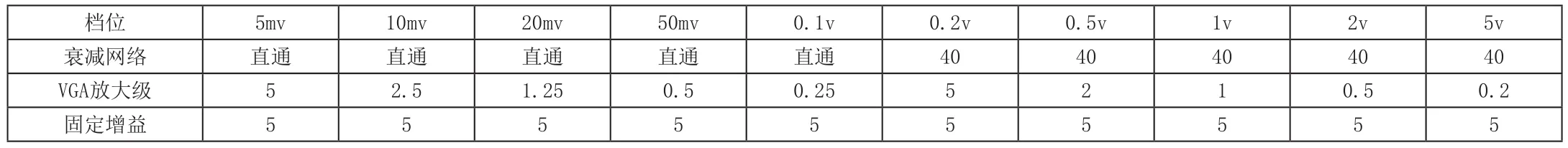

设计要求外部输入电压范围是±5mV~±50V[2],具体设置如表1所示。

2.3触发信号通道方案

触发信号通道主要通过多路选择器对输入信号进行选择,如果是50Hz交流或外部信号,需进行信号调理;如果是经信号调理的CH1和CH2信号,则可直接输入高速比较器。高速比较器把输入信号和触发基准信号进行比较,输出不同占空比的脉冲信号给FPGA处理。

2.4通道控制电路方案

通道控制电路是对触发通道和信号调理通道的各个继电器和调节电平进行控制,比如交直流耦和、衰减网络以及输入通道的选择。调节电平控制主要调节调偏电压和VCA压控端。

3 信号垂直调理通道电路

3.1无源衰减网络

无源衰减网络在信号垂直调理通道中起着重要作用[3],因VCA824衰减范围有限,所以有必要设计衰减网络与之配合。

实际线路中分布电容和引线电容对网络有影响,当电路工作在高频段时,为抵消电阻的寄生电感和寄生电容,加入高频补偿电容。调节高频补偿电容使网络达到最佳补偿时,无源衰减网络的衰减倍数K为:。

表1 增益衰减分布表

3.2阻抗变换电路

信号经过无源衰减网络后,在VCA824的输入端会有直流偏移电流,这个电流为微安级。如果其作用在较高的对地电阻上将导致较高的直流偏移量。加入阻抗变换电路来减小输出端对地阻抗,并提高带载能力和隔离前后级影响[4]。

由于高速宽带运放的低频特性不理想,所以直流与交流分开进行阻抗变换。直流分量会影响射随器的Q点,所以通过电容隔直。直流分量通过处于深度负反馈的AD8512的输入端耦合到输出端,与交流分量合二为一,通过阻抗反映法可把信号从输入端传输到输出端。

3.2.1输入阻抗

无源衰减网络与阻抗变换网络之间没有隔离,因此后级会影响前级的输入阻抗。当直通时,输入信号直接进入阻抗变换电路,示波器的输入阻抗等于阻抗变换电路的输入阻抗,则要求阻抗变换电路的输入阻抗为1MΩ。表示无源衰减网络的分压电阻,表示阻抗变换网络中运放输入端的分压电阻。当使用前面无源衰减网络时,示波器的输入阻抗等于,由于无源衰减网络为40倍衰减,则比1MΩ小很多,则示波器的输入阻抗约等于。 3.2.2直流通道

由于输入电压可能会因档位的不同而有不同,为使AD8512正常工作,我们对输入信号进行电阻分压,然后在阻抗变换电路输出端,通过电阻分压将信号变换到原电压值,具体定量分析如下。

3.2.3交流通道

我们利用场效应管和三级管构成复合管来提高输入阻抗。为调整T1管的Q点,我们加入T3,并把它接成电流源的形式。对于T2来说,随温度升高,其Ic和Ie增大,则R4电压增大使AD8512反相端电压升高。同时,AD8512正相电压不变,引起输出减小,导致T2的Ic和Ie减小。经此负反馈维持Ic和Ie的稳定,从而稳定了Q点,减小了温漂,增加稳定性。

3.2.4带宽限制

由于环境以及输入信号的高频噪声容易造成后级放大器自激等干扰,所以有必要对高于100MHz的高频信号做滤波处理来提高系统的灵敏度[5]。本文采用无源一阶低通滤波器。如选有源滤波器,因运放的加入和级间直接耦合方式会引起自激或零漂。

因前后级电路会影响低通滤波器的性能,则把其加在阻抗变换和VCA824之间。

3.3VGA运放电路设计

由于需要直流耦、宽带宽、V/V线性连续可变,本设计选择VCA824。其在10V/V时具有420MHz的带宽,精度达到20dB±0.3dB。由于它在差分输入状态下增益不可变,所以本文设计为单端输入。为提高VCA824的幅频特性和通道平坦度,以及补偿前面分压电阻的误差,设置VCA824的增益为0.05~7V/V。

为了矫正各级电路之间的误差,压控选择12位DA对增益进行精准控制。因为高速信号对阻抗一致性、损耗等要求很高,且需要低阻抗的回流路径,设计采用4层板设计。为去除纹波和去耦电容的效果有限,本文选用电源EMI滤波器提高模拟通道的电磁兼容性(EMC)。本文选用的是BNX005直流电源滤波器,它由四接线端电容器、旁路电容和铁氧体珠电感器构成[6]。

3.4固定增益电路设计

固定增益电路是与ADC连接的运算放大器,主要任务是对信号的固定增益放大和提高带载能力,输出电流能达到180mA。考虑到输入信号可能在高频段,因运放的外围器件和线路会产生寄生电容,我们选取THS4302作为最后一级放大。

3.5单端变差分电路设计

ADC前级为信号的单端转换为差分电路,其对信号进行垂直偏移调节。本文采用LMH6552。在100MHz带宽内,它保证0.1dB的增益平坦度。信号为单端输入,并利用其负端完成垂直偏移调节。

4 触发电路

触发通道是通过多路选择器选择触发信号,然后进行信号调理后进入高速比较器,通过设置不同的触发电平将输入信号变换为不同占空比的触发脉冲。触发信号可以来自系统内部或外部,CH1和CH2的信号直接从信号调理通道中引出,引出时要做相应隔离。当从系统外部引入触发信号时,需要先对信号调理后向多路选择器传输信号。

4.1多路选择器的设计

对于触发信号选择采用LMH6574。它可以通过向引脚12外加电阻的方式设定增益,这样就可以设置增益以便减小后级运放的放大倍数来提高系统的频率响应。

4.2高速比较器电路设计

本文采用LMH7322。当输入超过100mv时,它的失真仅为5ps、供电为宽压2.7V~12V。它的电路。

DAC输出的电压经LM431调整为-2.5V~2.5V,再经过三极管放大后输入比较器。LMH7322输出端将得到的差分同步脉冲信号送给FPGA进行处理。其中,可以调节RHREF 与RHYS之间的迟滞电阻,减少因为假信号噪声引起的状态变化进而增加系统的稳定性。

5 通道控制电路

对信号调理通道控制是把输入的模拟信号进行不失真的放大和衰减以及偏移,保证AD工作在正常采样范围内。对触发信号通道控制是选择不同的触发源,对触发信号的处理进行选择控制,例如触发通道的交/直流耦合控制、高频抑制和低频抑制、高速比较器的输入触发电平的控制。

首先设计通道状态控制电路,当需要对通道的状态进行调整时,由DSP控制FPGA对外部进行控制[7]。本文采用具有输出锁存功能和三态控制的高速转换器CD4094。

然后需要设计电平调节电路,输入调零和偏移控制都需要电平调节,本文通过DAC来实现。DSP控制FPGA发送控制信号给DAC,使DAC输出模拟控制信号。选择DAC时主要考虑3个方面:(1)电压调节范围和电压分辨率;(2)数模转换器的线性度和建立时间;(3)PCB布线的难易,比如是否需要外接参考源。

本文选择采用AD5628。AD5628的分辨率为12bit,电压调节范围为0-5V,建立时间为6us并且内部已经集成参考电压源。FPGA通过SCLK、DIN、SYNC三个引脚控制AD5628。其中VOUTA~VOUTH分别对应的是模拟电压值,用于实现各处电平调节。

6 测试结果与内容

信号源使用RUITE的SG1110数字合成信号发生器,示波器为固纬GDS-1102A-U。首先,设置信号源的参数并分成两路,一路直接送到示波器,另一路送到本次设计的模拟通道中,将其输出送入示波器。然后,对比两路波形,测试系统方波增益与系统频率响应。

首先是方波增益验证,由于线路阻抗匹配的原因,信号源显示的数值与示波器实际测量值之间有一定误差,为了保证测试结果的准确,我们以示波器测量数据为准。信号调理通道调至20mV档时,测试直通情况下的方波增益。此时不通过衰减网络,电阻分压为0.8倍,VGA放大倍数为1.56,整个模拟信号调理通道放大倍数为6.25。信号调理通道调至200mV档时,测试通过衰减网络时的情况。此时通过40倍衰减网络,电阻分压为0.8倍,VGA放大倍数为6.25,整个模拟信号调理通道放大倍数为0.625。完全符合设计目标。

然后是频率响应验证,本次设计的模拟通道的带宽为100MHz,因为有无源衰减网络的加入,所以要分别测试直通和带无源衰减网络两种情况,应用正弦信号点频法测试模拟通道的频率响应,具体为保持输入信号幅度不变,测试当输入信号频率为不同频率时幅度的变化情况。

首先验证直通情况,此时将档位调至20mV档,设置输入信号幅值为160mV,然后调节不同频点并记录输出幅值。20mV档理论增益G0为6.25。测试结果为带宽内0.1dB平坦度达到了60MHz,-3dB带宽达到110MHz,完全符合设计目标。

7 结论

本设计主要实现了多级衰减、VGA可控增益放大、固定增益放大相结合的方式来调控信号。同时,在电源线上加入了磁环减少噪声,并通过加补偿电容对高频部分进行频率补偿。本文的设计从理论分析到实验验证都达到预期结果,但是在增加带宽与降低噪声方面还有一定的提升空间。

参考文献

[1]古天祥,王厚军,习友宝,詹惠琴.电了测量原理[M].机械工业出版社,2006.

[2]涂建.DSO通道与触发电路模块设计研究[D].成都:电了科技大学白动化工程学院,2010.

[3]张涛.数字存储示波器500MHz宽带模拟通道设计[D].成都:电了科技大学,2008.

[4]董平.1GHz带宽多功能数字存储示波器模拟通道设计[D].成都:电子科技大学,2012.

[5]王彦斌.数字存储示波器中300MHz模拟通道设计[D].成都:电了科技大学自动化工程学院,2008.

[6]王立欣,林雨波.门亮.高速数据采集模拟通道设计相关[J].电测与仪表,2007,44(497):44-46.

[7]董立志.示波器信号调理通道与触发电路设计[D].成都:电了科技大学,2012.