高精度时间自动测量装置的设计与实现

2015-12-30秦友伦

张 京,龚 俊,袁 霞,秦友伦

(中国兵器工业第五八研究所特电部,四川 绵阳 621000)

高精度时间自动测量装置的设计与实现

张京,龚俊,袁霞,秦友伦

(中国兵器工业第五八研究所特电部,四川 绵阳621000)

摘要:介绍一种高精度时间自动测量装置实现的原理和方法,并给出测量装置的软硬件设计原理框图,测量装置首先对输入被测信号进行信号调理,然后和启动信号一起送入高速AD采集卡采集,将采集后的数据通过CPCI总线送到主板进行数据分析,计算出两路信号某两点之间的时间值;测量装置的研制解决了以往测量耗时长、精度低,各项功能和性能指标已达到技术指标要求。

关键词:时间测量;信号调理;高速AD采集

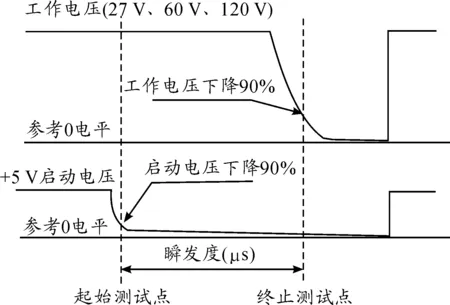

高精度时间自动测量装置是某项目雷达引信装置专用的测量设备,主要功能是测量雷达引信装置产生的引信信号的瞬发度(时间值),引信信号波形如图1所示,+5 V启动电压下降90%时刻为起始测试电,引信电压下降90%时刻为计时终止点,瞬发度就是使用高速AD采集卡的触发采集功能计算出起始测试点与终止测试点之间的时间间隔。研制高精度时间自动测量装置是一项非常重要的配套工作,关系到整个项目装置的可靠性、安全性和风险评估。为了满足对瞬发度的准确、可靠、快速的测量,它具有以下突出特点:具有装置自检功能,包括各功能板卡的自检等;具有测量通道的精度校准功能;具有全自动化测量功能;具有多通道选择可控功能;测量范围0~100 μs,精度±1 μs内;抗恶劣环境 (低温-40℃、高温65℃)。

1测量装置的组成及工作原理

1.1 测量装置的组成

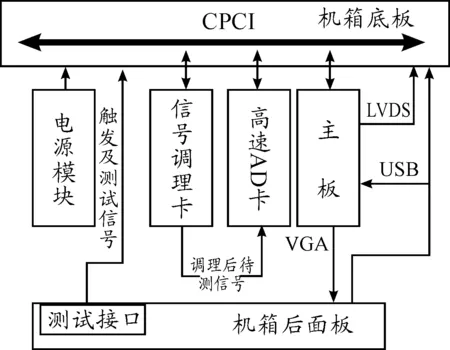

本测量仪采用3U标准CPCI结构嵌入式装置,由x86主板、高速AD采集卡、信号调理卡、电源模块、机箱底板以及显示器组成,此组成构建了一个信号调理和信号采集、处理装置。高速AD采集卡和信号调理卡通过CPCI总线与主板互连,CPCI接口选用PLX公司的PCI9054桥芯片,装置组成框图如图2所示。

图1 信号测试示意图

图2 装置组成框图

1.2 测量装置工作原理

所有被测信号共5路接入信号调理卡,通过上位机软件控制信号调理卡内部的继电器,对被测信号进行通道选择,只选择其中需要测量的一路信号,同时断开其他通道的信号,选通后的被测信号经过信号调理电路将信号电压幅值按比例缩放到高速AD采集卡的量程范围(±20 V)内,再接入高速AD采集卡Ch2,+5 V电压启动信号接高速AD采集卡的Ch1。高速AD采集卡用+5 V电压启动信号作为触发信号,触发电平设置在+5 V电压下降90%(瞬发度测试的起始点)位置,即0.5 V。采集完后,高速AD采集卡产生中断,通知上位机软件读取数据,上位机软件计算测试起始点和测试终止点之间的间隔点数,乘以高速AD采集卡的采样周期,计算出瞬发度的值。

为保证信号采集结果的准确性,本测量仪采用最大频偏约65 PPM的精密晶振为高速AD卡提供65 MHz时钟源,确保瞬发度测量精度在±1 μs内。每个通道采样长度8 192点,测量范围达126 μs。

1.3 误差分析

采样周期由65 MHz精密晶振提供,精密晶振最终的输出频率fO由标称频率 fL和频偏 fE决定,如式(1):

(1)

最大频偏约65 PPM,即fEmax=6.5×10-5,1个时钟周期误差如式(2)计算得到,TE≈1.0×10-12s。

(2)

(3)

(4)

瞬发度时间TPmax最长不超过100 μs,需要时钟周期个数由式(3)得到,N=6 500,整个测试周期的累积误差可由式(4)得到,E≈6.5 ns,远高于1 μs的精度指标。

2装置硬件设计

2.1 高速AD采集卡设计

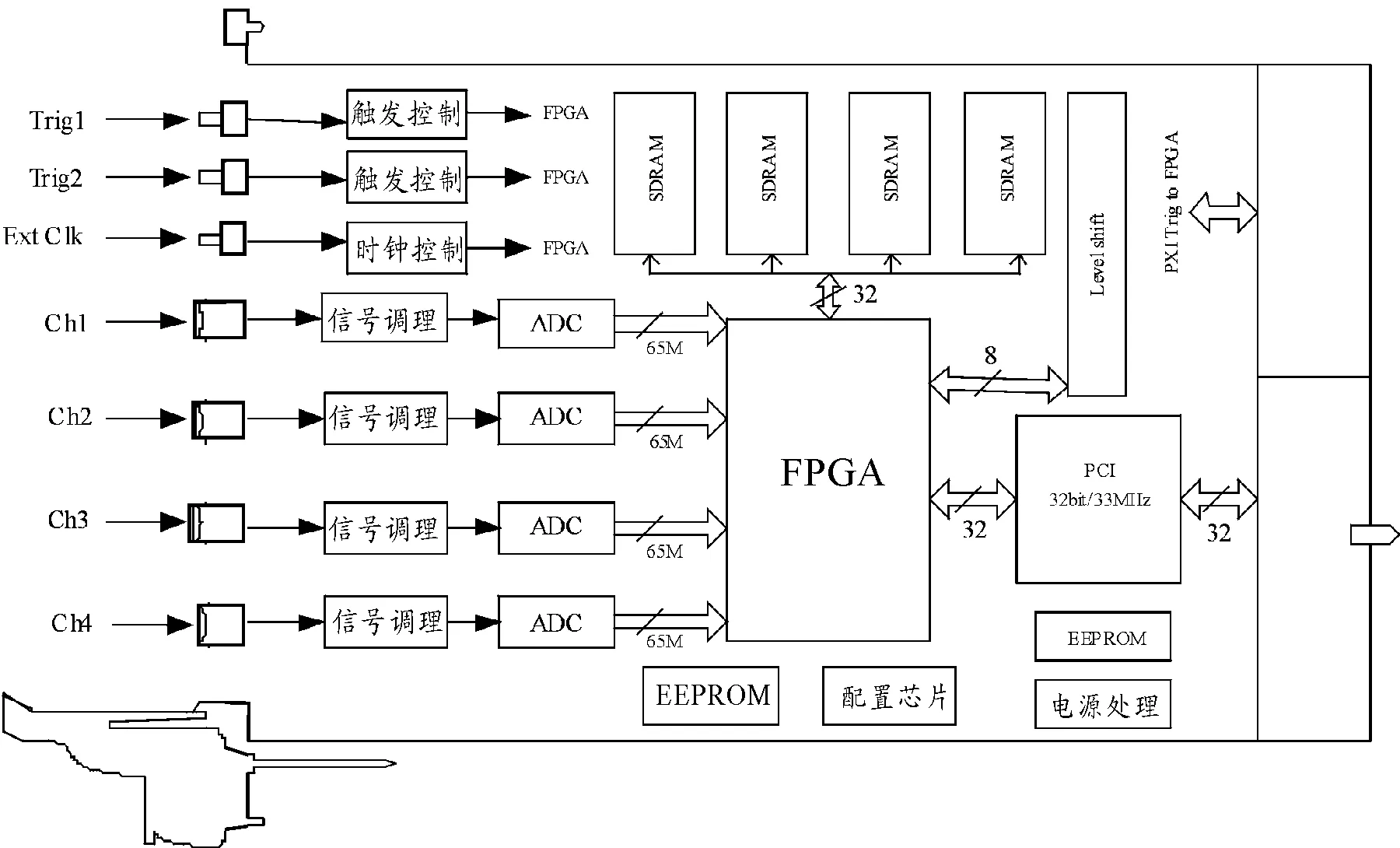

高速AD采集卡包括通道前端的交直流耦合电路、信号调理电路、模数转换器、可编程控制单元、本地FIFO缓存和PCI接口,原理框图如图3所示。

图3 高速AD采集卡原理框图

模数转换器芯片采用Analog公司的AD9245,该芯片是一款高速、高性能,转换精度14位的ADC,最高采样频率为65 MSPS,输出数据编码使用二进制补码形式输出。FPGA作为高速AD采集卡的可编程控制单元,负责信号的采集、处理、传输和触发模式等逻辑控制。

2.2 信号调理卡设计

信号调理卡以信号预处理、信号通道选择和信号转接为主要功能,原理框图如图4所示。

图4 信号调理卡原理框图

被测信号有3种不同的电压幅值:27 V(2路)、60 V(2路)、120 V(1路),根据测量要求,信号调理卡首先对被测信号加额定电阻和电容,再进行比例分压处理,将被测信号幅值按比例缩放到高速AD采集卡的量程范围(±20 V),但只有选通的信号传入高速AD采集卡。信号调理卡的继电器通道设计为闭环电路,用以反馈电路状态给上位机软件以确定继电器通道工作是否正常。FPGA作为信号调理卡的可编程控制单元,负责继电器通/断控制、继电器状态传输等逻辑控制。

3装置软件设计

本测量装置使用Windows XP操作装置,在Windows环境下,应用层软件要实现对硬件的IO操作、中断处理等,需要通过运行在内核层的设备驱动程序来实现,所以装置软件由板卡的WDM设备驱动软件和装置测量软件组成。为了方便驱动程序和应用程序的交互,板卡的各个功能封装成动态链接库(dll),应用程调用库里对应的API完成想要的功能,本装置的软件组成架构如图5所示。

图5 装置软件组成框图

3.1 驱动软件设计

板卡驱动软件采用VC6.0+DDK+DriverStudio方式进行编写,DriverStudio中的DriverWorks中包含WDM驱动程序框架代码生成向导DriverWizard,在生成的框架编写板卡功能驱动代码。DriverWorks带有许多类库,DriverWorks的KMemoryRange类封装了IO访问的操作,设备驱动程序使用这个类的成员函数ind和outd读写板卡的寄存器,KInterrupt类建立中断对象和关联中断服务程序。

3.1.1调理板卡驱动软件设计

驱动程序完成对调理卡的IO的访问。动态链接库通过驱动程序完成:打开信号调理卡、关闭信号调理卡、选择被测的信号通道、获取通道选择状态、PLX9054配置芯片的读写(PLX9054配置芯片保存各个通道电压比例系数)。

3.1.2高速AD采集卡驱动软件设计

驱动程序完成对高速AD采集卡的IO访问、中断处理、读取高速AD采集卡上FIFO的AD数据。

动态链接库通过驱动程序完成对板卡的采集控制:打开高速采集卡、关闭高速采集卡、采集参数设置、触发参数控制、采集状态获取、读取采集完成的数据、启动/停止采集、PLX9054配置芯片的读写等功能(PLX9054配置芯片保存校准比例系数)。

3.2测量软件设计

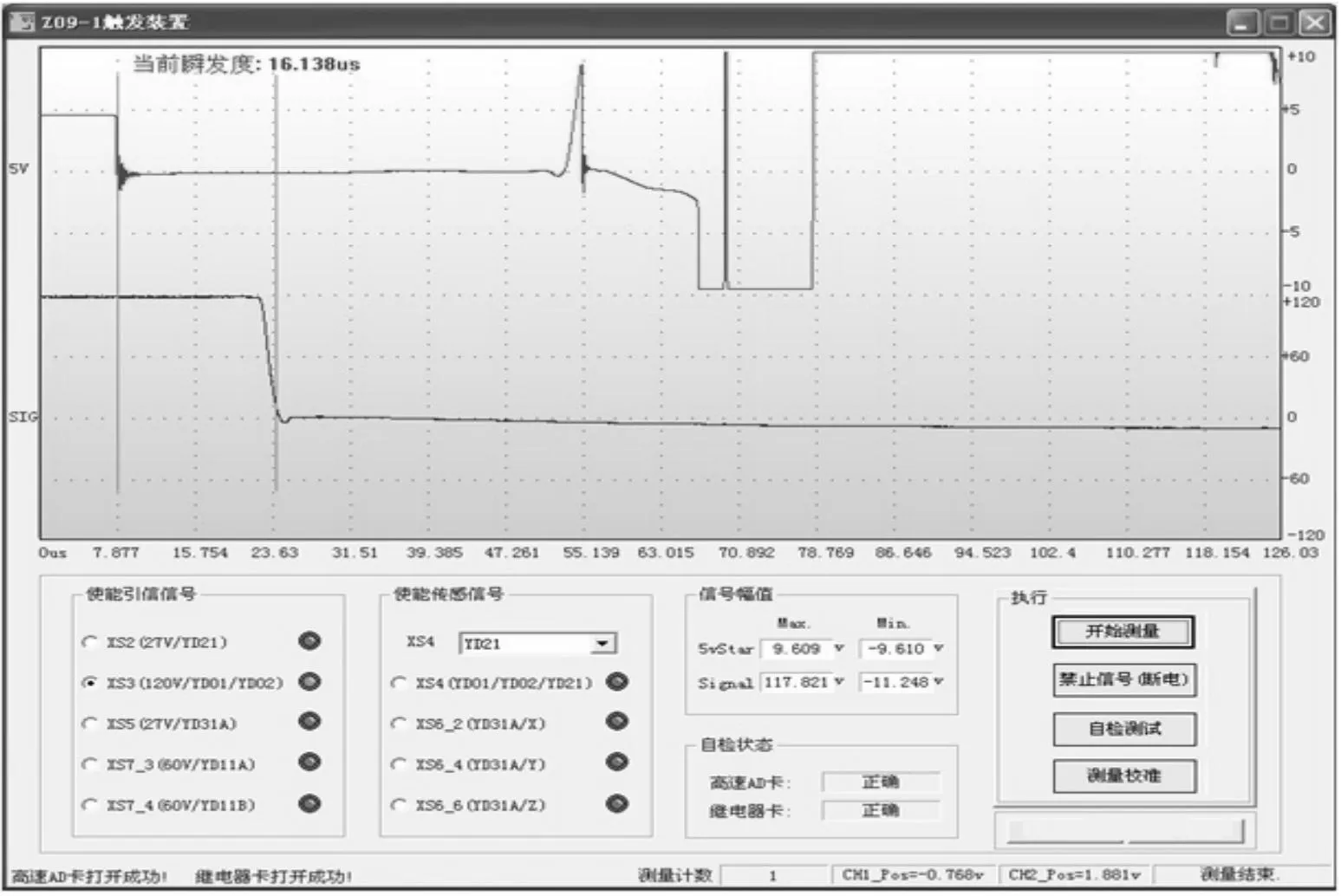

基于VC++6.0的人机界面具有操作简便、功能丰富、运行稳定的特点,用 VC++ 6.0开发的上位机测量软件,不仅可以实时采集每个信号的AD数据,而且可以进行板卡自检和测量校准。该软件主要功能模块包括:装置初始化、被测信号选择、自检测试、测量校准、启动测量以及计算结果显示等,测试结果如图6所示。

图6 测量软件主界面

3.2.1装置初始化模块

打开高速AD 采集卡,初始化高速采集卡的采集参数:设置高速采集卡采集量程、采集频率、预触发模式、预触发位置、触发电平、下降沿触发等参数。打开信号调理卡,所有的继电器处于关闭状态。

3.2.2被测信号选择模块

根据用户选择的信号打开相应的继电器,读取继电器通道状态,判断此继电器是否正常打开。

3.2.3自检测试模块

对板卡初始化,若初始化成功则对板卡的关键寄存器进行读写操作,对比读写是否正确,若正寄存器读写正确无误,依次打开各个继电器,并且检查继电器通断状态,然后显示自检结果。

3.2.4测量校准模块

由于电子原器件性能及装置响应等因素的影响,实际测量值与理论值存在极小的差异,为了消除这种影响,装置要进行测量校准。用泰克信号发生器产生两路固定相位差的信号,相位差作为基准值,启动校准,程序对两路信号进行多次测量,取平均值,基准值与实测的平均值相比得到校准比例系数,把此比例系数存入PLX 9054配置芯片,用于正式测量的校准。

3.2.5启动测量模块

启动测量,即启动高速AD采集卡采集数据,建立数据读取线程,此线程首先等待采集完成中断,然后读取数据,软件对数据进行计算处理。

3.2.6数据计算模块

用+5 V启动信号作为触发信号,0.5 V作触发电平,采用预触发方式,预触发点数为测试起始点,计算被测信号电平在预触发点数后面下降到90%的位置作为测试终止点,计算测试起始点和测试终止点之间的间隔点个数,乘以采样周期,算出时间值并显示在界面上,计算时间关键代码:

startPos=PRE_TRIG_POS;

//signal falling value 90%

ch2ThreadVal =signalADbuf[PRE_TRIG_POS]*float(0.9);

fval = signalADbuf[PRE_TRIG_POS];

for(i=PRE_TRIG_POS;i { if((fval-signalADbuf[i]) >= ch2ThreadVal) //falling edge { endPos = i; break; } } timeValue = (endPos-startPos )/float(65.0);//time unit:us 4结束语 本测量装置在研制中,针对性采取诸如滤波、模拟地与数字地间的隔离、电源隔离等一些抗干扰措施,为提高信号采样的准确性和减少外部信号干扰,所有连接线均采用高速屏蔽线,连接器选用射频连接器。在软件设计方面,采用了分层和模块化设计思想,层次分明,功能明确,易于使用。该测量装置在经历了各项试验后,操作方便,工作正常、稳定、可靠,目前已在某型号项目成功应用。 参考文献: [1]PLX Technology Inc.PCI9054 Data Book Version2.1[M].US:PLX Technology Inc,2000. [2]武安河,邰铭,于洪涛.Windows 2000 /XPWDM 设备驱动程序开发[M].北京:电子工业出版社,2003:351-376. [3]杨甘霖,蔡远文,姚静波,等.基于CPCI总线的运载火箭脉冲信号多路采集卡[J].兵工自动化,2012, 31(9):75-77. [4]陈亮,江明,林园胜.基于PSO算法的PID控制器参数优化研究分析[J].重庆工商大学学报:自然科学版,2014,31(5):77-80. [5]童鹏,吴新建.PCI9054 芯片接口设计中若干问题的深入研究[J ].电子技术应用,2005,31(10):64-66. [6]孙灯亮.数字示波器原理和应用[M].上海:上海交通大学出版社,2012. (责任编辑杨继森) 收稿日期:2014-11-15 作者简介:张京(1967—),女,工程师,主要从事计算控制技术研究。 doi:10.11809/scbgxb2015.07.026 中图分类号:TP274 文献标识码:A 文章编号:1006-0707(2015)07-0100-04 本文引用格式:张京,龚俊,袁霞,等.高精度时间自动测量装置的设计与实现[J].四川兵工学报,2015(7):100-103. Citation format:ZHANG Jing,GONG Jun,YUAN Xia,et al.Design and Implementation of Automatic High Precision Time Measurement Device [J].Journal of Sichuan Ordnance,2015(7):100-103. Design and Implementation of Automatic High Precision ZHANG Jing,GONG Jun,YUAN Xia,QIN You-lun (Department of Basic Electronic Engineering, No. 58 Research Institute of China Ordnance Industries, Mianyang 621000, China) Abstract:This paper introduced an automatic high precision time measurement device, and expounded the hardware and software design method. The measurement device did the signals regulation of the input signal, and then sent it with the start signal to the high speed AD acquisition card, finally analyzed the acquired data collected through the CPCI bus from motherboard and calculated out between two signals’ time value. The measurement device solved the problem of time-consuming, low precision for previous system, all function and performance parameters of the device has already reached the technical requirements of the users. Key words:time measurement; signals regulation; high speed AD sample _______________________ 【信息科学与控制工程】

Time Measurement Device