基于FPGA的高效机载视频采集及预处理方法

2015-12-19姜宏旭李辉勇刘亭杉段洣毅张萍

姜宏旭,李辉勇,刘亭杉,段洣毅,张萍

(北京航空航天大学 计算机学院,北京100191)

近年来,无人机在军用和民用领域均获得了广泛应用,其承担的首要任务是通过机载视频编码系统实时获取和处理视频信息并及时传送到地面控制中心[1].随着光电载荷技术的发展,在视频分辨率不断提高的同时,视频模式也呈多样化发展,除可见光视频外,还有红外、数码相片等[2].为了适应机载应用的发展,需要高性能多模式视频编码系统的支持,然而机载应用的特殊性要求系统在追求高性能的同时,还要考虑系统的可靠性和低功耗[3].

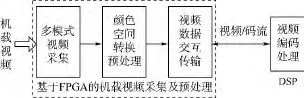

基于现场可编程门阵列(FPGA)的机载视频采集及预处理系统的主要功能单元包括多模式视频采集、颜色空间转换和视频数据交互传输.多模式视频采集单元是基于Camera Link接口实现机载多模式视频数据的实时采集.文献[4]面向嵌入式系统,选用FPGA基于FIFO(First Input First Output)机制解决了Camera Link相机和DM642之间无法直接连接的问题.文献[5]为了完成高清实时视频通信,采用FPGA实现了Camera Link接口的视频采集,可以满足高清视频数据的实时采集.然而这些设计都侧重于Camera Link接口功能的实现,忽略了在视频采集过程中数据错误的控制.目前的研究缺乏对视频采集过程中出现的数据错误进行有效控制,在一定程度上难以保证视频数据的可靠性,尤其是针对机载应用,及时可靠地获取清晰的视频信息显得尤为重要.

颜色空间转换预处理单元的主要功能是将视频的颜色空间从RGB转换到YCbCr.机载视频采用Camera Link接口输入,其视频是RGB格式,然而大多数视频编码标准使用YCbCr颜色空间[6-7].因此FPGA除了实时采集视频图像数据外,还要担负颜色空间转换任务.然而颜色空间转换中有多个浮点乘运算,这在FPGA上实现时,往往需要设计专门的浮点乘法器进行处理,从而占用大量的逻辑资源和布线资源,增加系统功耗.为了提高系统效能,通常的方法是采用查找表(LUT)方式实现乘法运算,文献[8-9]均对LUT进行了优化处理以提高计算效率.因为LUT需要占用的计算资源较少,所以在实际应用中十分有效.然而,直接使用LUT实现的不足之处在于随着变量数值位宽的增大,LUT占用的存储空间将不断增大.为了解决这个问题,文献[10-12]分别针对LUT的存储空间优化进行了一定研究.虽然在一定程度上节约了存储空间,但是效果不是十分明显.文献[13-15]中针对截断式乘法器的研究为本文的处理提供了一种新的思路.对于嵌入式应用程序而言,截断乘法不需要缓存乘法运算结果的完整长度,这有效减少了乘法运算占用的存储空间并降低了功耗.所以,为了进一步降低视频预处理中浮点乘法引入的动态功耗,本文综合LUT和截断处理技术,设计了一种高低位分离的截断式LUT乘法器,实现了高效低功耗的RGB到YCbCr颜色空间转换.

视频数据交互传输单元的主要任务是实现视频数据和压缩码流在FPGA与DSP之间的高效传输.在FPGA与DSP之间存在大量视频数据的频繁传输,这会占用DSP的部分处理资源,影响编码器性能.针对这个问题,本文采用SRIO接口,设计了一种以FPGA为控制核心的数据交互机制,尽量减轻DSP的负担,使DSP专注于视频编码运算,降低处理延时.

1 可靠的多模式视频采集方法

在机载多模式视频编码系统设计中,视频输入接口需要支持多种模式的视频图像数据,然而在具体实现中发现,不同模式视频切换过程中,容易出现视频数据错位现象.其原因是在模式切换的瞬间,视频数据的发送方和接收方出现了信号不同步的问题.为了有效降低数据错误的影响,本节设计了一种具有自动检错机制的视频数据采集方法,实现错误的自动检测和及时恢复.

1.1 自动检错控制器设计

视频图像采集主要是根据输入的帧有效信号与行有效信号来确定开始采集的时机,即在帧有效信号与行有效信号均有效(即为1)时,采集视频图像的有效数据.为了防止视频模式切换时错误视频数据积累,设计了一种自动检错控制器.首先做如下符号定义:

1)视频模式为 Model[n],其中 n=1,2,…,7;

2)分辨率为 Wn×Hn,其中 n=1,2,…,7;

3)每行采集到的数据为Wcapture;

4)行有效信号为Lsignal.

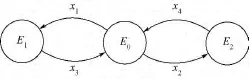

图1 自动检错控制状态机模型Fig.1 State machine model of automatic error control

自动检错控制器初始状态为E0,事件x1(或x2)发生时进入状态E1(或E2),并做出相应的控制动态r1(或r2).当r1(或r2)执行结束后,控制器自动回到状态E0.E1和E2为瞬间状态,它们随着控制动作的结束而自动结束.从上述错误恢复机制可知,在视频模式切换时,如果出现数据错误,自动检错控制会将错误控制在一帧数据内,甚至是一行数据内,可有效避免错误积累.

1.2 多模式视频鲁棒采集方法

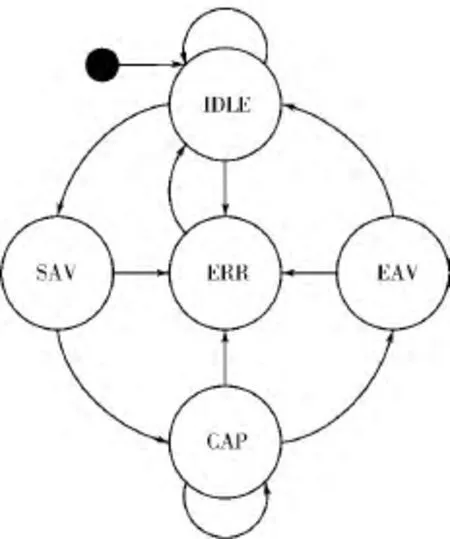

在FPGA平台上实现视频采集时的状态机一般包括4个状态:IDLE,SAV,CAP和EAV状态,为了解决不同模式视频切换过程中出现的数据采集错误,保证视频数据的可靠性,本文在上述4种采集状态中加入自动检错机制,并将本文设计的自动检错控制器ERR加入到状态机.这样在视频采集过程可以动态实时地检测视频采集的正确性,一旦出现错误,可以及时恢复处理,如图2所示是可靠的视频采集方法状态机模型.

图2 可靠的视频采集方法状态机模型Fig.2 State machine model of robust video capture method

IDLE状态标示当前处于空闲状态,当视频SAV码到来时,进入SAV状态.SAV状态是视频采集起始状态,CAP状态是视频采集阶段,若检测到视频结束码则进入EAV状态,否则继续采集视频.EAV状态是视频采集结束状态,下一步进入IDLE状态.可靠的视频采集具体过程如下:

1)在IDLE状态时,检测到同步信号到来,检查后续标志码校验位出错则进入ERR.

2)SAV状态检查标志码不是起始码,进入ERR.

3)CAP状态设置采集数据量计数,检测采集到的视频数据是否与当前模式视频数据一致,若有错误,则进入ERR,否则继续采集.

4)EAV状态检查标志码不为结束码,则进入ERR,否则在EAV状态完成时,行计数增加,当顶场数据和一帧数据采集结束时,核对行计数值是否符合当前模式的视频格式,若不符合则进入ERR.

5)ERR状态即进行自动检错控制,当出现标志码错误时,表明视频同步信号出错,对采集当前视频帧数据进行清空处理;当出现视频数据量不足或超量时,进行相应的补齐和截断操作.在系统恢复后,由ERR进入IDLE状态,等待采集新一帧视频数据.

综上所述,可靠的视频采集方法是在原有视频采集过程基础上,有效利用视频同步信号,实时检测所采集的视频数据是否符合当前需要处理的视频模式,一旦出现错误,系统能够及时采取措施恢复正常工作,控制错误扩散,避免了错误数据积累.

2 高效低功耗色彩空间转换

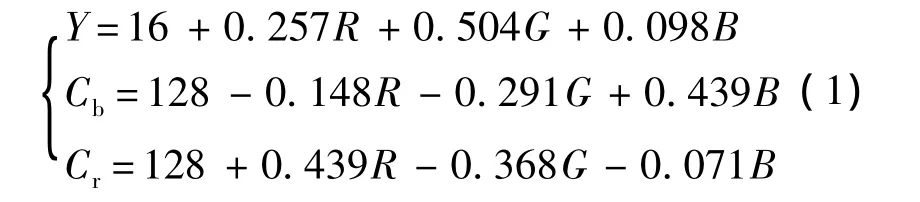

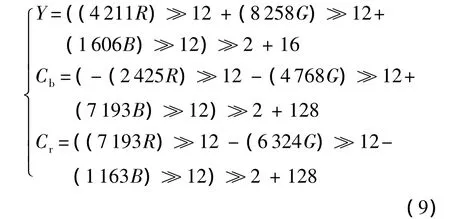

根据 ITU-R BT.601 标准,R,G,B 3 个分量分别用8 b 表示,取值范围为[0,255],并且 R,G,B与 Y,Cb,Cr的关系为

根据式(1),本文对常系数乘法的定义如下:

式中,A为常系数,采用W b的二进制数表示;X为R,G和B中任一个分量的值,采用8 b的无符号二进制数表示;F为乘积,如果乘法运算的结果为完整长度,则F是(8+W)b的二进制.显然,当直接使用LUT完成乘法运算时,存储乘积的数据表占用(8+W)·28b,这对于嵌入式系统来说是不能接受的.在RGB到YCbCr转换时,Y,Cb和Cr的位宽与R,G和B的位宽一致,均采用8 b的二进制无符号数表示.为了减少存储开销,引入截断处理的方法对LUT进行优化设计,提出了一种高低位分离的截断式LUT乘法器.

2.1 高低位分离的截断式LUT乘法器设计

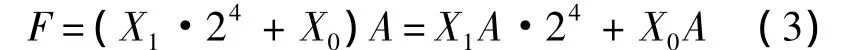

由于式(2)中的X位宽为8 b,如果直接建立乘积的查找表,采用8 b输入,需要28=256个存储空间,这在一定程度上增加了FPGA的资源消耗.由于大部分FPGA的构造均采用4输入LUT或6输入LUT,结合这个特点,本设计采用高低位分离的LUT,将X分为高4b和低4b,分别建立部分乘积的查找表:LUT0和LUT1.这样设计会增加一次加法运算,但存储空间变为2×24=32,极大地节约了存储空间.此外,充分使用FPGA内部的4输入LUT,避免了资源浪费.因此,式(2)被分解为

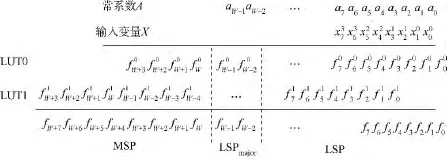

式中X0和X1为4b的二进制数.根据X0和X1的取值不同得到的部分积不同,将部分积的值建立查找表,在进行乘法运算时,根据乘数的值进行查表获取相应的部分积,再将部分积进行加法运算即可得到乘法的最终乘积.为了进一步节省存储空间,对LUT中存储的部分积进行截断处理.将部分积中几乎不影响最终乘积的尾数丢弃,具体丢弃策略需要在计算精度和存储空间之间进行权衡.表1所示为截断的部分积查找表.

表1 截断式部分积的LUT(T-LUTn,n=0或1)Table1 LUT based on truncated partial product(T-LUTn,n=0 or 1)

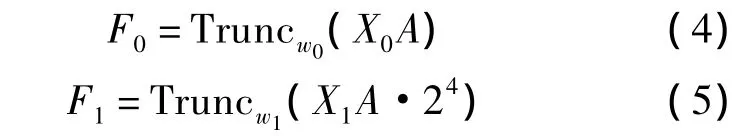

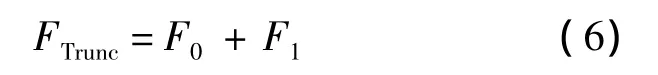

设Fn(n=0或1)分别为查找表T-LUT0和T-LUT1的输出值,即

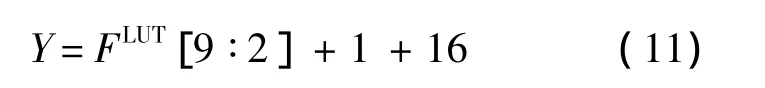

如图3所示为基于高低位分离的截断式查找表乘法器结构示意图,其乘法器输出乘积FTrunc可表示为

由于对乘法的部分积进行了截断处理,所以计算结果会存在一定的误差,其误差率Erate可表示为式中,F为不使用截断处理的精确乘积;FTrunc为使用截断处理的乘积.

图3 基于高低位分离的截断式LUT乘法器结构Fig.3 Truncated LUT multiplier structure based on the separation of high and low bits

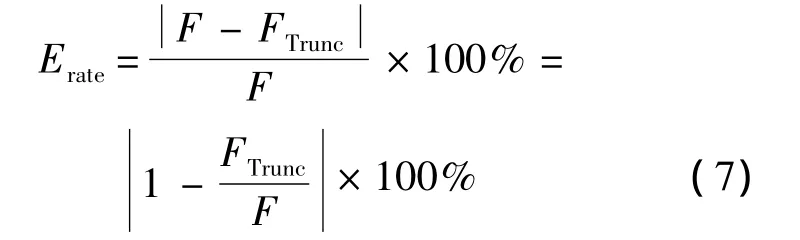

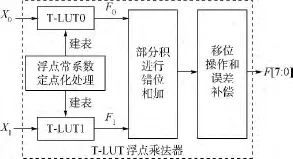

由式(7)可知,误差率是存储空间和截断处理的权衡值,截断处理中丢弃的位数越多,误差率越高.分析截断处理的过程,由于最终乘法结果需要一个8 b输出,在计算过程中所产生的部分积的尾部字节最终都会被丢弃.因此为了节省存储空间,在建立LUT时就将作用不大的尾部字节丢弃,这样对最终乘积的影响不大,又能节省LUT的存储空间.如图4所示为W b×8 b部分积相加计算过程示意图.对应上述两个分离部分积,对最终乘积结果影响较大的是MSP(Most Significant Part)部分,在运算时必须保留.对于 LSP(Least Significant Part)部分,其主要能量集中在LSPmajor部分,因此为了补偿由于截断处理带来的误差积累,根据四舍五入的思想,可对LUT中存储的每一个部分积增加两位作为差错补偿.根据最终乘积结果,如果LSPmajor<10(二进制),则直接丢弃;如果LSPmajor≥10,则对MSP部分进行加1.因此,进行截断处理时,根据n的不同,LUT0和LUT1中存储的部分积位宽分别为w0=6和w1=10.

图4 Wb×8 b部分积阵列Fig.4 Wb ×8 b partial product array

2.2 高效的RGB到YCbCr空间转换

为了便于在FPGA平台上实现RGB到YCbCr转换,首先对运算中的浮点系数进行定点化处理,然后再采用基于高低位分离的截断式LUT乘法器完成乘法运算.浮点数进行定点化是通过将浮点数扩大一定的倍数(左移若干位)取整数部分,计算完成后再将结果缩小相应的倍数(右移相应的位)得到最终计算结果.因此确定位移位数要权衡变换后的精度损失和计算量.图5所示是通过统计的方式将系数乘以相应的扩大倍数完成定点化以后,再右移相应的位数,将结果与原系数计算结果比较获得的精度损失的柱状图,x坐标表示式(1)中的各个常系数,y坐标表示定点化后损失的精度值.

图5 系数的精度损失比较Fig.5 Comparison of coefficient precision losses

由图5可知位移14 b时可达到较高精度,与位移15 b相比,精度损失差距很小.考虑到计算复杂度的因素,尽量减少运算的位数,位移位数不宜过多,本文采用位移14 b的方法进行定点化扩展.经过定点化处理后的式(1)可以表示为

由式(8)可知,RGB到YCbCr颜色空间转换过程中的每个乘法运算都是位宽为8 b的变量与位宽为14 b的常系数相乘获得中间结果.为了减少精度损失,参照截断处理策略,在计算时保留两位进行误差补偿,可将式(8)转为

以Y为例进行说明,Y可以表示为

式中,A为14 b的常系数;R,G和B的位宽均为8 b;C为常数16.

根据式(3)进行高低位分离,并按表1建立相应的乘法部分积查找表.为了节省存储空间,对查找表中的部分积进行截断处理.这样将乘法操作转换成查表和加法操作,得到乘积FLUT1,FLUT2和FLUT3,位宽为10 b.在计算FLUT时,需要进行右移2位操作,为了进一步降低误差,在进行移位操作时,根据四舍五入原则判断要丢弃2位FLUT[1][0]的值,如果 FLUT[1][0]<10,则对结果影响不大,可以直接移位丢弃;如果 FLUT[1][0]≥10,则 Y的值为

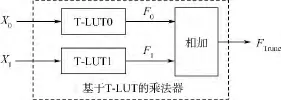

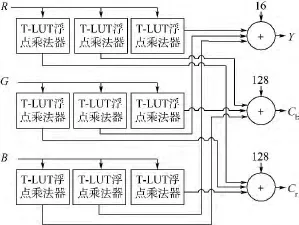

计算Cb和Cr的值时用与计算Y的处理方法相同,这样不但能实现四舍五入操作,并且避免移位操作,加速计算过程.图6所示为基于高低位分离的截断式LUT(T-LUT)浮点乘法结构示意图.图7所示为基于T-LUT浮点乘法器的RGB到YCbCr转换结构示意图.

图6 基于高低位分离的截断式LUT浮点乘法器结构Fig.6 Truncated LUT float multiplier structure based on the separation of high and low bits

图7 基于T-LUT浮点乘法器的RGB到YCbCr转换结构Fig.7 RGB to YCbCrconversion structure based on T-LUT float multiplier

采用查找表方式可以将乘法运算转换成只有查表和加法运算的操作.在处理过程中,查表操作的速度相对于加法运算会快很多,因此整个处理过程的速度限制在加法运算上.针对运算过程中含有的多次加法运算,本文采用加法流水的方式提高加法运算速度,从而进一步提高颜色空间转换效率.

3 基于SRIO的高效数据传输机制

在FPGA+DSP架构的视频处理系统中,通常利用FPGA扩展视频接口并完成视频预处理任务,利用高性能的通用DSP作为主要运算器件完成复杂的视频处理功能.FPGA与DSP间的高速视频数据的互连传输是系统正常工作的基本前提.SRIO(Serial Rapid I/O)总线作为一种高可靠、高效能和具有良好扩展性的开放总线标准,已经成为高性能嵌入式系统中高速互连的主要传输方式之一.本文采用SRIO作为数据传输的高速链路,SRIO协议中规定了多种事务类型,它们可以分为两种数据传输方式:直接IO/DMA(direct IO/Direct Memory Access)传输方式和消息传递.直接IO/DMA传输方式速度较快,支持本地器件通过SRIO协议读写对端器件的存储器,但是本地器件需要知道对端存储结构,同时需要考虑存储器读写同步;消息传递不需要知道对端器件存储结构,只需知道对端ID和邮箱号就可以完成数据传输.

为实现SRIO高速传输,降低DSP的SRIO传输负担,本设计使用FPGA通过直接I/O传输方式完成SRIO总线上所有视频数据的收发工作,采用消息传递方式完成FPGA与DSP同步.如图8所示为以FPGA为控制核心的数据交互机制示意图.FPGA为SRIO传输控制核心,这样设计的优势是DSP基本不需要参与SRIO传输控制工作,SRIO视频数据传输过程对DSP基本透明,DSP可以专注于视频处理计算.

图8 以FPGA为控制核心的数据交互机制Fig.8 Data exchange mechanism based on FPGA control

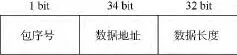

当原始视频数据由FPGA传入DSP时,FPGA通过SWRITE事务发送所有数据,SWRITE事务通过SRIO总线能够实现对DSP的DDR3存储器直接写操作,写操作过程对DSP核完全透明.考虑到存储读写同步,要求此过程中DSP禁止访问该视频数据缓冲区.在DDR3中视频数据写满一帧后,通过DOORBELL事务通知DSP,解除该存储区域访问锁;当视频码流由DSP传入FPGA时,FPGA通过NREAD事务请求读取处理后的视频码流数据,DSP的SRIO硬件接口直接读取DDR3对应存储位置,组织NREAD响应事务包,发送处理后视频数据到FPGA,此过程对DSP核完全透明.为实现存储读写同步,DSP在完成一帧视频数据压缩处理后,向FPGA发送一个控制包通知FPGA回收该帧的压缩码流.控制包的格式如图9所示,包括包序号、数据存储地址和数据长度.其中包序号用1 b表示,相邻的两个包序号采用0或1表示,以示区别,数据存储地址根据SRIO协议规范采用34b表示;数据长度根据一帧数据压缩后的码流量采用32 b表示.

图9 控制包格式Fig.9 Format of control packet

综上所述,以FPGA为控制核心的SRIO传输过程,一方面可以减少DSP在SRIO传输过程中的时间开销,使DSP可以专注于视频处理过程,降低编码延时;另一方面,简化本系统支持的SRIO事务种类,只使用3种SRIO事务完成视频数据传输过程,节约FPGA逻辑资源,有助于提高SRIO传输速度.

4 实验与分析

如图10所示为FPGA+DSP架构的机载视频采集及预处理结构示意图,其主要功能单元包括视频采集、颜色空间转换和视频数据交互传输.FPGA作为协同处理器承担着关键的纽带作用,其中的一个主要任务是快速地从机载记录仪获取多模式原始视频图像数据,实时完成色彩空间转换后传入DSP进行压缩处理.

图10 机载视频采集及预处理结构Fig.10 Structure of airborne video capture and preprocessing

为了评估本文方法的有效性,FPGA平台选用 Xilinx公司的 XC5VSX50T-1ff665,采用 SRIO接口与DSP建立数据传输通路.使用Verlog硬件描述语言在FPGA平台上实现本文设计的方法,首先验证视频采集和预处理的正确性和性能,然后针对预处理后的数据完成高速传输测试.

4.1 视频采集及预处理测试

为测试设计中视频采集方法的可靠性,分别使用和不使用自动错误检错机制的方法进行测试,在视频模式不断切换过程中,观察采集的视频图像正确性.经实验测试,使用自动错误检错机制的方法可以正确采集视频数据,而不使用自动检错机制时,采集的视频容易出现错误积累,引起视频错位.如图11所示为实验比较图(分辨率为720像素×576像素).

图11 视频采集的实验比较图Fig.11 Comparison of video capture experiment

实验表明,本文提出的可靠的视频采集方法利用视频同步信号自动检查视频数据量是否正确,能够在视频数据丢失或中断后及时恢复,将错位数据控制在一帧甚至一行视频内,避免产生错误累计,提高了视频源的可靠性.

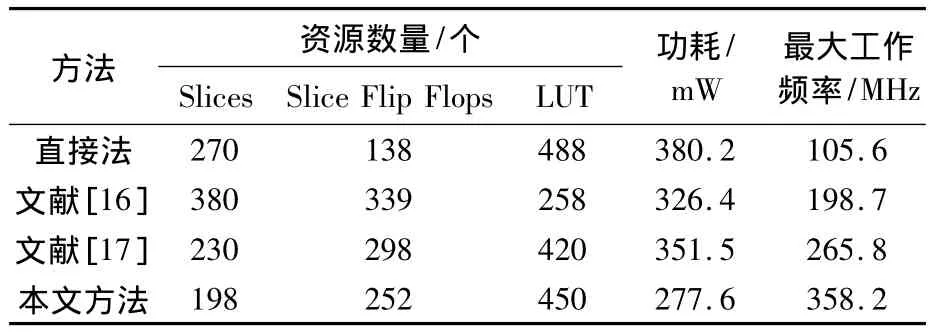

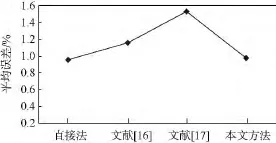

为测试颜色空间转换的有效性,分别实现了本文方法、直接法、文献[16]的方法和文献[17]的方法.当用直接法实现时,在计算前应将浮点数定点化,并且在计算过程中不使用DSP48进行运算;对于文献[16]和文献[17]的方法,编译环境的配置和程序实现分别参考对应的文献.对于本文提出的方法,为了节省FPGA上的运算资源,也不使用DSP48.表2比较了在相同条件下4种方法的资源消耗和性能测试结果.

表2 资源消耗及性能比较结果Table2 Resource consumption and performance comparison results

由表2可知,与直接法相比,本文方法最大工作频率为358.2 MHz,是直接法的3.5倍,证明该方法能显著提高转换速度.之所以本文方法使用了较多的Slice Flip Flops,是因为流水线技术占用FPGA上较多的寄存器.文献[16]和文献[17]的方法节省了LUT,但是使用了更多的 Slices和Slice Flip Flops.FPGA中具有较多的LUT资源,本文提出的方法使用了略多的LUT资源,获得了更高的频率.并且本文方法采用基于截断处理建立的LUT,减少了存储空间和计算位宽,因此降低了电路的动态功耗.实验证明本文方法的功耗比其他几种方法减少了15% ~27%.图12所示为实验性能比较图.

图12 性能比较Fig.12 Performance comparison

因为在截断处理的过程中,丢弃的是对结果影响最小的尾数,并且采用误差补偿机制减小了误差,因此本文提出的方法几乎不影响计算结果的精度.图13显示了平均误差补偿的结果.

图13 平均误差比较Fig.13 Comparison of mean error

4.2 高效的数据传输测试

根据目前机载视频处理系统的需求,通过FPGA采集和预处理后需要传入DSP的原始视频最大数据率小于500 Mb/s,因此设置FPGA与DSP之间SRIO通路为1.25 Gb/s工作模式.

测试FPGA通过SRIO的SWRITE(流写)事务向DSP传输数据,并存储到DDR3.SWRITE事务包头信息极短,有效数据打包率高于NWRITE(普通写)等其他事务.SRIO协议规定每个事务包最大有效数据载荷为256 B,因此使用携带256 B数据的SWRITE事务可以实现最高速率的SRIO传输过程.在1.25 Gb/s模式下,由于8b/10b编解码SRIO数据传输率为1 Gb/s,SWRITE事务打包率为95%,此时SRIO理论最高有效数据传输速率为950Mb/s.经过实验测试,使用本文方法其数据发送速率可达880 Mb/s,达到理论值传输速率93%,完全可以满足系统需要的最大数据传输率.

测试FPGA通过SRIO读取DDR3速率和正确性,在1 s内FPGA向DSP连续发送NREAD请求事务,在FPGA端接收NREAD响应事务,检查收到数据正确性并记录收到数据包数量,测试结果为812 Mb/s,达到理论值传输速率90%,数据正确无误.

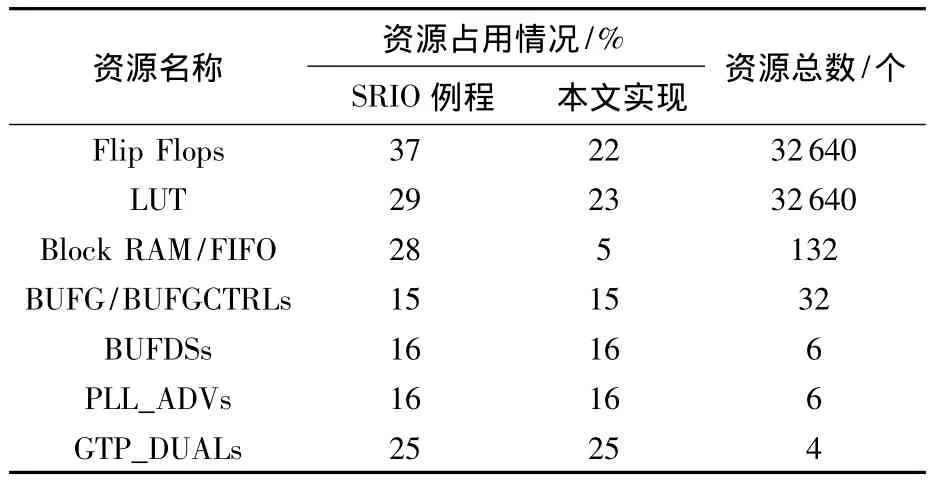

以XC5VSX50T-1ff665型FPGA为目标器件,本文方法能够完成FPGA与DSP的SRIO自动收发;SRIO例程没有实际应用价值,只提供了利用ChipScope工具手动发送SRIO事务功能.如表3所示测试统计本文实现SRIO方法和SRIO例程逻辑资源使用情况.

表3 SRIO资源占用情况统计Table3 SRIO resource occupancy statistics

对比资源使用情况可知:

1)本文方法占用较少Flip Flops和LUT资源.Flip Flops反映芯片寄存器资源,LUT是FPGA实现逻辑运算的查找表.本文简化SRIO事务实现,保留了常用的 SWRITE,NREAD及 DOORBELL事务,删除不常用的SRIO原子事务操作,同时简化了SRIO地址计算过程和存储数据过程;SRIO例程支持所有事务类型,存储过程和地址计算过程复杂,同时ChipScope核也占用较多资源.

2)本方法占用较少Block RAM/FIFO资源.根据视频传输特点,本文采用以行为单位的收发缓存队列,大小仅为6个视频行,大大降低FPGA上需要的缓存数据量;同时采用收发缓存队列结构实现数据缓存,相比SRIO例程中使用的双端口RAM控制简单、实现方便,可靠性更高.

3)其他资源占用一致.BUF主要用于SRIO高频输入时钟和数据缓存;PLL_ADVs用于SRIO高频时钟网络减少抖动;GTP_DUALs是FPGA集成的高速收发器,实现SRIO硬件接口.

综上所述,本文结合视频传输特点,在占用较少逻辑资源情况下,设计实现了FPGA与DSP间SRIO的高速互连,数据传输速率达到理论值90%以上.

5 结论

本文针对机载视频采集及预处理系统中的关键功能单元从可靠性、高效性角度进行了研究,主要包括:

1)设计了一种可靠的多模式机载视频采集方法,通过增加自动检错机制,有效避免了采集错误的积累.

2)针对颜色空间转换中浮点运算占用资源多,功耗大的问题,设计了一种基于高低位分离的截断式LUT乘法器,并实现了一种高效低功耗的颜色空间转换方法,提高了系统性能.

3)采用SRIO数据传输协议在FPGA与高性能DSP之间设计了一种由FPGA为控制中心的高效数据交互策略,可以减少DSP在数据传输过程中的资源开销,使其更加专注于视频处理,提高系统性能.

此外,本文设计的方法已经成功应用于机载视频压缩系统中,取得了良好的效果.

References)

[1] Blair J B,Rabine D,Wakeet S.et al.High-altitude laser altimetry from the global hawk UAV for regional mapping of surface topography[C]//AGU Fall Meeting Abstracts.San Francisco:AGU,2012:885.

[2] Adams S M,Levitan M L,Friedland C J.High resolution imagery collection utilizing unmanned aerial vehicles(UAVs)for postdisasterstudies[J].Bridges,2014(10):1143879634-1143879667.

[3] Saffar S,Abdullah A.Vibration amplitude and induced temperature limitation of high power air-borne ultrasonic transducers[J].Ultrasonics,2014:54(1):168-176.

[4] Wang D Y,Tao X H,Hu R.The design of the interface for camera link and DM642[C]//Control and Decision Conference.New York:IEEE,2010:2914-2916.

[5] 贾建禄,王建立,郭爽,等.基于Camera Link的高速图像采集处理器[J].液晶与显示,2010,25(6):914-918.Jia J L,Wang J L Guo S,et al.High speed image grabber and processor based on Camera Link[J].Chinese Journal of Liquid Crystals and Displays,2010,25(6):914-918(in Chinese).

[6] Singh S K,Kumar S.Novel adaptive color space transform and application to image compression[J].Signal Processing:Image Communication,2011,26(10):662-672.

[7] Li S A,Chen C Y,Chen C H.Design of a shift-and-add based hardware accelerator for color space conversion[J].Journal of Real-Time Image Processing,2013,9:1-14.

[8] Liu Z G,Du S Y,Yang Y,et al.A fast algorithm for color space conversion and rounding error analysis based on fixed-point digital signal processors[J].Computers & Electrical Engineering,2014,40(4):1405-1414.

[9] Meher B K,Meher P K.A new look-up table approach for highspeed finite field multiplication[C]//2011 International Symposium on Electronic System Design.New York:IEEE,2011:51-55.

[10] Meher P K.LUT optimization for memory-based computation[J].IEEE Transactions on Circuits and Systems II:Express Briefs,2010,57(4):285-289.

[11] Meher P K.New approach to look-up-table design and memorybased realization of FIR digital filte[J].IEEE Transactions on Circuits and Systems I:Regular Papers,2010,57(3):592-603.

[12] Meher P K.New look-up-table optimizations for memory-based multiplication[C]//Proceedings of the 12th International Symposium on Integrated Circuits.New York:IEEE,2009:663-666.

[13] Kuang S R,Wu K Y,Yu K K.Energy-efficient multiple-precision floating-point multiplier for embedded applications[J].Journal of Signal Processing Systems,2013,72(1):43-55.

[14] Eswari S.Design of low error and power fixed width multiplier by using compensation function[J].International Journal of Engineering Research and Technology,2013,7(2):755-760.

[15] Balamurugan S,Srirangaswamy B,Marimuthu R,et al.FPGA design and implementation of truncated multipliers using bypassing technique[C]//Proceedings of the International Conference on Advances in Computing,Communications and Informatics.Berlin:ACM,2012:1111-1117.

[16] Xue J,Cao X.Color space conversion based on FPGA[C]//IEEE International Conference on Computer Science and Automation Engineering.New York:IEEE,2012:422-425.

[17] Yang Y,Peng Y H,Liu Z G.A fast algorithm for YCbCr to RGB conversion[J].IEEE Transactions on Consumer Electronics,2007,53(4):1490-1493.