用于SVC控制系统的新型软件锁相环的设计与实现

2015-12-15刘育鑫王小红方存洋施胜丹

刘育鑫,王小红,方存洋,施胜丹

(南瑞集团公司,江苏 南京 210003)

0 引言

静止型无功补偿设备(Static Var Compensation,简称SVC)是一种提高系统电压稳定性,抑制冲击负荷所造成的电压波动的先进技术[1]。SVC系统一般由一次系统和二次控制系统组成。一次系统由晶闸管控制电抗器(Thyristor Control Reactor,简称TCR)、和滤波电容器(Filter Capacitor,简称FC)组成。可实现较快、连续的动态无功功率调节,具有反应时间快,运行可靠,能平衡有功,适用范围广和价格便宜等优点[2]。

锁相环(Phase Locked Loop,简称PLL)在SVC控制系统中的主要作用是为SVC控制系统提供快速、稳定、高精度的同步信号。锁相环的性能,关系到整个SVC控制系统的同步以及晶闸管器件触发控制的精准度,是控制系统的重要环节。

依靠硬件的模拟锁相环有器件饱和及易受电源和环境温度变化等缺点[3];基于三角函数正交性以及自适应滤波原理的相位跟踪闭环控制系统,它克服了模拟锁相环的缺点,但这种方法采用了傅立叶分析法,使跟踪速度变慢[4];依靠软件计算的α β坐标开环锁相环对畸变电压敏感等缺点[5];在电压不平衡条件下为了抑制负序电压的影响,dq锁相环一般以100 Hz分量衰减系数为PI控制器设计指标,因此也存在着响应速度慢的缺点[6]。

此外,目前绝大部分控制设备厂家的控制装置结构都是以DSP作为逻辑运算单元,并采用FPGA实现信号采集、通信处理等功能[7]。详细设计了一种用于SVC控制系统的新型软件锁相环,充分利用控制装置硬件资源,在DSP单元编码实现软件锁相模块,在FPGA实现锁相计数器,软件锁相模块完成系统同步电压的锁相调节控制,锁相计数器代替复杂的积分环节,产生锁相角θ。该控制方式易于工程实现,在电压不平衡、电压跌落、频率突变等条件下,仍可快速、可靠的实现锁相。

1 软件锁相环设计与实现

1.1 软件锁相环原理

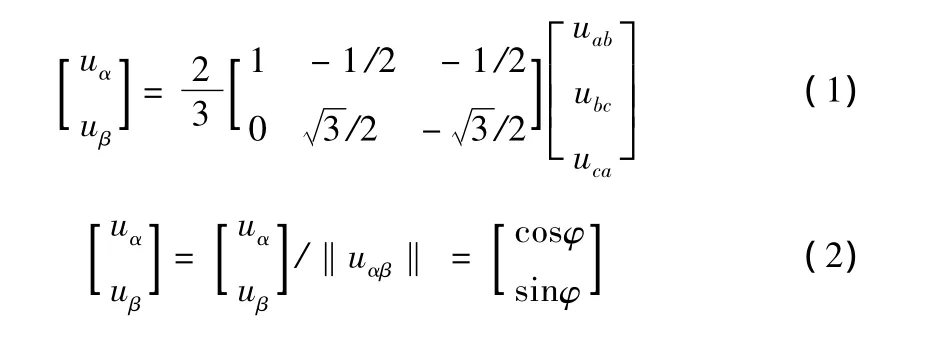

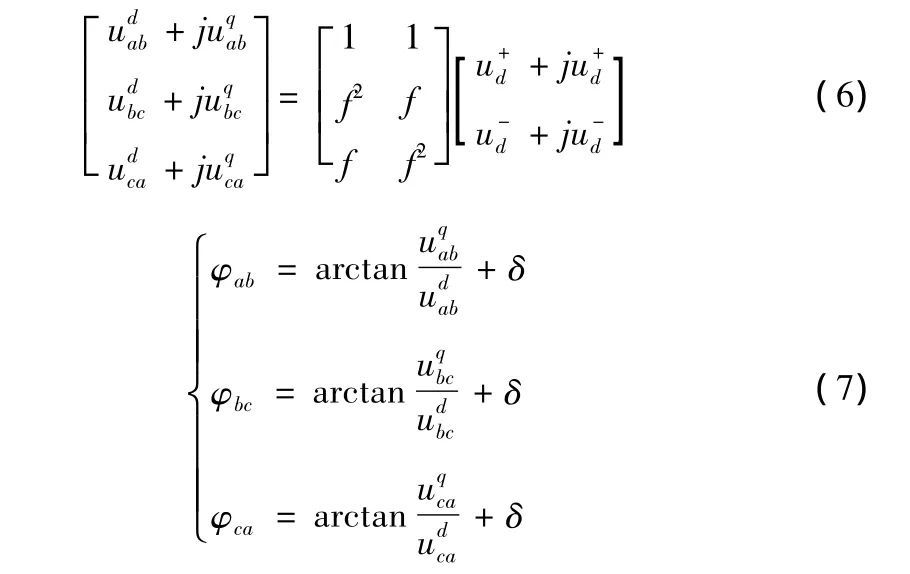

软件锁相环采用瞬时无功理论锁相原理,其原理如图1所示。首先将电压信号由abc坐标系转化到α β坐标系。θ为电压向量u与α轴的夹角。为方便计算,进行标幺化处理。由于TCR一般采用三角形接线方式,所以选取uab做为同步电压。

为滤除负序分量,进行dq坐标转换前,需要进行相序分解。二倍频陷波器可实现相序分离,但其滤波器设计较为复杂,不利于工程实现,同时受频率波动的影响较大,因此本系统中采用了延时相序分解法,处理简单,利于工程实现。

上标“+”表示正序分量,“-”表示负序分量。根据公式(2),可得将(t)、(t)带入正序同步旋转坐标系,进行dq坐标系转换,将(t)、(t)带入负序同步旋转坐标系,进行dq坐标系转换。θ'为d+轴与α轴的夹角。

此外,考虑到三相电压不平衡、采集和计算延迟,锁相环模块还应计算出三相校正角度φab、φbc、φca。

图1 锁相环原理图

1.2 软件锁相环的实现

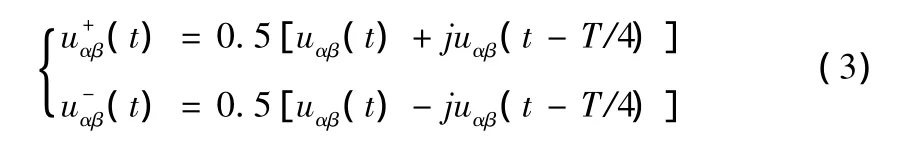

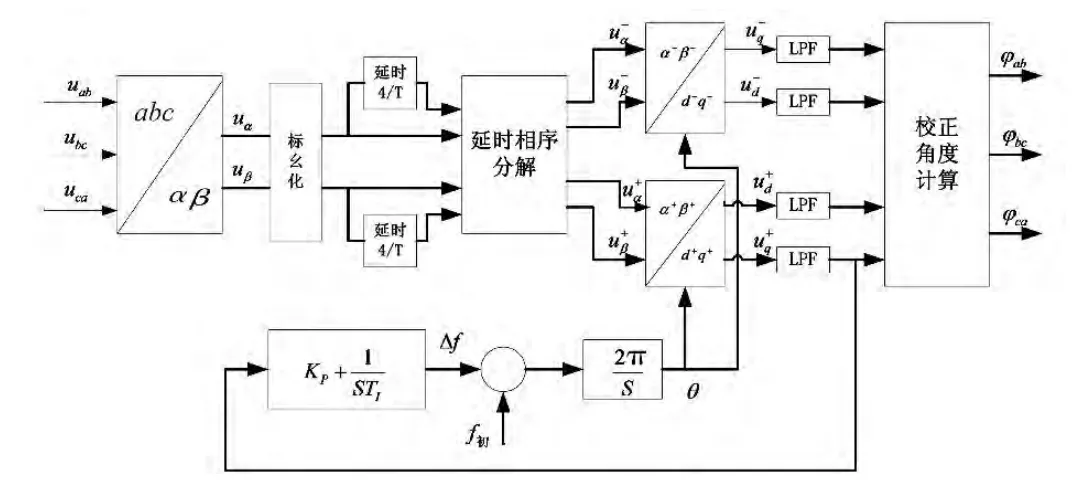

目前大部分控制设备厂家的控制装置结构都是以DSP作为逻辑运算单元,并采用FPGA实现信号采集、脉冲触发、通信处理等功能。本新型软件锁相环实现所基于的控制系统硬件平台选用目前业界可靠性、功能和处理能力最有优势的嵌入式CPU、DSP和大容量的FPGA进行设计,同时采用符合工业标准的高速以太网和IEC标准的数据采集的光纤通道作为数据传输链路,内部采用高可靠、高实时、高效率的数据交换接口。采用ADI公司的32位/40位扩展精密浮点DSP,型号为ADSP-21469,作为逻辑单元,并采用Xilinx公司出品的Spartan6作为FPGA单元。硬件平台结构如图2所示。

图2 SVC控制系统硬件平台

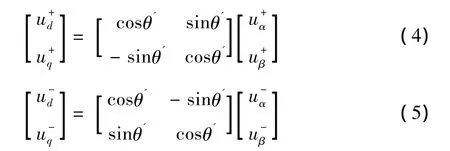

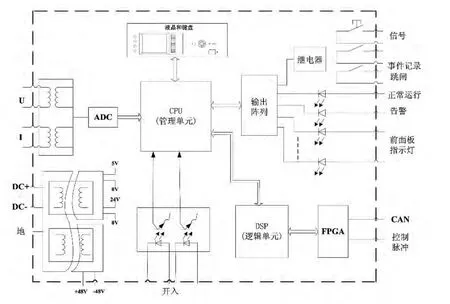

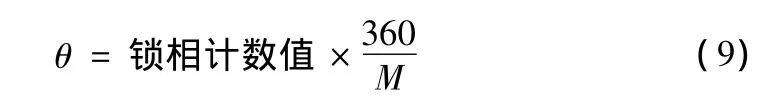

锁相过程中,锁相角θ由PI调节器输出的频率值经过积分环节计算得出。通过软件实现积分计算较复杂。本新型软件锁相环的实现,充分利用控制装置资源,在DSP单元用C语言编码实现软件锁相模块,任务周期为100 μs。用FPGA实现锁相计数器,软件锁相模块完成系统同步电压的锁相调节控制,锁相计数器代替复杂的积分环节,产生锁相角θ,软件锁相模块配合锁相计数器,实现锁相功能。图3为用FPGA锁相计数器代替积分环节后的锁相原理图。

具体实现过程为:软件锁相模块按图1的锁相原理进行锁相控制,将PI控制器输出值Δf,加上初始电网频率f初,从而得到了锁相的频率输出。将锁相所得的频率换算为锁相计数器计数周期最大值M,传递给FPGA锁相计数器。

FPGA锁相计数器设计原则为:一个标准工频周期的值20 MS,对应的计数值为50 000,即FPGA的计数时钟周期为400 NS,即,计数频率为2.5 M。由于标准工频周期下,一周波对应的计数值为50 000,FPGA锁相计数器的计数值作为触发控制的时间参考,触发控制精度可以达到0.007 5(°)。

FPGA锁相计数器按照M进行循环计数,当达到最大值时,计数器清零,重新开始计数。软件锁相模块在每个执行周期内读取当前FPGA锁相计数器的计数值,换算为当前锁相角θ,用于锁相调节。

软件锁相模块将当前FPGA锁相计数器的计数值提供给SVC系统作为触发控制的时间参考。即SVC控制系统将计算出的晶闸管触发角度,转换为与FPGA锁相计数器计数值相对应的设置值K。当FPGA锁相计数器计数值达到该设置时,SVC控制系统发触发脉冲,使得对应的晶闸管导通。

图3 用FPGA锁相计数器代替积分环节后的锁相原理图

2 仿真分析及试验结果

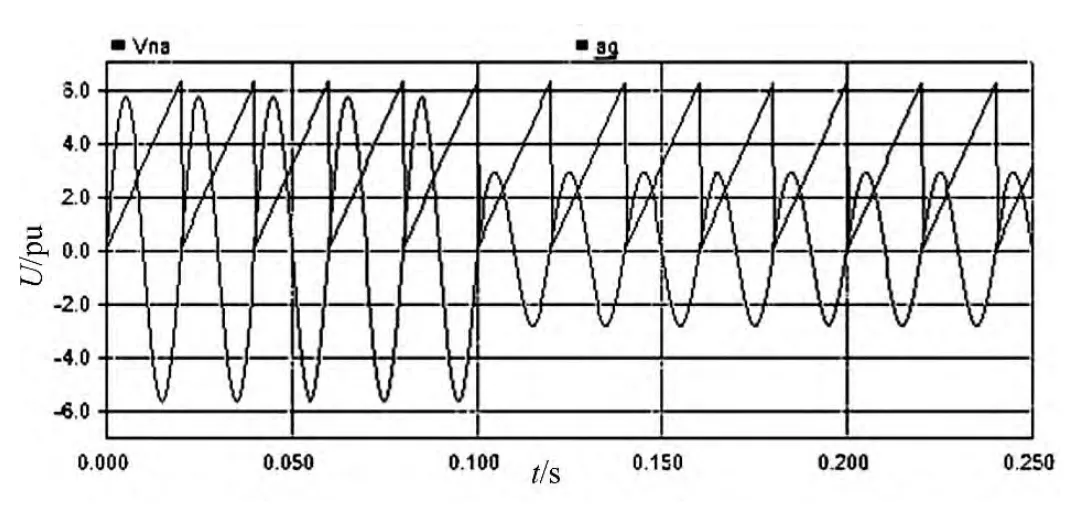

通过PSCAD/EMTDC软件搭建锁相环模型,当t=0.1时刻,发生电压跌落,仿真结果如图4所示。当t=0.1时刻,发生频率突变,f由50 Hz突变到46 Hz。仿真结果如图5所示。可看出在电压跌落、频率突变情况下,本实用新型锁相环仍可快速、可靠的实现锁相。

图4 电压跌落时锁相环仿真图

图5 频率突变时锁相环仿真图

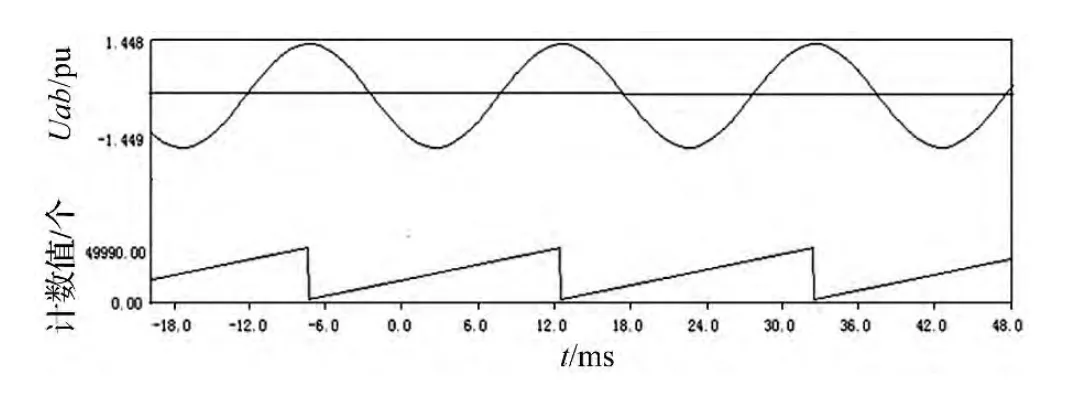

为验证该新型软件锁相环的实际应用效果,基于2.2节所述的硬件平台,实现软件锁相环。在SVC动态模拟实验室进行测试,额定电压为1 kV。

控制平台具有录波功能,能手动或根据录波触发条件自动录波,产生标准格式的comtrade文件。通过录波分析软件,可以看到电流电压、锁相环、触发脉冲等系统工况。图6为锁相环波形图,Uab是同步电压。从图中可知当前锁相环最大计数值为49 990,即当前系统电压频率为49.99 Hz。

图6 锁相环波形图

3 结束语

锁相环在SVC控制系统中的主要作用是为SVC控制系统提供快速、稳定、高精度的同步信号。锁相环的性能,关系到整个SVC控制系统的同步以及晶闸管器件触发控制的精准度,是控制系统的重要环节。本文设计了一种用于SVC控制系统的新型软件锁相环,采用基于瞬时无功理论的锁相原理,以FPGA计数器替代复杂的积分环节,产生锁相角θ,在电压不平衡、电压跌落、频率突变等条件下,仍可快速、可靠的实现锁相。

通过PSCAD/EMTDC软件的仿真和以ADSP-21469和FPGA-Spartan6为核心的控制平台的动态模拟实验研究,验证了该新型软件锁相环的正确性和可行性,易于工程实现,参数修改方便,可方便的实现与SVC控制系统的其他模块接口,具有良好的应用效果。

[1]林海雪.现代电能质量的基本问题[J].电网技术,2001,25(10):5-12.

[2]王兆安,杨君,刘进军.谐波抑制和无功补偿[M].北京:机械工业出版社,1998.

[3]韩民晓,尤勇,刘昊.线电压补偿型动态电压调节器(DVR)的原理与实现[J].中国电机工程学报,2003,23(12):49-53.

[4]周卫平,吴正国,夏立.基波相位和频率的高精度检测及在有源电力滤波器中的应用[J].中国电机工程学报,2004,24(4):91-96.

[5]王海军,陈潜.云广直流工程锁相环功能分析及仿真研究[J].南方电网技术,2009,3(4):60-63.

[6]丁菊霞,张华俊,张秀峰.基于平均值理论的无锁相环三相电路谐波电流检测方法[J].电测与仪表,2010,47(5):43-47.

[7]张吉,宋斌,唐成虹.保护测控装置嵌入式采样新平台的研制[J].电力系统自动化,2011,35(2):89-92.