基于CUDA平台的AVS视频编码应用

2015-11-23颜海峰刘忆宁

黄 海 钟 婍 颜海峰 刘忆宁

(桂林电子科技大学数学与计算科学学院,广西 桂林 541004)

基于CUDA平台的AVS视频编码应用

黄 海 钟 婍 颜海峰 刘忆宁

(桂林电子科技大学数学与计算科学学院,广西 桂林 541004)

文章通过研究AVS视频编码在可编程图形处理器上实现,充分利用图形处理器的高性能并行运算能力和浮点计算能力加快编码的处理程。实验结果表明,在保证视频质量的同时,大大提升了AVS视频编码的速度。

GPU;视频编码;GOP级的并行编码;CUDA

1 引言

AVS(Audio Video coding Standard,音视频编码标准)是由我国自主制定的、享有自主知识产权的第二代信源编码技术标准。2006年2月,国家标准化管理委员会正式批准AVS的第二部分(AVS1-P2)即视频部分为国家标准。AVS视频标准的编码效率比以前的MPEG4等视频编码标准的编码效率高。

H.264/AVC视频编码标准的压缩效率非常高,但是H.264/AVC的这种高压缩效率的获得却是以较高的计算时间复杂度为代价的,而且H.264编码算法在CPU上展开了大量的优化策略,技术上也已经非常成熟,因此,研究人员开始探索其他一些能提高压缩编码效率的方式。近些年来,由于图形硬件的飞速发展和更新,GPU(Graphic Processing Unit,图形处理器)的计算速度也在不断地提高,此外它还拥有非常强大的并行计算能力与浮点运算能力。2007年6月,NVIDIA公司推出了CUDA(Compute Unified Device Architecture,统一计算设备架构)编程模型,该模型在利用GPU的通用计算资源上更加地充分合理[1]。而目前的PC机在实时编解码高清晰视频时,其处理器要承担的压力非常大。因此研究以CUDA为基础的视频编解码,对于编解码时计算时间的减少、整个编码性能的提高等方面都有着非常重要的现实意义。

2 解决方案

无论是音视频编码技术自身还是该产业的应用背景在经过了十几年的发展之后,都有了许多明显变化,很多新的方法相继提出。目前音视频产业领域有四个信源编码标准可供选择,它们分别是:MPEG-2、MPEG-4、MPEG-4 AVC(简称 AVC,也称JVT、H.264)、AVS。按制订者来划分,前三个标准是由MPEG专家组发展制订的,第四个标准是我国自主制订的。按发展阶段划分,第一个标准属于第一代信源标准,其余三个标准皆为第二代信源标准。按编码效率这一主要技术指标进行比较:MPEG-4的编码效率是MPEG-2编码效率的1.4倍,AVS和AVC的编码效率相差无几,都是MPEG-2编码效率的两倍多[2]。

随着显卡的进一步发展以及越来越多的开发人员参与到GPU的并行计算开发中来,GPU的并行计算能力和访存带宽的速度都有了很大的提高,而且在显示图像时GPU还做一些了优化处理,它的计算能力实际上已经超越了通用的 CPU[3]。如此强大的芯片如果只是拿来作显卡的话未免太过大材小用了。因此,NVIDIA公司推出了CUDA架构,它使显卡除了用于图像计算以外还有其他的功能。GPU的专长在于密集型数据的处理和并行计算,所以在需要大规模并行计算的领域里CUDA可以大显身手。通用GPU已经能够达到十万的线程数量级,因而,提高GPU的并行计算效率对于提升GOP级的并行计算能力意义重大。

3 实现方案

3.1 ASV原理分析

如图1所示AVS编码器的系统结构。不难发现,AVS使用的是一种混合编码框架,其中结合了预测和变换技术,这与H.264的编码结构非常相似。图像类型定义为 I帧、P帧、B帧三种,其中I帧的编码模式只能是帧内编码,P帧和B帧的编码模式可以是帧间编码模式和帧内编码模式,两者区别在于P帧是前向预测编码帧,而B帧是双向预测编码帧。码流结构从高到低的语法层次依次为:序列、图像、条带、宏块、块[4]。在这方面上,AVS与 MPEG2 较为类似。AVS1-P2中,块的尺寸大小为 8×8。原始的视频信号在进入编码器后,编码器将根据配置参数对当前帧是进行I帧、P帧还是B帧的编码做出判断。若当前帧是I帧,则只能选择帧内编码模式。帧内编码只需要参考当前帧中重构后的宏块信息而不需要其他帧的已编码信息作为参考。进入编码器的一个新的块和经过帧内预测出来的预测块做减法运算得到残差,再进行变换、量化过程将残差变为量化系数,该量化系数再通过zig-zag扫描成为一维量化系数,最后经过熵编码就能得到编码了的码流。此外,在熵编码前,通过反量化和反变换等过程,就能使得已经量化了的信息得以重构这个块,并在缓存中存储作为后续图像或块编码的参考帧[5]。如果是 P帧,则可以有三种编码模式:SKIP模式、帧内模式和帧间模式。官方参考模型是让P帧遍历以上三种模式,通过计算率失真代价,得到一种最优的编码模式。与I帧相同,P帧的帧内模式也是以视频序列时间上的相关性为基础的,通过参考最近解码后的I帧或P帧使当前待编码宏块得到残差,再经过变换、量化和熵编码步骤得到码流。 AVS中P帧数量的最大参考值为2。P帧中块在 SKIP 模式下编码后的残差为 0,因此只需传输代表SKIP模式的信息,就可以得出预测的运动矢量。AVS中的B帧一样有以上三种编码模式:SKIP模式、帧内模式和帧间模式。但B帧的帧间预测模式是双向的,包含有对称模式(symmetric mode)和直接模式(direct mode)两种,这是B帧与P帧的不同之处。

图1 ASV原理

3.2 GOP级并行编码算法

图像群组(Group of pictures,GOP)是一组连续图像,这些图像来源于以MPEG编码的影片或者视讯串流内部。

图像群组可包含的图像类型如下:

● I-图像/画格(intra coded picture,节点编码图像)参考图像,与一个固定影像类似,并且与其它的图像类型相独立。每个图像群组以此类型的图像作为开始。

● P-图像/画格(predictive coded picture,预测编码图像)包含来自之前的 I-画格或 P-画格的差异资讯。

● B-图像/画格(bidirectionally predictive coded pictures,前后预测编码图像)包含来自之前和/或者之后的I-画格或P-画格的差异资讯。

● D-图像/画格(DC direct coded picture,指示编码图像)用于快速进带。

假设有两个B帧,每个GOP可排成IBBPBBP…序列,且一直到视频结束都将会保持这一排列顺序。IDR图像是GOP的第一个图像,且都是I图像,一个GOP只能有一个IDR图像,而IDR图像以后的图像在进行解码时决不会引用IDR图像之前的图像数据,这就使得GOP之间的并行有了可能。

编码效果的好坏与GOP的长度大小相关。一定的范围内,GOP的长度值越大,每个图像组中能有更多的B帧和P帧,因而压缩编码效率也越高。但是GOP的值也不能取过大,因为会导致编码质量不高,特别是对于场景切换或运动较为剧烈的视频序列的情况。此外,一个GOP中如果出现了严重的丢包现象或者是由其他原因导致的数据错位问题,为减少误码的发生,只有通过获得重新同步,因此要折中考虑GOP的长度值。

GOP的优点:

①可扩展性强:能根据硬件情况适当调整并行线程数。

②线程开销小:整个并行程序的运行过程只需进行一次Fork,由频繁派生、合并线程导致的性能损失在很大程度上得到了减少。

③加速比高:如果各个线程的负载能够平衡,那么加速比会比较高。

④易于实现:每个线程都有比较大的任务量,线程间无需频繁的进行数据同步,程序实现较为容易。

图2 GOP级并行编码

在开始编码视频序列前,要将其分为多个GOP,且每个GOP都要分配一个线程进行编码。编码完成后回到主线程,再完成数据同步并且输出AVS码流。对于非实时编码来说,最好的选择是GOP级并行,一方面因为GOP级并行对目标码流的PSNR、码率等各项指标不会造成影响,另一方面由于GOP之间没有相关性,且编码器能对序列中的任意帧进行随机访问,因此在编码前对帧序列的划分可根据GOP长度大小。划分帧序列后,依据GOP的多少来设置线程的数量。而要实现GOP级并行,编码过程必须要在原始图像序列数满足GOP的长度后才能进行,所以在对实时性有很高要求的应用场合,比如在远程机器人控制、视频会议系统等情况下,GOP级并行显然无法满足要求。

3.3 GPU并行计算模块实现原理

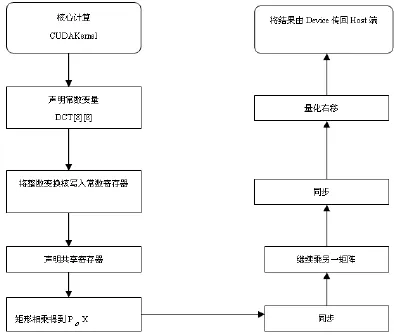

原有的变换编码采用了整数DCT变换,根据之前确定的实现方案,笔者方案的具体实现按照如下的流程图进行,如图 3所示:

图3 变换编码并行实现

主机端在运行函数后得到关于当前块的残差宏块矩阵。然后程序将检测GPU加速是否已由该编码器幵启,或者该客户端是否有可编程 GPU。如果得到检测结果为编码器没有开启 GPU加速,或者无可编程GPU,则编码流程将按照常规的步骤进行串行编码,然后得到--个返回值dc[6],即为变换后的8x8矩阵。如果检测结果是编码器己经幵启了GPU加速并且该客户端有可编程GPU,则将进行Device端编码,也即GPU编码。该编码流程主要分为以下几个步骤:(1)在主机端的内存上为8x8矩阵分配空间;(2)将主机端的代码复制到设备端GPU的显存上:这样我们就在设备端GPU上得到了大小为8x8的Md矩阵,也即残差宏块矩阵;(3)分配Grid和线程Thread,该部分是在主机端分配的,也即指令流需要由CPU产生,然后来操作GPU的行为;(4)核心计算Kernel代码;(5)将计算的结果返回。

而在设备端GPU上,也存在正变换和反变换两次变换。对于设备端GPU的变换代码,有以下流程,设备端变换编码并行实现流程图如图4:

图4 变换编码并行实现设备

由图4,当设备端GPU收到开始计算的指令后,首先做准备工作,即声明常数变量DCT[6],用来存放整数变换核;之后进行如下的计算工作。该步骤的意义在于每一次的计算过程中整数变换核会被调用,存有常数变量则可减少数据的流量和调用的次数,为GPU与CPU的交换省下了带宽。

4 测试结果及分析

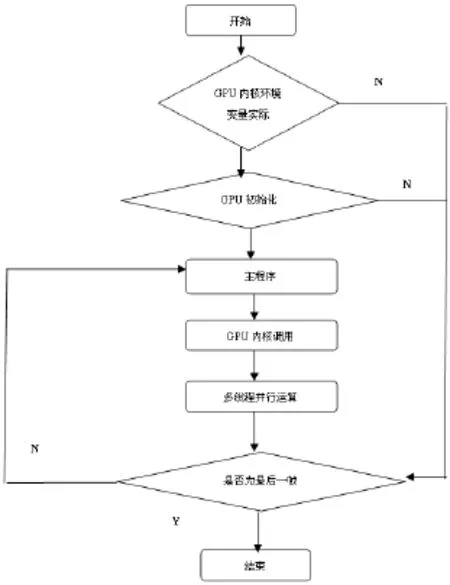

系统设计流程图如图5所示:

图5 系统流程图

测试环境为:

操作系统 Windows 7 Professional(64bit)

处理器 Intel(R) Xeon(R) CPU E5504 @ 2.00GHz×8

内存 12GB

显卡 NVIDIA Tesla C1060×2;NVIDIA Quadro FX380×1

编译器 Microsoft Visual Studio 2008

调试器 Parallel Nsight

表1给出了本文方案与CPU方案的在性能上的对比,不难发现,本文方案的编码速率相比CPU方案有了很大的提升,同时,编码质量也比较好,从而实现了高清视频编码的效果。

AVS video coding applications based on CUDA platform

This paper studies the AVS video coding in programmable graphics processor to take full advantage of the graphics processor, high-performance parallel computing power and floating-point computing power to speed up the process of coding process. Experimental results show that the video quality, greatly enhance the speed of the AVS video coding.

GPU; video coding ;GOP level parallelism coding; CUDA

TN76

A

1008-1151(2015)02-0013-03

2015-01-12

2014年全国大学生创新创业训练计划(XY290398)。

黄海,男,广西玉林人,桂林电子科技大学数学与计算科学学院信息计算专业学生;钟婍,女,江西赣州人,桂林电子科技大学数学与计算科学学院硕士生,研究方向为信息安全;颜海峰,男,广西全州人,桂林电子科技大学数学与计算科学学院教师,研究方向为信息系统安全;刘忆宁,男,河南巩义人,桂林电子科技大学数学与计算科学学院副教授,博士后,研究方向为应用密码学与信息安全。