基于FPGA的VGA图像显示系统的设计

2015-11-17杜宗展王振河冯迎春

杜宗展+王振河+冯迎春

摘 要: VGA(视频图形阵列)是一种标准的显示接口,被广泛应用。根据VGA,FPGA(现场可编程门阵列)的作用原理,设计的基于FPGA的VGA接口可以直接将数据送至显示器,同时增添了关于输出图像灰度等级的设计。与传统设计相比,该设计没有计算机的处理过程,可节省硬件成本,加快数据处理速度,被广泛应用到视频显示领域。

关键词: 现场可编程门阵列; 视频图形阵列; 显示接口; 灰度

中图分类号: TN919?34; TP391.8 文献标识码: A 文章编号: 1004?373X(2015)16?0095?05

Design of VGA image display system based on FPGA

DU Zongzhan1, WANG Zhenhe2, FENG Yingchun2

(1. School of Electrical Engineering, Shandong University, Jinan 250061, China;

2. Maintenance Company, Shandong Electric Power Group Co., Jinan 250061, China)

Abstract: As a standard display interface, VGA (video graphics array) has been widely used. According to the principles of VGA and FPGA (field programmable gate array), the designed VGA interface based on FPGA can send the data to the display directly, and grayscale of the output image was added to this design. Compared to the traditional design, there is no computer processing procedure in the design, which can save the expense of hardware and enhance the speed of data processing. It is widely used to the domain of video display.

Keywords: field programmable gate array; video graphics array; display interface; grayscale

在传统的图像处理系统中,要将图像显示出来,采取的方法是先将图像数据传入电脑,然后经过显示器显示。在这个传输过程中,对图像的控制需要经过CPU,这样既造成资源浪费,一直通过电脑处理还会降低系统的灵活性[1]。利用FPGA(现场可编程门阵列)对VGA(视频图形阵列)显示接口进行设计,数据不需要经过计算机,只在整个系统内部传输。这种设计使得系统的组成规模和硬件设备成本减少,系统的稳定性、扩展性和可靠性得到增强[2?3]。VGA自从推出以来,作为一种标准显示接口在视频、计算机等显示器领域有较广泛的应用[4]。FPGA的特点是容量大、投资少、周期短、灵活性等,FPGA强大的处理功能使其在视频领域得到广泛应用[5?8],成为硬件设计的首选方式之一[9?10]。

1 VGA概述

1.1 VGA接口定义

VGA(Video Graphic Array)视频图形阵列是一种显示标准[11],VGA接口就是显示器经过VGA标准数据输出的接口。VGA视频输出接口一共有15个管脚,如图1所示。在VGA输出接口的15个管脚里面,3条基本色彩线(红、绿、蓝)以及水平、垂直2条控制线是其中最重要的。这5条控制线可以组成8种组合,显示8种色彩。

图1 VGA接口

1.2 VGA显示原理

VGA显示器在显示屏幕上的彩色是由R,G,B(红、绿、蓝)三个基本色组成的,阴极射线管(CRT)发出电子束,打在荧光屏上产生三基色。VGA图像显示器的显示是通过CRT逐行扫描或隔行扫描的方式实现的[12?13],即输入信号在显示器屏幕上方开始从左到右,从上到下逐行扫描。行扫描信号HS控制从左到右扫描、场扫描信号VS控制从上到下的扫描。电子束在扫描完一行后会回到下一行的起始位置,CRT对电子束消隐,用行同步信号HS进行行同步;等所有行扫描结束,场同步信号VS进行场同步,同时进行场消隐,使电子束回到屏幕左上方[14]。

1.3 VGA时序分析

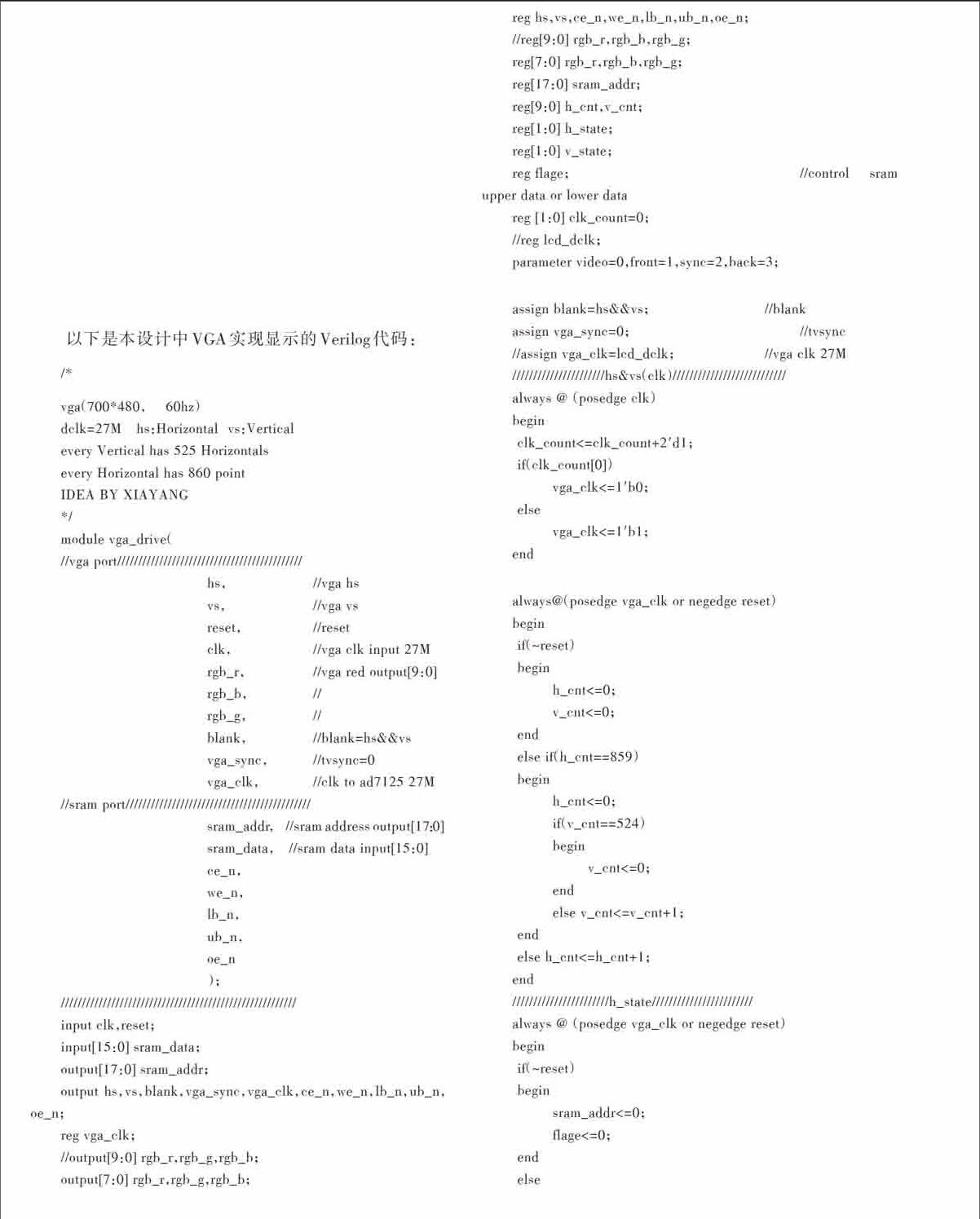

计算机业界根据不同的显示接口制定了多种显示接口协议,VGA是其中的一种[15]。在VGA的显示接口协议中,显示模式的不同是因为分辨率和刷新率不同,因而时序也不同[16]。不同显示模式的时序都由VGA工业标准来控制。设计VGA图像显示时需要注意的是时序的驱动和VGA信号的电平驱动[17]。时序的驱动是设计的关键点,时序若有偏差,显示肯定会不正常,严重情况会损坏彩色显示器。图2为VGA的扫描时序图。

图2 VGA行(场)扫描时序图

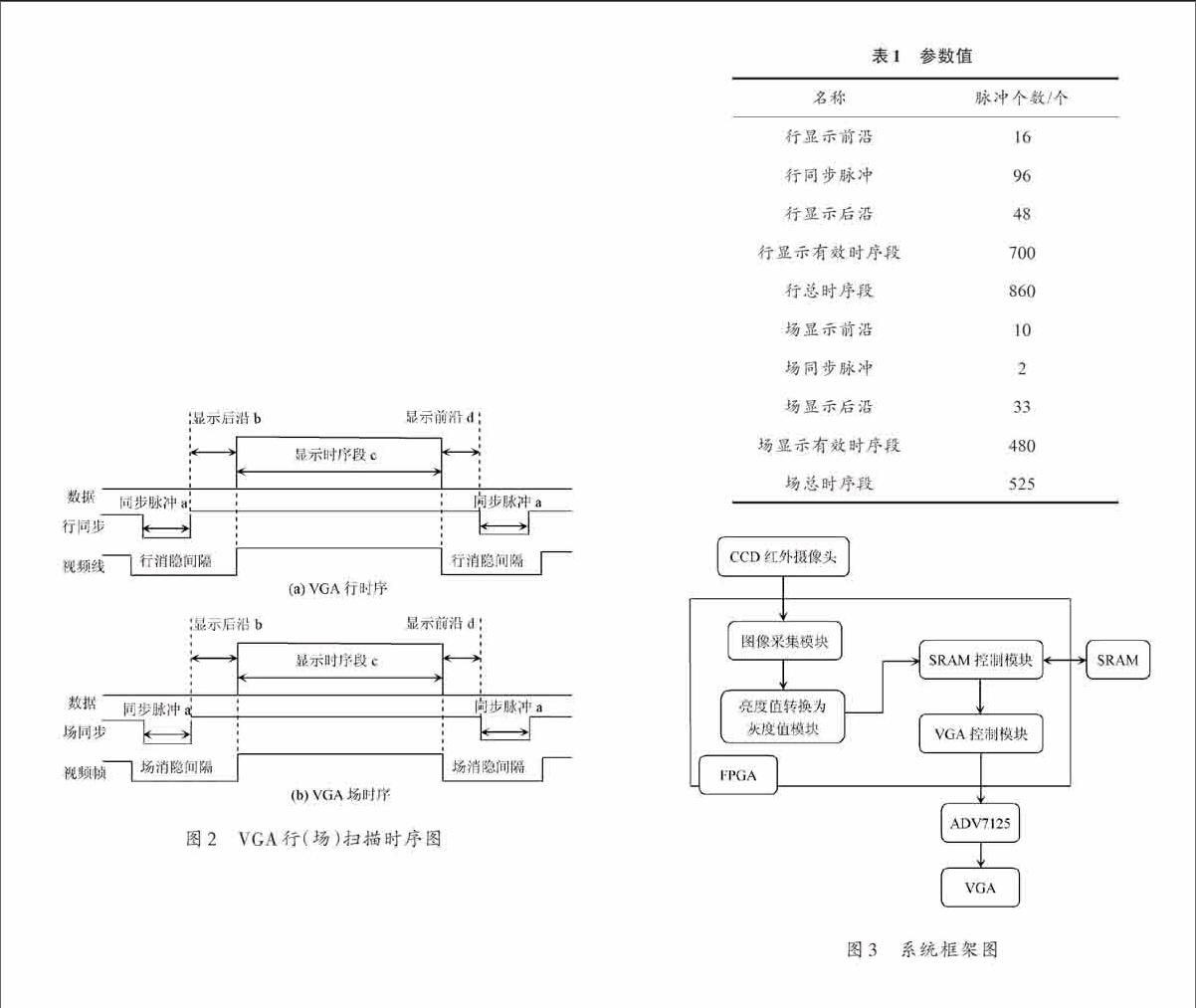

水平扫描时间是指完成一行扫描所需要的时间,其倒数代表行频率;垂直扫描时间是指完成整个屏幕扫描需要的时间,倒数为场频率,即一屏刷新一次的频率。常见的有60 Hz,75 Hz等。在本文中,时钟频率以700×480@59.94 Hz(60 Hz)为例,每场对应着525个行周期(信号是N制式,525=10+2+480+33),其中480是图像显示行。每一场都有场同步信号,脉冲的宽度是2个行周期的脉冲,每显示行有860点时钟,其中700点是有效显示区,每一行有行同步信号,该脉冲宽度为96个脉冲。由此可以算出:行频为525×59.94=31 469 Hz;需要的时钟频率为:525×860×59.94≈27 MHz。VGA的行时序、场时序分别包括4个参数:显示前沿、同步脉冲、显示后沿和显示有效时序段,参数值见表1。

2 VGA驱动程序的FPGA实现

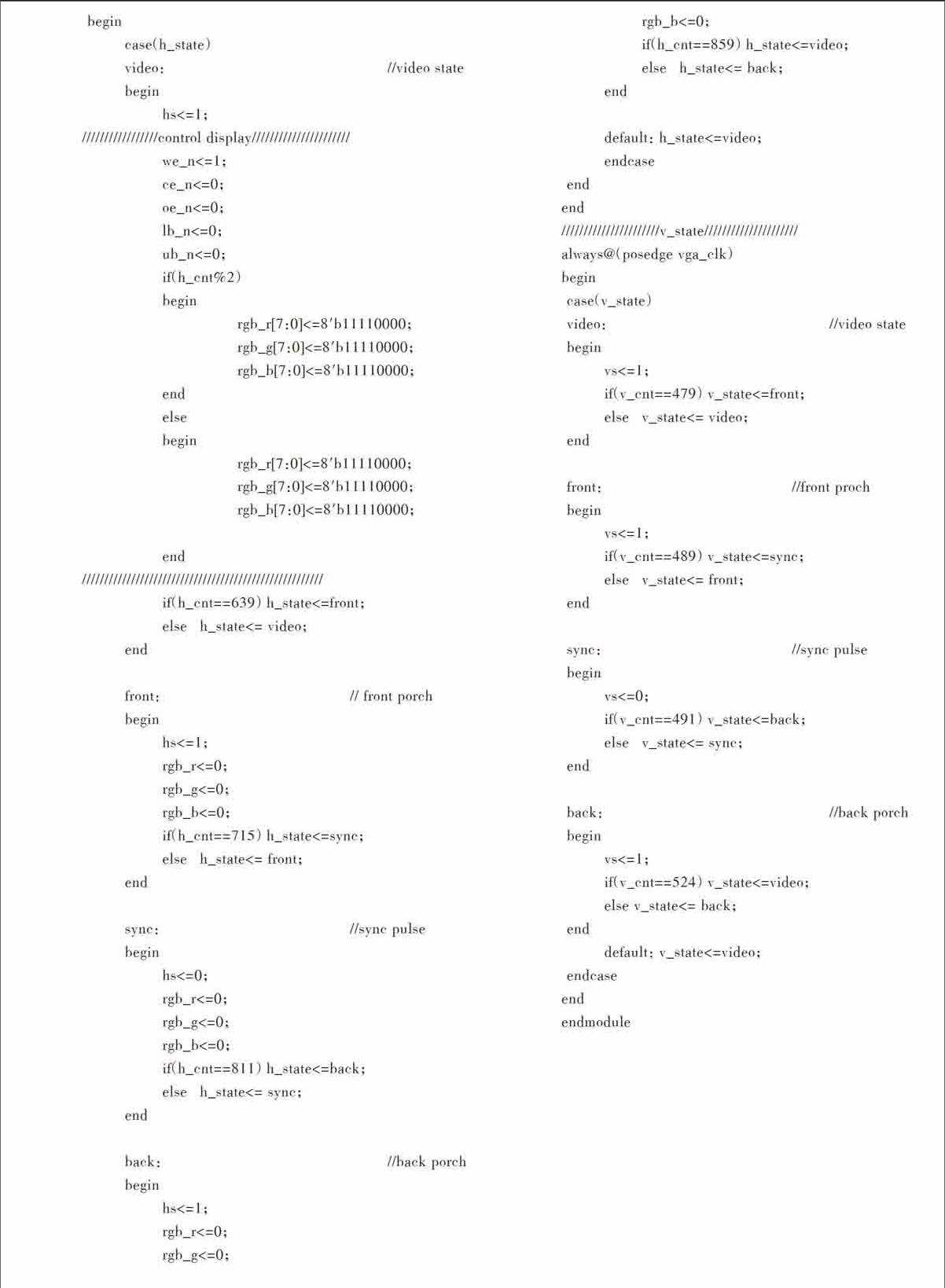

FPGA(Field?Programmable Gate Array)现场可编程门阵列,是整个系统的核心。FPGA拥有广泛的硬件资源,功能强大,可重配置能力强,保密性好,系统硬件规模小、投资少等特点,是嵌入式设计的主流平台之一[18?19],利用FPGA编程器件实现VGA显示,实际应用广泛。系统组成框架图如图3所示。

表1 参数值

图3 系统框架图

(1) 系统通过CCD红外摄像头采集红外图像LVDS数据传输给FPGA芯片,FPGA内部实现的功能包括:图像采集模块、亮度值转换为灰度值模块、SRAM控制模块、VGA控制模块。

(2) 图像采集模块获取红外图像LVDS数据,根据红外图像的时钟信号及同步信号划分出一块存储地址及一帧图像的大小。

(3) 亮度值转换为灰度值模块是对红外图像亮度值映射到灰度值的转换,也就说获得红外图像亮度范围为0~65 535映射到灰度范围0~255上。

(4) SRAM控制模块是对外围SRAM芯片的读/写操作,也就是说通过SRAM控制模块可以把转换好的红外图像数据存储到SRAM芯片,新数据来到更新SRAM芯片中数据,读信号来到读取SRAM芯片中数据,是一种乒乓读写操作的实现。

(5) VGA控制模块实现了使用27 MHz时钟输出700×480@60 Hz VGA信号,同时控制ADV7125芯片输出到VGA显示屏幕上。

VGA驱动程序需要完成的任务是:行同步信号和列同步信号根据VGA时序产生,在有效像素期间内将显示颜色的数据传输到RGB;显示模式和刷新频率不同时,同步信号的前、后、同步信号、有效像素数也不同,需要通过像素时钟率来进行设置;例如表1中数据,以700×480,60 Hz为例,像素时钟为27 MHz,像素时钟=(16+96+48+700)×(10+2+33+480)×60=27 MHz。

以下是本设计中VGA实现显示的Verilog代码:

/*

vga(700*480, 60hz)

dclk=27M hs:Horizontal vs:Vertical

every Vertical has 525 Horizontals

every Horizontal has 860 point

IDEA BY XIAYANG

*/

module vga_drive(

//vga port////////////////////////////////////////////

hs, //vga hs

vs, //vga vs

reset, //reset

clk, //vga clk input 27M

rgb_r, //vga red output[9:0]

rgb_b, //

rgb_g, //

blank, //blank=hs&&vs

vga_sync, //tvsync=0

vga_clk, //clk to ad7125 27M

//sram port////////////////////////////////////////////

sram_addr, //sram address output[17:0]

sram_data, //sram data input[15:0]

ce_n,

we_n,

lb_n,

ub_n,

oe_n

);

////////////////////////////////////////////////////////

input clk,reset;

input[15:0] sram_data;

output[17:0] sram_addr;

output hs,vs,blank,vga_sync,vga_clk,ce_n,we_n,lb_n,ub_n,oe_n;

reg vga_clk;

//output[9:0] rgb_r,rgb_g,rgb_b;

output[7:0] rgb_r,rgb_g,rgb_b;

reg hs,vs,ce_n,we_n,lb_n,ub_n,oe_n;

//reg[9:0] rgb_r,rgb_b,rgb_g;

reg[7:0] rgb_r,rgb_b,rgb_g;

reg[17:0] sram_addr;

reg[9:0] h_cnt,v_cnt;

reg[1:0] h_state;

reg[1:0] v_state;

reg flage; //control sram upper data or lower data

reg [1:0] clk_count=0;

//reg lcd_dclk;

parameter video=0,front=1,sync=2,back=3;

assign blank=hs&&vs; //blank

assign vga_sync=0; //tvsync

//assign vga_clk=lcd_dclk; //vga clk 27M

//////////////////////hs&vs(clk)///////////////////////////

always @ (posedge clk)

begin

clk_count<=clk_count+2′d1;

if(clk_count[0])

vga_clk<=1′b0;

else

vga_clk<=1′b1;

end

always@(posedge vga_clk or negedge reset)

begin

if(~reset)

begin

h_cnt<=0;

v_cnt<=0;

end

else if(h_cnt==859)

begin

h_cnt<=0;

if(v_cnt==524)

begin

v_cnt<=0;

end

else v_cnt<=v_cnt+1;

end

else h_cnt<=h_cnt+1;

end

///////////////////////h_state////////////////////////

always @ (posedge vga_clk or negedge reset)

begin

if(~reset)

begin

sram_addr<=0;

flage<=0;

end

else

begin

case(h_state)

video: //video state

begin

hs<=1;

/////////////////control display//////////////////////

we_n<=1;

ce_n<=0;

oe_n<=0;

lb_n<=0;

ub_n<=0;

if(h_cnt%2)

begin

rgb_r[7:0]<=8′b11110000;

rgb_g[7:0]<=8′b11110000;

rgb_b[7:0]<=8′b11110000;

end

else

begin

rgb_r[7:0]<=8′b11110000;

rgb_g[7:0]<=8′b11110000;

rgb_b[7:0]<=8′b11110000;

end

//////////////////////////////////////////////////////

if(h_cnt==639) h_state<=front;

else h_state<= video;

end

front: // front porch

begin

hs<=1;

rgb_r<=0;

rgb_g<=0;

rgb_b<=0;

if(h_cnt==715) h_state<=sync;

else h_state<= front;

end

sync: //sync pulse

begin

hs<=0;

rgb_r<=0;

rgb_g<=0;

rgb_b<=0;

if(h_cnt==811) h_state<=back;

else h_state<= sync;

end

back: //back porch

begin

hs<=1;

rgb_r<=0;

rgb_g<=0;

rgb_b<=0;

if(h_cnt==859) h_state<=video;

else h_state<= back;

end

default: h_state<=video;

endcase

end

end

//////////////////////v_state/////////////////////

always@(posedge vga_clk)

begin

case(v_state)

video: //video state

begin

vs<=1;

if(v_cnt==479) v_state<=front;

else v_state<= video;

end

front: //front proch

begin

vs<=1;endprint

if(v_cnt==489) v_state<=sync;

else v_state<= front;

end

sync: //sync pulse

begin

vs<=0;

if(v_cnt==491) v_state<=back;

else v_state<= sync;

end

back: //back porch

begin

vs<=1;

if(v_cnt==524) v_state<=video;

else v_state<= back;

end

default: v_state<=video;

endcase

end

endmodule

VGA时序控制模块控制产生700×480的显示范围,另外,消隐范围、水平同步时序信号HS以及垂直同步时序信号VS的值也受VGA时序控制模块控制[20]。通常情况下,时序计数器是通过像素时钟来控制水平同步时序信号HS,译码计数器的值产生HS信号。当前像素显示的位置由计数器在指定的某一行处产生。一个独立的计数器产生垂直时序信号VS,垂直同步计数器在每个HS脉冲信号来临时自动加1,译码值产生VS信号,计数器产生当前显示行。这2个计数器从地址到显示缓冲器连续计数。

3 灰度图像的实现

这里把能真实地反映自然物本来颜色的图像称之为真彩色图像,真彩色图像占用的存储空间大、耗时多[21]。只含有亮度信息,而无色彩信息的图像称为灰度图,例如平时生活中见到的黑白照片:照片的亮度有明暗的变化,但是没有彩色。在显示器上要想显示灰度图,需要把亮度的值进行量化。亮度值通常包括从0~255的范围,一共256个级别,其中0是代表最暗即全黑,255代表最亮即全白。在.bmp格式的文件中是没有灰度图这一概念的,但是可以通过在.bmp文件中表示出灰度图。通过利用每一项的 RGB 值都是相同的256色的调色板来实现,也就是说 RGB 值从(0,0,0),(1,1,1)一直到(255,255,255)这样的方式。其中(0,0,0)是全黑色,(255,255,255)是全白色,中间的代表灰色。这样,灰度图就可以用256色图来表示,同理灰度级别也可以用256级别来表示。本文中VGA显示系统中灰度图的研究和添加,使得显示器不仅能显示彩色,同时可以有不同灰度等级的图像输出。

4 结 语

本文在基于FPGA的VGA图像显示系统的研究中,通过基于FPGA进行的设计以及VGA显示接口的使用,使系统的成本大大降低,数据传输速度增强。在应用上可以根据时钟频率大小设置分辨频率大小,相比专用IP模块减少了不必要的电路配置,增加了模块的灵活性。另外,添加了显示彩色图像可以转化为灰度图的设计,完善了输出图像多为彩色图的不足,使输出图像的色彩变化更具选择性。

参考文献

[1] 董兵,朱齐丹,文睿.基于FPGA的VGA图像控制器的设计与实现[J].应用科技,2006,33(10):42?45.

[2] 朱奕丹,方怡冰.基于FPGA的图像采集与VGA显示系统[J].计算机应用,2011,31(5):1258?1264.

[3] 刘威,石彦杰,高博.基于FPGA的VGA显示模式和像素频率的识别[J].电子工程师,2008,34(1):50?52.

[4] 蒋艳红.基于FPGA的VGA图像信号发生器设计[J].电子测量技术,2008,31(3):78?81.

[5] 杨钦,周云飞,胡永兵.基于FPGA的视频图像采集与显示系统设计[J].计算机工程与设计,2013,34(6):1988?1992.

[6] 邵忠俊,程光伟.基于FPGA的视频采集与显示模块设计[J].电子元器件应用,2010,12(12):24?25.

[7] 刘文英.基于FPGA的视频图像预处理系统的设计与实现[D].天津:天津师范大学,2010.

[8] 祝长锋,肖铁军.基于FPGA的视频图像采集系统的设计[J].计算机工程与设计,2008,29(17):4404?4407.

[9] 张亚平,贺占庄.基于FPGA的VGA显示模块设计[J].计算机技术与发展,2007,17(6):242?245.

[10] 郑争兵.基于FPGA的VGA波形显示系统设计与实现[J].液晶与显示,2014,29(1):88?93.

[11] 周卓然,徐道连,吕凤飞,等.基于FPGA的VGA图像显示系统的设计与实现[J].仪表技术与传感器,2012(7):90?92.

[12] 袁堂青,张玉璘.基于FPGA的VGA汉字显示系统设计与实现[J].济南大学学报:自然科学版,2011,25(1):37?38.

[13] 熊文彬,蒋泉,曲建军,等.基于FPGA实现的视频显示系统[J].液晶与显示,2011,26(1):92?93.

[14] 陈姚节,卢建华.基于FPGA的VGA显示接口的研究与设计[J].交通与计算机,2005,23(2):47?49.

[15] Video Electronics Standards Association. VESA and industry standards and guidelines for computer display monitor timing (DMT) [S]. San Jose, USA: VESA, 1998.

[16] 朱文伟,许忠仁.基于FPGA的VGA图像控制器的设计与实现[J].贵州大学学报:自然科学版,2009,26(2):109?111.

[17] 刘乐善.微型计算机接口技术及应用[M].武汉:华中科技大学出版社,1999.

[18] 郑争兵.一种基于FPGA的UART电路设计[J].国外电子测量技术,2010,29(7):85?87.

[19] 郑争兵.基于DSP Builder的FIR数字滤波器设计与验证[J].陕西理工学院学报:自然科学版,2013,29(2):34?38.

[20] 郭永彩,苏渝维,高潮.基于FPGA的红外图像实时采集系统设计与实现[J].仪器仪表学报,2011,32(3):514?519.

[21] 周雪芹,刘晓红.利用VC实现真彩色位图到灰度图的转换[J].模式识别与仿真技术,2005,24(3):25?27.endprint