基于FPGA的图像发生器的设计

2015-10-26李华

李 华

(商洛学院电子信息与电气工程学院,陕西商洛726000)

基于FPGA的图像发生器的设计

李 华

(商洛学院电子信息与电气工程学院,陕西商洛726000)

为了验证图像采集系统的正确性,设计了一套基于FPGA的图像发生装置。系统将规律变化的图像集成到FPGA片内,结合连续变化的行头和帧头信息,按照一般图像探测器输出的格式进行输出,从而达到检验采集系统的目的。系统以一片Xilinx公司FPGA作为硬件运行平台,使用Verilog-HDL硬件描述语言并采用自上而下的模块化设计对整个系统进行硬件描述。试验结果表明,所设计的图像发生器产生的图像边缘锐利、规律性强,系统复杂度低、易于硬件实现,具有较好工程应用价值。

FPGA;Verilog-HDL语言;图像探测器;仿真

随着多媒体技术和网络技术发展的速度不断提高,各领域中数字图像处理被广泛地应用,相应的对于图像处理的要求也随之不断提高。一方面,图像处理依靠软件实现的实时性、高效性效果欠佳;另一方面,高速发展的微电子技术,促使基于各种硬件平台的数字图像处理的优势愈加明显[1]。特别是近些年,随着可编程逻辑器件技术的进步,基于FPGA的图像处理得到了长足的发展[2-3]。本文正是在这种大背景下,对基于FPGA硬件实现的图像发生器设计进行了深入研究,为将来开展以FPGA为核心图像处理系统的新型数字图像处理算法的开发、应用及硬件实现奠定了稳固的基础。

1 系统方案设计

本文图像发生系统的原理框图如图1所示。系统以一片FPGA为核心,+5V供电,仅配置外围辅助电路就可以根据用户需要完成不同分辨率和帧频的图像输出功能。其中,FPGA使用了Xilinx公司的Virtex-4,型号为XC4VSX55。程序存储器选用一片Xilinx公司的大容量FLASHXCF32P。FPGA正常工作需要三种电源,分别是+2.5 V、+3.3 V和核电压+1.2 V,其中,+2.5 V和+3.3 V由+5 V经LDO变换而来,而+1.2 V与+5 V压差较大,因此,为了考虑变换效率,此处选用DC/DC进行变换。晶振选用64 MHz,以适应较宽的频率应用范围。

图1 图像发生器原理框图

系统的工作过程为:当FPGA上电稳定后,根据默认的分辨率和帧频进行工作,通过LVDS向外界输出并行图像数据。由于本设计使用的是并行输出模式,输出图像由帧有效、行有效、像素时钟和数据组成。当用户需要改变输出图像的分辨率或帧频等参数时,通过RS422进行设置,同时,在设置成功后,FPGA会通过RS422接口返回工作状态,以告诉用户是否设置成功。

2 设计过程

本设计选择的Virtex-4系列FPGA采用90 nm工艺设计的高性能平台级逻辑器件,该产品是基于新的高级硅片(ASMBL)架构,有550万个逻辑门,位列全球逻辑密度最高的器件之一,适合于对逻辑门需求较高的设计应用。

Xilinx公司推出的ISE软件开发平台是针对Xilinx的FPGA和CPLD器件开发的软件工具,涵盖了软件开发、基于HDL硬件语言设计、验证、调试等设计流程。ISE的开发流程包含设计输入、综合、仿真、实现和下载,包括了FPGA开发的全过程[4]。

本设计主要是结合Xilinx公司的XC4VSX55和ISE进行开发。

2.1 图像发生器设计

2.1.1 图像探测器输出格式

一般的图像探测器,不管是并行输出或者是LVDS输出,其最终的格式都将由四部分组成:帧有效、行有效、像素时钟和图像数据[5],如图2所示。其中,帧有效、行有效用于标识有效数据,高电平有效。像素时钟用于图像数据的同步,便于后续图像采集系统对图像数据的采集,一般在时钟的上升沿输出图像数据。图像数据有8 bit、10 bit或12 bit等位宽,取决于探测器使用的AD。直到这些关系是设计图像发生装置的前提。

图2 探测器图像输出格式

2.1.2 设计原理与过程

1)设计原理

本设计的思路即利用FPGA模拟图2所示的图像格式,这样,图像采集装置即使在图像探测器没有到位的情况下照样可以验证其正确性。为了便于找问题,本设计使用了诸多技巧:首先,图像数据的设计,使用了由大到小递减的格式,而且每次变化都是减1,这样,反映到灰度图像上就是亮度由亮逐渐变暗,直到全黑为止,不管是主观感觉还是客观查找,都很容易发现问题;其次,图像每一行的第一个像元代表帧号,即第几帧,这个信息会显示图像采集是否连续,有没有丢帧现象,因为图像的存储往往都是若干帧一起存储,因此,连续存储的图像,如果其帧号不连续,就说明有丢帧现象;最后,仿照帧有效的原理,在图像数据每一行的第二个像元放置行号,用来判断图像有没有丢行,一帧图像是由若干行组成,从上往下行号是逐行递加的关系,因此,很容易找到丢行问题。

本设计就是按照以上思路,结合帧有效和行有效,组成图像数据送给图像采集装置[6],用于验证其正确性。

2)主要信号的设计与取值

按照某采集系统的要求,本设计用于产生2352×1728分辨率的图像,具体设计方面的参数取值如下:

像素时钟信号:像素时钟用64 MHz的系统时钟。

帧同步信号(fsync):fsync信号由两部分组成,帧有效和帧逆程。帧有效的长度总共需要包含2 352个行时间、第一个行有效前的时间(取200像素时钟)和最后一个行有效后的时间(取200像素时钟),有效时为高电平。帧逆程时为低电平,长度取为两行的长度,即2352×2= 4704像素时钟。帧有效信号的跳变在时钟的下降沿发生。

行有效信号(lsync):行有效的长度也由两部分组成,行有效和行逆程。行有效的长度为2352像素时钟,行逆程的长度为600像素时钟。行有效信号的跳变也在时钟的下降沿发生。

数据信号:图像数据采用12 bit的形式,总共有2352×1728像素。一帧中每一行的第一个像元为帧计数,从0开始计数,直到4 095又重新赋0。第二个像元为行计数,也由0一直递增到1 727。其它像元每一行都一样,从2 350一直递减至0。

当然,以上参数是在全帧模式下设定的,如果用户要求改变帧频和分辨率时,只需要将相应的参数仿照全帧模式进行修改即可,此处不再赘述。

3)FPGA设计过程

基于以上思路的FPGA设计过程如下:首先,产生行有效信号,方法是采用计数器的方式,即行有效和行逆程总共2352+200=2552,计数器为1时,行有效变为高电平直到2 352,在2 353时变为低电平,直到2 552,这样,一行就产生了,当有1 728行时,停止产生行有效,此时,一个1 728行,每行2 352个像元且行逆程为200的灰度图像就产生了。下来就是给行逆程内填充数据,当计数器为1时,给图像数据赋帧号,等于2时赋行号,3以后直到2 353赋从2 350逐一递减的计数值[7]。

整个过程以一个三段式状态机控制[8],它可将一个个状态分变量集合,能记住当前的状态和所有的输入信息,目的是将输入信息划分为状态和数据两部分,利用状态机中的译码器进行检测,从而将输入信息完整输出。整个过程从空闲状态→第一行前→行功能→最后一行后→空闲状态,如此反复,达到连续不断产生图像的目的。

图3是本设计的Modelsim仿真波形。其中,时钟信号为clk_in、帧信号是fsync、行信号是lsync、图像数据为data。其中,图3(b)是图3(a)第一行的放大。可以看出,设计完全满足图像输出格式要求,证明了设计的可行性与正确性。

图3 图像发生器时序仿真波形

2.2 串口通讯协议设计

根据需要,本系统用RS422串行接口(简称串口)与外界进行通讯,接收控制命令以及发送图像发生器的工作参数,速率为9 600 bps。硬件接口电路如图4所示。

图4 RS422接口电路

2.2.1 串口设计原理

串口是一种串行通信接口标准,使用它连接的串行设备之间的距离可达25 m,传输速度可达38.4 Kbps。虽然串口作为一种连接标准正逐渐被高速网络取代,但是,它对于嵌入式系统来说仍然是一种非常有用而且简单的连接工具[9]。

目前,大部分处理器芯片都集成了UART,但是一般FPGA芯片却没有这个特点,所以使用FPGA作为处理器来实现串口功能可以有两个选择,第一个是使用UART芯片进行串并转换,第二个选择是在FPGA内部实现UART功能。本设计选择了第二种,通过FPGA将串口协议及其附加的缓冲模块整合到FPGA内部,这样很大程度上节省了电路的物理面积和成本,增强了系统的可扩展性。FPGA的串口模块工作时,当任意一路接收数据时,FPGA内部与其对应的接收模块按照协议将接收到的串行数据转换为并行数据,在FPGA内部进行处理,从而完成与串口的通讯过程。

2.2.2 串口通讯设计

串口的接收模块与发送模块工作原理基本一致,都可以在FPGA内部由状态机来实现,通过分析发送数据起始位、数据位、奇偶校验位和停止位的发送顺序,依次完成Start,Shift,Parity,Stop四个状态,完成串口通讯。发送和接收过程如图5所示。

图5 串口FPGA实现过程

将串口协议嵌入到FPGA后,就可以应用其与外界进行通讯了,本设计应用串口分别控制图像的分辨率、帧频和级数等。当然,这里事先有约定协议在里面,例如分辨率的控制,没有必要逐行逐列的进行设置,这样不但麻烦,而且没有必要,因为分辨率要几个典型的就足够了。因此,分辨率从最大的2352×1728开始,成倍递减,而且采用的是寄存器的方式,例如:0x11表示2352×1728、0x22表示1176×864、0x33表示2352×864、……。这样,只要向串口发送寄存器的值,相应的分辨率就会由FPGA设置到图像里面。本设计定义了每次通讯由三级命令组成,其格式如图6所示。

图6 FPGA串口与外部通讯协议

其中,命令级参数:0xaa表示串口接收,0x55表示串口发送;寄存器级参数:0x11表示图像分辨率,0x22表示帧频,0x33表示级数等;数值级参数:表示相应的写入值。例如命令:0xaa+0x11+ 0x11就表示串口在接收外部指令,对分辨率进行修改,修改的值为2352×1728。

按照以上约定,利用串口向图像发生器发送了分辨率、帧频等参数,并从系统读取了一个参数,得到的仿真波形如图7所示。

图7 串口仿真波形

其中,exptime代表图像发生器的帧频,step代表图像发生器的分辨率,gain代表图像发生器的级数。可以看出,系统相应的工作状态都随着外部指令的改变而改变,通讯接口的设计完全满足项目的需要。

3 结果与分析

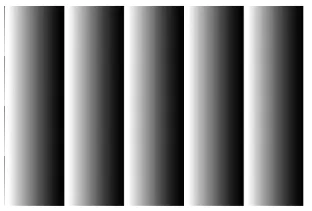

系统设计完毕,烧写至FPGA,通过数据线连接到图像采集卡,采集得到的图像如图8所示,可以看出,图像规律比较器,从左边由最亮逐渐递减至最暗,因为本文实验的图像采集卡采集的是8位图像,因此,最亮的值是255,最暗的值是0,这样,查找问题就很容易。特别是每行图像的第一个像元代表帧号,一帧内都是一致的,第二个像元代表行号,一帧图像中从上到下递增,而且是连续的,这样,图像是否丢帧、丢行一目了然。总之,这些特点对保证图像采集系统的正确工作奠定了坚实的基础。

图8 本系统输出图像

4 结语

本文设计了一套以Xilinx公司FPGA为核心器件的图像发生装置,系统可以根据应用需要产生不同帧频和分辨率的规律变化灰度图像,并结合连续变化的帧头和行头信息,从而更容易的找到图像采集系统的问题。整个成像系统不管是在功能,还是图像质量方面都具有较好的表现。目前,该图像发生系统已经用于数套图像采集系统的检测,其优良性能得到了用户的好评。

[1]李娟,刘艳滢.基于FPGA的图像采集模块的设计[J].仪表技术与传感器,2012(10):27-30.

[2]李华.基于FPGA+COMS的小型彩色数字相机系统设计[J].商洛学院学报,2014,28(4):27-31.

[3]李华.基于FPGA的成像系统自动曝光算法设计[J].商洛学院学报,2014,28(2):17-20.

[4]田耘,徐文波,胡彬,等.Xilinx ISE Design Suite 10.x FPGA开发指南—逻辑设计[M].北京:人民邮电出版社,2008:3-10.

[5]刘贤得.CCD及其应用原理[M].武汉:华中理工大学出版社,2008:10-35.

[6]吴灿.基于DSP的图像采集实验装置的研制[D].哈尔滨:哈尔滨工业大学,2007:31-39.

[7]余辉龙.CMOS一体化相机关键技术研究[D].长春:中国科学院长春光学精密机械与物理研究所,2010:93-96.

[8]高书莉,罗朝霞.可编程逻辑设计技术及应用[M].北京:人民邮电出版社,2006:44-56.

[9]刘艳滢,李桂菊,冯晓勇.高速数字式摄像机的控制与数据流远距离传输的研究[J].长春理工大学学报,2004,27(2):22-25.

(责任编辑:李堆淑)

Design of Image Generator Based on FPGA

LI Hua

(College of Electronic Information and Electrical Engineering,Shangluo University,Shangluo 726000,Shaanxi)

In order to verify the correctness of the image acquisition system,a set of image generator based on FPGA is designed.Regular image combined with continuous change of line-head and frame-head information is integrated into the FPGA chip.Image output is done with the general imagedetectoroutputformattoachievethepurposeofsysteminspection.OneXilinxField Programmable Gate Array(FPGA)is chosen as the hardware design platform,and the algorithm is described with Verilog-HDL to perform the modularization design from top to bottom.Experimental results show that image obtained from the system is sharp with strong regularity,low complexity and easy hardware implementation,and has a good engineering application value.

FPGA;Verilog-HDL language;image sensor;simulation

TP391.4

A

1674-0033(2015)04-0015-05

10.13440/j.slxy.1674-0033.2015.04.005

2015-05-11

收稿日期:陕西省教育厅专项科研计划项目(2013JK1057)

李华,女,陕西临潼人,硕士,副教授