用于射频集成的高Q硅基电感的优化设计

2015-09-16王惠娟等

王惠娟等

摘 要: 采用理论分析与电磁仿真结合的方法,对硅上多层金属构成的螺旋电感进行电性能研究,优化并获得一种适用于射频电路集成的硅基射频高Q电感。对于影响电感Q值的多种损耗机制,重点研究了趋肤效应对电感的影响。并通过结构参数及金属层叠优化后,硅上电感的Q值可以达到60以上,自谐振频率可以达到10 GHz以上,可以较好地应用于射频系统中的滤波选频及匹配等网络。

关键词: 硅上电感; 趋肤效应; 射频系统集成; 电磁仿真

中图分类号: TN702?34 文献标识码: A 文章编号: 1004?373X(2015)18?0106?04

Abstract: The electrical performance of silicon?based spiral indicator constituted with multi?layer metal is studied by the combined method of theoretical analysis and electromagnetic simulation. The silicon?based RF high?Q indicator applied to RF circuit integration was optimized and acquired. Among various loss mechanisms influencing Q?value of the indicator, the influence of skin effect on the indicator is researched emphatically. The silicon?based Q?value of the indicator after optimizing the structure parameter and the metal stacking can reach 60, and the self?resonant frequency can achieve 10 GHz. The inductor can be better applied to networks of filtering, frequency?selecting and matching in RF system.

Keywords: silicon?based inductor; skin effect; RF system integration; electromagnetic simulation

0 引 言

近几十年以来,片上电感的相关研究成为国内外研究的热点,取得了重要研究进展。目前片上电感的实现方式主要有三种:键合线电感、有源电感与螺旋电感。其中键合线电感寄生电容大,电感量的不精确,应用比较受限;而有源电感占用芯片面积小,应用受频率和电压影响大[1]。螺旋电感由于其对衬底的绝缘性要求较高,同时占用面积过大,主要使用薄膜、砷化镓、低温共烧陶瓷等技术制作并以单片的形式与电路的有源部分连接。随着硅理论和工艺的发展,由于其低成本且成熟的工艺,人们开始关注使用硅上工艺实现无源器件。与GaAs半绝缘衬底不同,硅衬底是半导体,衬底的损耗比较大,很难获得高的品质因素,如何实现高性能的电感成为一个重要的研究方向。已经知道采用片上技术在硅上实现螺旋电感,Q值一般在十几以内;而采用厚铜和高阻硅来实现高Q螺旋电感一般也在40以下[2?5]。本文正是在此背景之下,对硅上螺旋电感进行理论上对损耗机制分析,并结合电磁仿真软件对影响硅上电感的感值及Q值进行优化仿真,并得到Q值最高结构的硅上电感。同时基于优化仿真结构,和影响硅上电感的多种寄生,提出适用于宽频带的电感寄生参数。

1 硅基螺旋电容的设计参数与损耗机制

1.1 硅基螺旋电感的设计参数

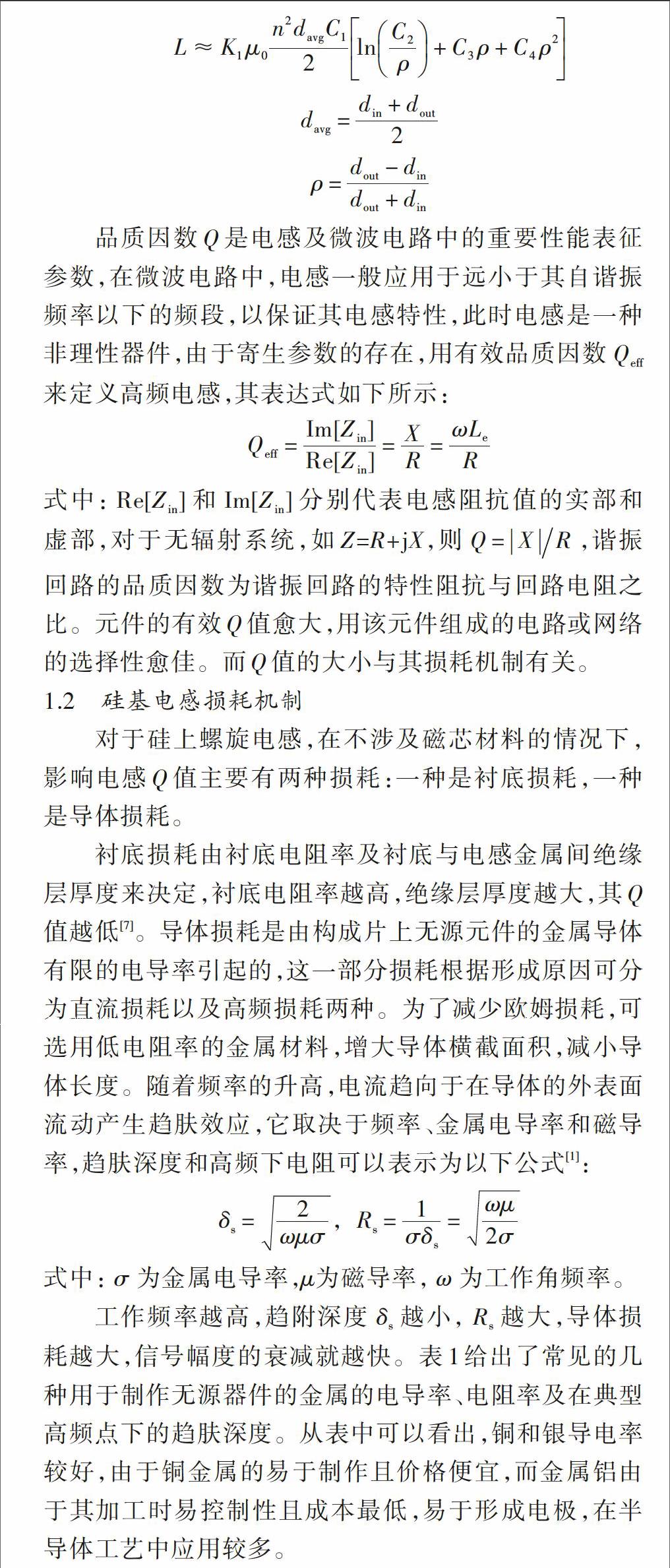

硅基螺旋电感量与其几何形状有着密切的关系,其精确的计算可通过求解麦克斯韦方程组得出。其几何参数的确定可以应用 S.S Mohan提出的计算电感的闭合公式[6]:针对四边形、六边形、八边形及圆形平面螺旋电感,其中C1,C2,C3,C4是由电感线圈形状所确定的常数,[μ0]代表磁导率,n代表线圈匝数,[davg]代表了电感线圈内径与外经的平均值,[ρ]代表了线圈填充率,其相关定义式为如下所示:

[L≈K1μ0n2davgC12lnC2ρ+C3ρ+C4ρ2]

[davg=din+dout2]

[ρ=dout-dindout+din]

品质因数Q是电感及微波电路中的重要性能表征参数,在微波电路中,电感一般应用于远小于其自谐振频率以下的频段,以保证其电感特性,此时电感是一种非理性器件,由于寄生参数的存在,用有效品质因数[Qeff]来定义高频电感,其表达式如下所示:

[Qeff=Im[Zin]Re[Zin]=XR=ωLeR]

式中:[Re[Zin]]和[Im[Zin]]分别代表电感阻抗值的实部和虚部,对于无辐射系统,如Z=R+jX,则[Q=XR],谐振回路的品质因数为谐振回路的特性阻抗与回路电阻之比。元件的有效Q值愈大,用该元件组成的电路或网络的选择性愈佳。而Q值的大小与其损耗机制有关。

1.2 硅基电感损耗机制

对于硅上螺旋电感,在不涉及磁芯材料的情况下,影响电感Q值主要有两种损耗:一种是衬底损耗,一种是导体损耗。

衬底损耗由衬底电阻率及衬底与电感金属间绝缘层厚度来决定,衬底电阻率越高,绝缘层厚度越大,其Q值越低[7]。导体损耗是由构成片上无源元件的金属导体有限的电导率引起的,这一部分损耗根据形成原因可分为直流损耗以及高频损耗两种。为了减少欧姆损耗,可选用低电阻率的金属材料,增大导体横截面积,减小导体长度。随着频率的升高,电流趋向于在导体的外表面流动产生趋肤效应,它取决于频率、金属电导率和磁导率,趋肤深度和高频下电阻可以表示为以下公式[1]:

[δs=2ωμσ,Rs=1σδs=ωμ2σ]

式中:[σ]为金属电导率,μ为磁导率,[ω]为工作角频率。

工作频率越高,趋附深度[δs]越小,[Rs]越大,导体损耗越大,信号幅度的衰减就越快。表1给出了常见的几种用于制作无源器件的金属的电导率、电阻率及在典型高频点下的趋肤深度。从表中可以看出,铜和银导电率较好,由于铜金属的易于制作且价格便宜,而金属铝由于其加工时易控制性且成本最低,易于形成电极,在半导体工艺中应用较多。

2 硅基电感的层叠及优化仿真

2.1 硅基螺旋电感的设计参数

通过对硅上平面螺旋电感进行了理论分析,给出了影响电感电学性能主因素。总结出在设计中要考虑的可变参数包括:

(1) 衬底的厚度及电阻率;

(2) 线圈的圈数;

(3) 金属的线厚、线宽、线间距,材料的选择;

(4) 线圈面积与电感参数的影响;

(5) 多圈的过孔及连出方式[3]。

表1 几种常见金属的导电性能及趋肤深度对比

本文选取其中的几个关键点,介绍具体的分析、仿真及优化过程。为了研究硅上电感的电学特性,采用两种不同的软件(HFSS,ADS)完成以下电感的电磁仿真(EM)及建模仿真。

本文所采用的电感为平面螺旋八边形结构,金属层叠由四层金属及两种通孔构成。其4层金属可以组成如图1所示的两种结构,图中M1和M3的典型选择为金属铝,M2及VIA1_2的典型选择为金属铜。基于这两种层叠,选择以下参数来完成优化:硅上电感的典型硅衬底选择均为2 000 [Ω?cm],而衬底厚度采用尽可能薄加工时且易于拿持的尺寸350 μm,选择2 μm的氧化层来作为硅表面绝缘。由于金属厚度大于3倍趋肤深度时,电感性能的改善并不明显,所以图1中构成电感的主要层M1和M2均为3 μm,VIA1_2也为3 μm,金属表面电极层M3为1 μm。

2.2 硅基螺旋电感的设计参数

(1) 电感的线宽、间距及内径:电感的电感内径D=240 μm;4种电感的线条宽度W分别为30 μm,40 μm,50 μm,60 μm;间距S为15 μm;线圈匝数N为2。图2数据中4条曲线依次对应4种线宽依次增大的电感和Q值。可以看出线条宽度的增加,电感感值略有增大,电感Q值却有明显的增大,这是因为线宽增大减小了导体损耗。且所有电感自谐振频率在10 GHz内均未出现。

另外针对相同电感不同间距也相应完成仿真,发现以线宽60 μm电感为例,间距为15 μm时其电感Q值最大,说明此时绕线密度最有利用磁场的集中。而随着电感的内径增大其感值也相应呈正比增大,但是大电感谐振频率也随之减小。以线宽为60 μm的电感为例,内径从240 μm增大到500 μm,其感值从1.9 nH增大至3.2 nH(@2.5 GHz),谐振频率从11 GHz降低至6 GHz。

(2) 电感的绕圈匝数:对于电感的电感内径D=240 μm,电感的线条宽度W=60 μm,间距S=15 μm时,分别减少绕线圈数N,仿真得到电感值和Q值如图3所示。可以看出随着电感的圈数逐渐变小,电感感值呈线性减小,但是Q值略微增大,特别是小电感的Q最大值明显要增大很多。电感的Q值跟线圈圈数并没有直接的线性关系,跟线圈的绕线密度还有一定的关系,三者必须综合起来优化。

2.3 硅基螺旋电感的设计参数

前面的优化均采用如图1叠层2的思路,将多层金属都综合利用起来建模,下面将各种的金属及过孔互相组合形成电感,并对比其仿真结果。选择内径D为240 μm的八边形电感,线宽60 μm,间距为15 μm的两圈电感,建模得到的4种电感的金属构成分别为:M1+M2+M3+VIA1_2;M1+M2 +VIA1_2;M2+VIA1_2;M2,如图4所示,数据中4条曲线依次对应4种电感。结果显示电感的感值均接近,但是Q值有区别。预计的采用4层金属够成获得最高Q的电感并非如此,在2.5 GHz读取数据对比,采用单层M2上形成电感Q值最高可超过40,初步分析这是由于趋肤效应造成的。

为了进一步分析这种现象,采用单圈电感在不同层上走线建模。选择内径D为600 μm、线宽60 μm的八边形电感,对不同层金属的结构进行仿真得到的电感值及Q值如图5所示,图中4种电感的金属构成分别为M2,M3,M2+M3,M1+M2+M3+VIA1_2。同样选择频率约在2.5 GHz最近点读取数据,可知采用3 μm厚铜作为惟一金属层的电感Q值最大,并且其Q最大值可以超过60(7 GHz左右)。

图5中同时给出了两种电感的表面电流分布的结果,左图为L1的结果,可以看出其表面电流较大,右图为L4的结果(L2和L3结果类似),这是由于仅有L1电感是由3 μm的厚铜构成,其他电感表面均有一层1 μm的铝。而铜的导电率是比铝要高得多,使得铜线圈电阻小于铝圈。由于趋肤效应,电场往线圈的金属表面集中,所以L1的电流会大得多。

3 高频寄生参数的提取

对于硅上螺旋电感的等效模型研究,已经有较多的发表文章研究,但是大多等效模型都没有考虑到高频时的趋肤效应所带来的影响[6,9]。在本文中,根据仿真结果可以得到如图7中电路来拟合硅基电感的高频寄生参数。模型中将本征电感值一分为二,可以在较大频域内合理反应电感的性能。如图6所示,该模型考虑了多种寄生参数:电感的线圈电阻;趋肤效应;线圈叉指寄生电容以及衬底的介质损耗和衬底绝缘层带来的寄生电容,比较完备地反应了硅上电容在高频下的各项寄生参数。

将两种EM仿真软件的结果与原理图的阻抗参数拟合可以得到各组寄生参数的值,图7所示为最后仿真提取与电路提取电感值的结果对比,可以看出3种方法都可以较好地反应电感的感值随频率变化特性。

4 结 语

本文提供一种在硅上多层金属形成螺旋电感的优化和设计方法,并对影响电感感值及Q值的主要参数做理论分析,并对影响其电学性能的物理结构参数和层叠参数做优化仿真。对优化后的几个nH的电感,自谐振频率均达到10 GHz以上,在去除薄层的低电阻金属Al带来的趋肤效应和采用高电阻率衬底来避免衬底损耗后,其Q值最大可以达到60以上,验证了硅上电感可应用于射频集成系统的应用。同时本文提出了一种用于表征硅上螺旋电感的高频寄生参数的电路模型,可以与多种EM仿真结果一致,提供一种该螺旋电感用于射频无源系统设计的快速建模。

参考文献

[1] BAHL I. Lumped elements for RF and microwave circuits [M]. Boston: Artech House, 2003.

[2] LONG J R, COPELAND M A. The modeling, characterization, and design of monolithic inductors for silicon RFIC' s 90?2 [J]. IEEE Journal of Solid?State Circuits, 1997, 32(3): 357?369.

[3] LOPEZ?VILLEGAS J M, SAMITIER J, CANE C, et al. Improvement of the quality factor of RF integrated inductors by layout optimization [J]. IEEE Transactions on Microwave Theory and Techniques, 2000, 48(7): 76?83.

[4] NIKNEJAD A M, MEYER R G. Analysism, design, and optimization of spiral inductors and transformers for Si RF IC's [J]. IEEE Journal of Solid?State Circuits, 1998, 33(10): 1470?1481.

[5] RONG B, BURGHARTZ J, NANVER L, et al. Surface?passivated high?resistivity silicon substrates for RFICs [J]. IEEE Electron Device Letters, 2004, 6(25): 176?178.

[6] MOHAN S S, MARIA D M H, BOYD S P, et al. Simple accurate expressions for planar spiral inductances [J]. IEEE Journal of Solid?State Circuits, 1999, 36(34): 1419?1424.

[7] BURGHARTZ J N, REJAEI B. On the design of RF spiral inductors on silicon [J]. IEEE Transactions on Electron Devices, 2003, 50(3): 718?729.

[8] ROTELLA F, BHATTACHARYA B K, BLASCHKE V, et al. A broad?band lumped element analytic model incorporating skin effect and substrate loss for inductors and inductor like components for silicon technology performance assessment and RFIC design [J]. IEEE Transactions on Electron Devices, 2005, 11(52): 1429?1441.

[9] YU C P, RYU C, LAU J, et al. A physical model for planar spiral inductors on silicon [C]// Proceedings of 1996 Electron Devices Meeting. San Francisco: IEEE, 1996: 155?158.