基于FPGA的CMOS线阵图像传感器数据采集系统设计

2015-07-22樊红星张小超刘磊周鹏赵博

樊红星+张小超+刘磊+周鹏+赵博

摘 要: 针对日本滨松公司的CMOS线阵图像传感器G9214?512S,设计基于FPGA的同步工作模式的图像数据采集系统,使用VHDL语言对此系统进行描述,并用Xilinx ISE Design Suit自带的ISim软件对设计的时序进行仿真。采用Xilinx公司的Spartan 3 XC3S200A?4VQ100进行FPGA配置和验证,仿真结果表明该数据采集系统的时序正确,具有较高的实用价值。

关键词: FPGA; CMOS传感器; 数据采集系统; 模/数转换器

中图分类号: TN98?34 文献标识码: A 文章编号: 1004?373X(2015)14?0129?04

0 引 言

近红外(NIR)光谱仪是一种测量物质对近红外辐射的吸收率或透过率的分析仪器,由于其检测过程绿色,无损,快速等特点,已经广泛应用于农业、食品工业、石油化工、生物化工、制药业地质学等领域,近红外光谱仪也因此成为近年来分析仪器的热点研究领域之一[1]。作为近红外光谱仪核心器件的光电传感器的发展,对高性能光谱仪的研发起到了重要的推动作用。过去,光谱仪的光电传感器采用CCD传感器,但由于CCD型传感器耗电量大、工艺复杂、成本较高、驱动程序复杂,因此,基于CCD的近红外光谱仪的发展缓慢。随着半导体技术的进一步发展,CMOS传感器诞生,相对于CCD传感器来说,CMOS图像传感器具有成本低、功耗低,集成度高、体积小的优点,已经逐渐替代CCD应用于各种光电检测系统中,因此,开发基于CMOS传感器的光谱仪,发展前景广阔,具有较高的市场价值与实用价值[2]。

本文分析了G9214?512S图像传感器的工作模式 ,采用FPGA技术完成了其数据采集系统,使用VHDL语言对所设计系统进行描述,最后用Xilinx ISE Design Suit软件自带的ISim仿真软件对其进行仿真和验证,结果证明该数据采集系统的时序正确性。

1 系统简介

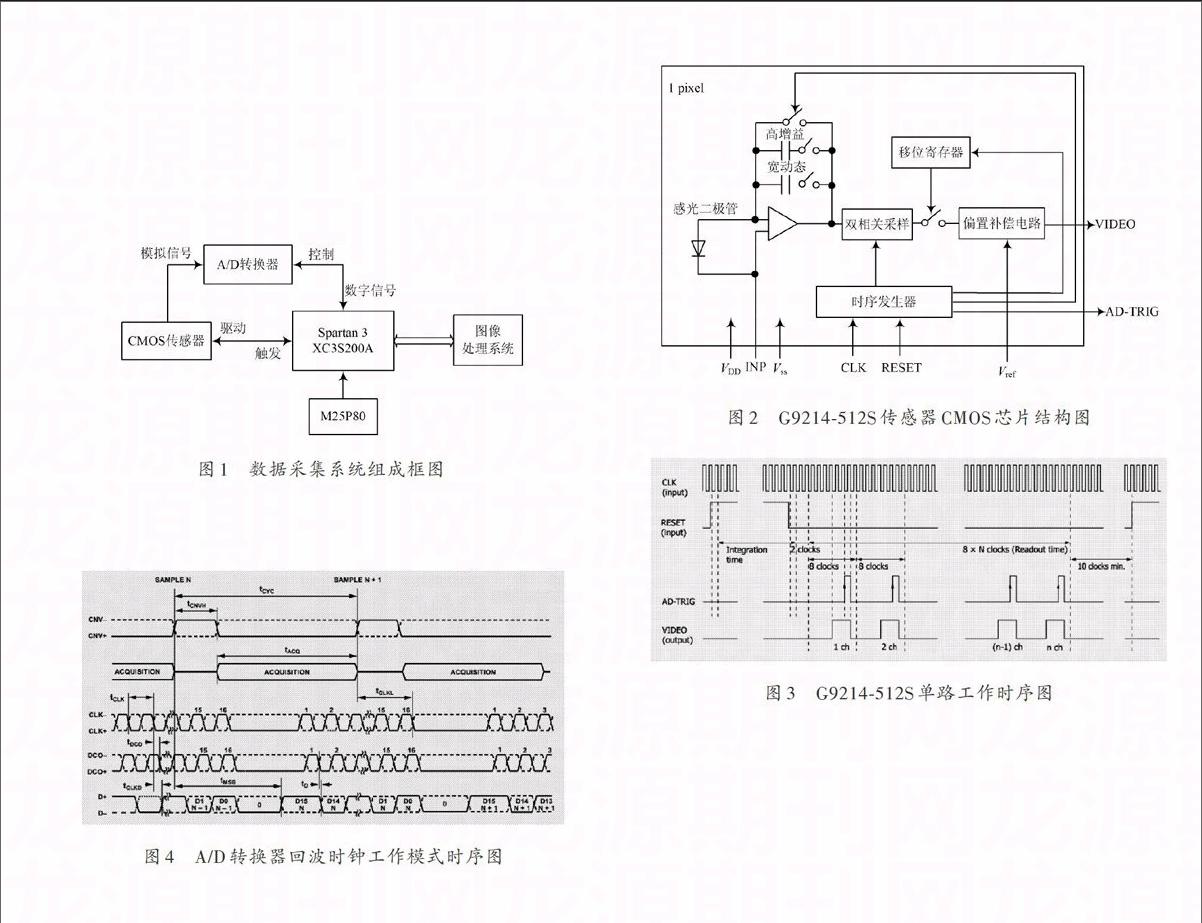

该数据采集系统由FPGA主控模块,CMOS图像传感器模块和A/D模数转换器模块组成,其系统框图如图1所示。FPGA主控模块提供系统所需要的时序和控制指令,外存储器M25P80存储FPGA配置信息,FPGA内部的FIFO缓存模块采用IP核产生,用来存储采集到的数据,以便后续图像处理系统进行数据处理,其数据缓存容量为10K×16 b,一次可以缓存20帧图像信息。CMOS图像传感器将光信号转换成模拟电压信号,输出给模/数(A/D)转换器进行模/数转换。A/D转换器模块将采集到的模拟数据转换成16 b串行数字信号,将其存入到FPGA内部移位寄存器,然后存入FIFO缓存器,完成一次数据采集[3]。

图1 数据采集系统组成框图

2 G9214?512S图像传感器

2.1 传感器参数

G9214?512S传感器是滨松公司专为近红外多通道光谱仪而设计的InGaAs线性CMOS图像传感器。具有动态范围高、像元小、分辨率高、暗电流小的特点,该传感器参数如下[4]:感光波长为0.9~1.7 μm;像元数目为512;像元尺寸为25 μm×25 μm;动态范围为16 666;工作时钟为0.1~4 MHz。G9214?512S传感器像元分为具有为奇、偶2路,每路256像元,外部信号对这两路像元的工作进行单独控制,使其工作于同步工作模式或者异步工作模式。同步工作方式驱动方案简单,因此本文所述数据采集系统采用同步工作方式。CMOS芯片的信号处理电路提供了2种工作方式:宽动态范围和高增益模式,在传感器CfSECLECT引脚加高电平实现高增益工作模式,加低电平即可实现宽动态范围工作模式。G9214?512S传感器CMOS芯片结构图如图2所示。G9214?512S片上CMOS电路集成了时序产生电路,因此其时序驱动简单,外部提供给传感器时钟信号和复位信号即可,双相关采样电路可以有效地减小复位噪声,移位寄存器电路可以保证信号准确有效的移出。

2.2 传感器工作时序图

传感器单路工作时序图如图3所示。可以看出,同步工作模式下,传感器需要2个外部输入时序信号:时钟信号CLK和复位信号RESET。本文所述数据采集系统采用同步积分模式:在一个复位周期中,RESET信号保持一段时间高电平,变为低电平,积分结束,等待2个时钟CLK,传感器将256个像元电荷信号以模拟电压形式VIDEO输出,VIDEO的信号周期是主时钟CLK频率的[18],输出VIDEO信号的同时,传感器输出一个触发外部操作信号TRIG,用于启动外部A/D转换器的操作,电荷输出结束,进入等待阶段[5]。

图2 G9214?512S传感器CMOS芯片结构图

图3 G9214?512S单路工作时序图

3 模/数转换器

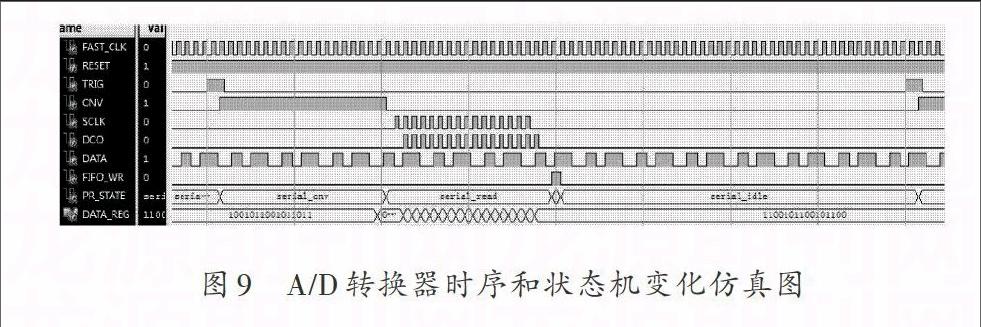

AD7961是Analog Device公司生产的16 b,5 MSPS,电荷再分配逐次逼近型(SAR)接口的模/数转换器,具有结构紧凑、功耗低、转换精度高和抗干扰性强的优点。AD7961具有差分输入接口、差分输出接口和差分控制接口,所有转换结果通过一个LVDS自时钟或回波时钟串行接口传送给FPGA[6]。本文采用回波时钟工作模式,其工作模式时序图如图4所示。

图4 A/D转换器回波时钟工作模式时序图

如图4所示,在CNV信号上升沿,ADC初始化,传感器开始进行采样,CNV信号高电平保持一段时间后,变为低电平后,开始有数据输出。FPGA在CNV信号上升沿一段时间后,给A/D转换器一个获取数据时钟AD_CLK,A/D转换器给FPGA一个回波时钟DCO,转换后的16 b数据与DCO同步,在每个DCO上升沿,FPGA获取转换后的16 b数字信号。