基于FPGA的TFT液晶显示时序控制器设计

2015-07-05陈建军金强宁章鹏刘凯丽

陈建军,金强宁*,章鹏,刘凯丽

基于FPGA的TFT液晶显示时序控制器设计

陈建军1,2,金强宁1,2*,章鹏1,2,刘凯丽1,2

(1.国家平板显示工程技术研究中心,江苏南京210016; 2.中国电子科技集团公司第五十五研究所,江苏南京210016)

针对某些仅绑定栅源驱动芯片而没有时序控制电路的液晶显示面板,设计了一款基于FPGA的SOPC嵌入式系统的时序控制器。它利用FPGA的逻辑电路实现LVDS视频信号的解码、灰阶扩展、RSDS信号编码、显示控制时序转换等功能,并通过FPGA中Nios II软核的串行口设置参数,编程GAMMA及VCOM电压,参数具有掉电保护功能。时序控制器中还增加了BIT检测电路,可实时査询电路运行状态。该时序控制器电路集成度高、功耗低,结构简单,适合特殊应用,具有较高使用价值。

TFT液晶显示;时序控制器;FPGA;SOPC;BIT

1 引言

在当今信息社会,彩色TFT(Thin Film Transistor)液晶显示器已经广泛地应用在我们生活的各个方面,液晶显示面板的制造技术不断完善成熟,已形成标准化、规范化的电气接口形式,如低电压差分信号LVDS(Low Voltage Differential Signaling)、bit位数字RGB信号等。近来,随着液晶显示面板集成度越来越高,栅源驱动芯片Source driver与Gate driver均绑定在玻璃面板上,导致与面板的电气接口发生根本性改变。时序控制器(Timing controller)作为液晶显示器的核心部分之一,对液晶显示系统的正常工作起着关键的作用,它为液晶显示器前级电路与液晶面板之间提供桥接,接收并处理前级电路输出的标准数字视频信号,产生特定的时序信号控制液晶面板正常工作。目前,国内、外各液晶面板厂商设计的时序控制电路通常采用商用专用控制芯片,这样时序控制电路只适合专一的液晶面板使用。本设计采用工业级FPGA(Field Programmable Gate Array)来实现商用控制芯片的所有功能,同时集成了状态BIT (Built In Test)检测及参数可编程设置等功能,能满足特殊应用场合苛刻环境下的可靠性要求。而且,硬件电路的通用化设计可以适应不同厂商、不同规格的液晶面板。

2 液晶显示面板

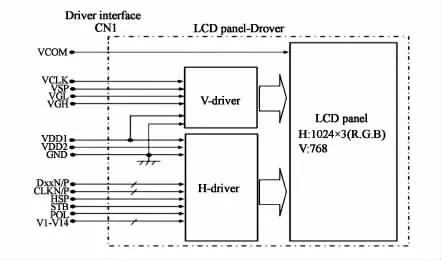

图1为一款典型的仅绑定栅源驱动芯片而没有时序控制电路的彩色液晶显示面板结构,本文针对该款显示面板展开时序控制电路设计[1]。

图1 液晶显示面板的结构框图Fig.1Block diagram of LCD panel

液晶显示面板基本参数:

分辨率:1 024(H)×768(V)

显示颜色:RGB

显示灰阶:每色64级,262144级色阶

电气接口:

·数据、扫描及控制通道:RSDS(Reduced Swing Differential Signaling)低摆幅差分信号,扫描时钟、水平垂直扫描起始脉冲、水平垂直方向控制、差分信号极性控制、数字锁存脉冲等;

·芯片支持电压;

·VCOM电压和GAMMA电压(Vγ1~Vγ14)。

3 时序控制电路设计

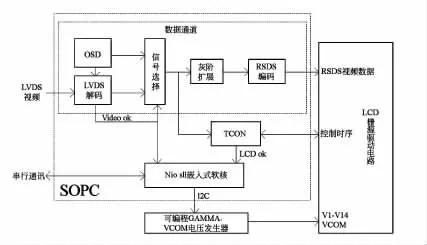

图2为时序控制电路结构框图。

图2 时序控制电路结构方框图Fig.2Block diagram of timing controller circuit

时序控制电路[2-4]采用基于Altera公司FPGA的SOPC(System On Programmable Chip)技术来实现[5-6],它由数据处理通道、显示控制时序变换、驱动电压发生器及嵌入式NiosII软核[7]等部分组成。

3.1数据处理通道

数据处理通道在FPGA内实现,它由LVDS解码电路、灰阶扩展及RSDS输出接口电路等部分构成。

3.1.1LVDS解码电路

LVDS接口是为了解决TTL电平方式传输宽带高码率数据时功耗大、电磁辐射大等缺点,由美国国家半导体公司研制的一种数字视频传输方式,在液晶面板上得到了广泛的应用。本文所设计的时序控制器接收单路四通道8 bit LVDS视频信号,同时兼容VESA LVDS信号格式和JEIDA LVDS信号格式。

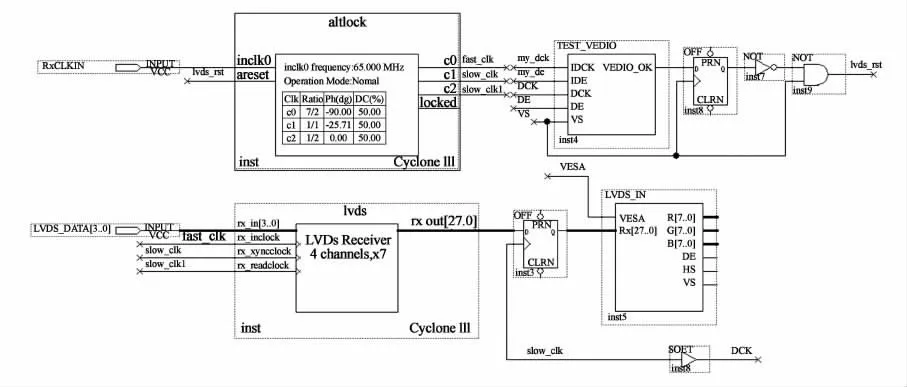

图3 LVDS解码电路Fig.3Decoding logic for lvds

LVDS解码电路如图3所示。

外部65 MHz的LVDS时钟RxCLKIN接入锁相环(PLL)IP核,根据LVDS时钟与数据的相位关系,产生3个时钟:

fast_ck:频率为227.5 MHz,相位为-90°。

slow_ck:频率为65 MHz,相位为-25.71°。

slow_ck1:频率为32.5 MHz,相位的为0°。

四通道LVDS视频数据接入LVDS解串行化器(LVDS SERDES),设置数据通道为4,SERDES因子为7,选择外部锁相环。分别将PLL产生的fast_ck接至解串行化器的rx_inclock,slow-ck接至解串行化器的rx_syncclock,slow_ck1接至解串行化器的rx_readclock。解串行化器输出28位含有视频数据和时序信号的并行数据,slow_ck作为输出的点时钟DCK。

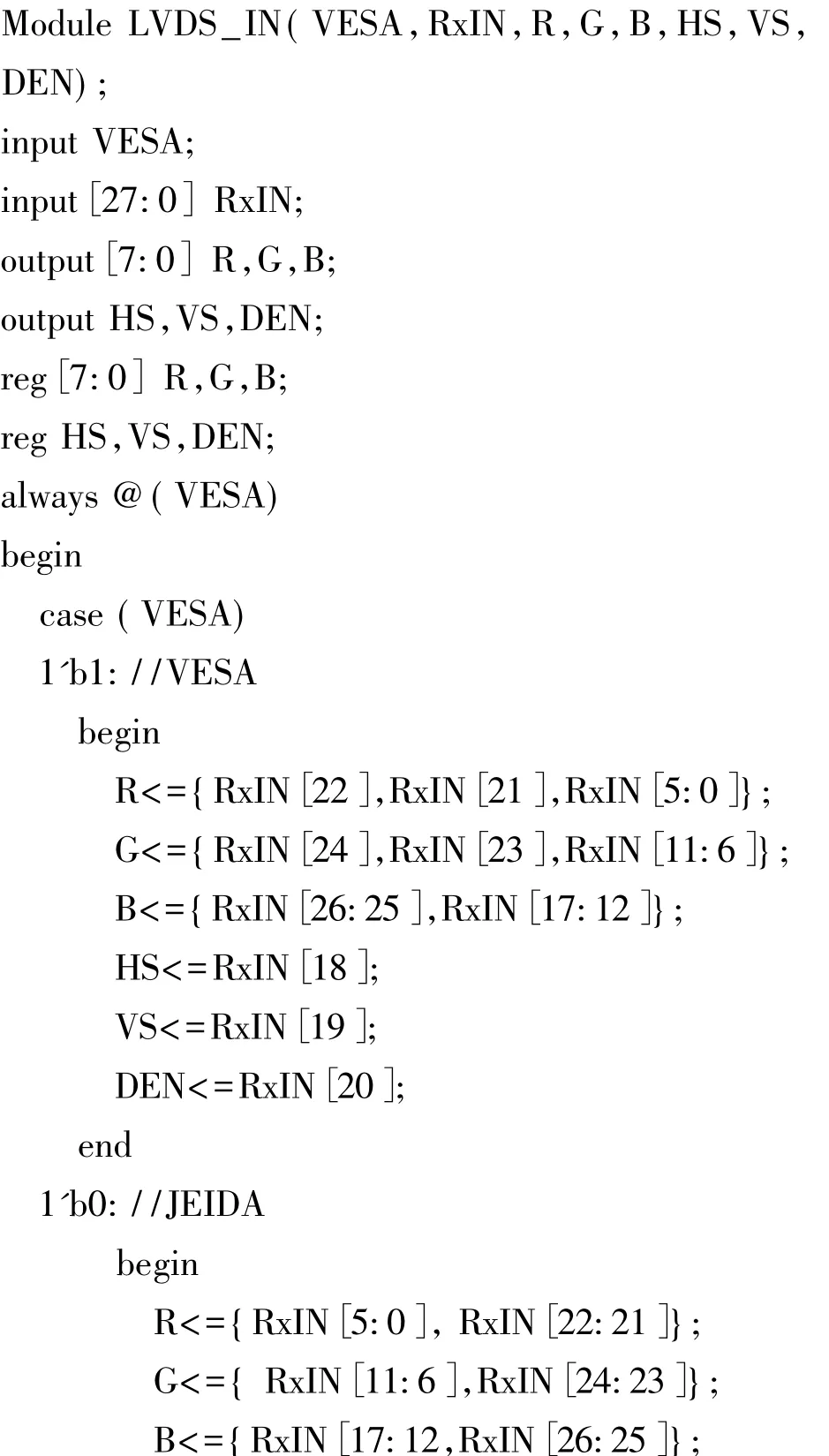

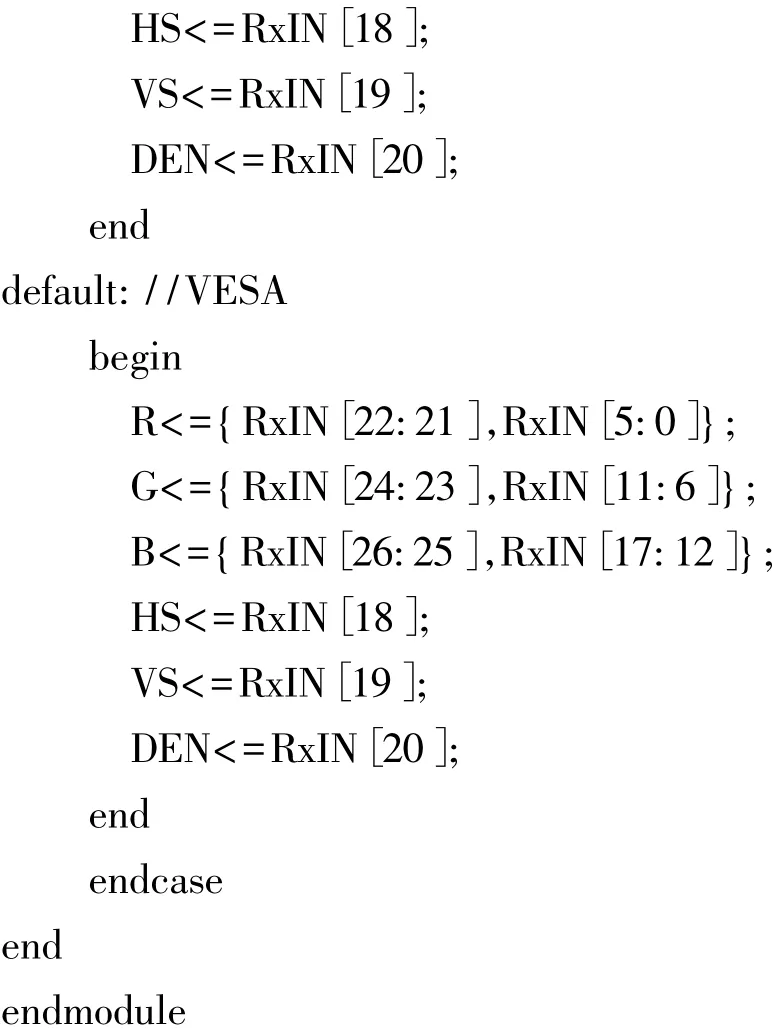

目前有两种流行的LVDS编码格式,一种是VESA标准[8],另一种为JEIDA标准[9],两种编码的Data Mapping不同。LVDS_IN模块根据外部输入信号格式标准,从28位并行数据中译码出红,绿,蓝视频数据和时序信号HS,VS,DE。为了使时序控制器可以兼容6 bit8 bit VESA及8 bit JEIDA三种视频输入格式,在LVDS_IN模块的设计中,当VESA脚电平为高时,采用8 bit VESA编码,VESA脚为低电平时采用6 bit VESA或8 bit JEIDA编码,6 bit VESA与8 bit JEIDA编码是兼容的,当外部输入的第四对LVDS差分数据线使用时是8 bit视频数据,否则是6 bit数据。

LVDS_IN模块用硬件描述语言Verilog编写,程序清单如下:

3.1.2灰阶扩展

时序控制器的外部接口为RGB各8 bit视频数据,而显示屏的源驱动器为6 bit,我们采用了PD+FRC算法来实现显示器的灰阶扩展[10-13],使显示屏具有253×253×253种颜色体现能力。

PD(Pixel Dithering)技术是指用交替的点图案去模拟在显示器中不能使用的颜色的过程。采用不同的真实灰阶实现亮度融合,产生感应灰阶。

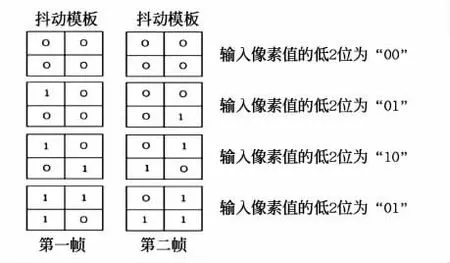

FRC(Frame Race Control)是为了消除静态抖动算法引起的条纹效应,更好地还原图像质量,使显示的图像平滑柔和,利用人眼视觉惰性而实现的动态抖动算法。算法示意图如图4所示。

图42 bit Bayer动态抖动矩阵Fig.42 bit Bayer dynamic dithering matix

由图4可以看出,动态抖动算法为了消除固定抖动模板引起的条纹效应,采用隔帧变换抖动模板的方法,在时域上,由于抖动矩阵的循环变换而导致不同帧在抖动后的图案中同一位置处的像素明暗轮换出现,但图像的灰度保持不变,条纹效应被平均。

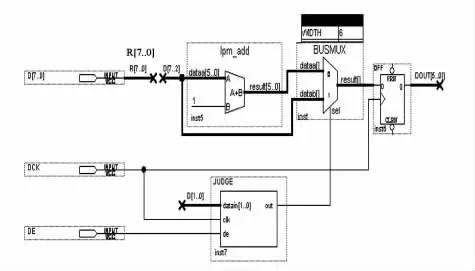

根据上述算法,在FPGA内用图形输入法实现的电路如图5所示。

图5 用FPGA实现FRC+PD算法的电路图Fig.5Logic in FPGA for implementing FRC+PD algorithm

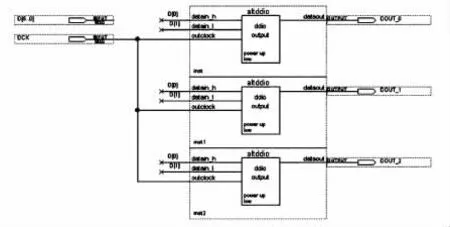

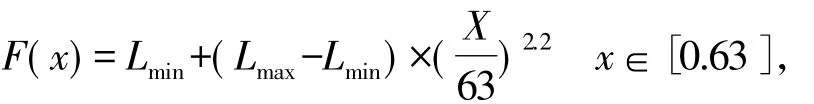

3.2RSDS编码

时序控制器采用RSDS接口驱动液晶面板的源极驱动器。RSDS接口有诸多优点,包括低功耗、低压差分摆幅以及低电磁辐射等。RSDS按串行模式传送数据,信号触发是双沿的,数据应进行倍速编码。根据面板的接口要求,每种基色的6 bit数据编码成三对RSDS差分对,全彩色视频数据编码成9对差分数据信号及一对时钟信号。数据倍速编码电路如图6所示。

图6 数据倍速编码电路Fig.6Double data rate logic for image data

电路中采用了Altera的双数据速率I/O IP核Altddio_out。Altddio_out核是参数可配制的,并针对Altera FPGA结构进行了优化,在参考时钟的上升沿和下降沿发送数据。

差分输出时钟与参考时钟理论上相差90°,在实际电路中用锁相环调整输出时钟的相位,抵消内部电路和布线延时,使输出时钟在数据跳变的中心位置,确保接收电路的时序裕度。

3.3显示时序转换

时序控制器的显示时序转换电路将外部输入的符合VESA标准的视频信号转化为显示屏工作所需的时序信号。为了提高时序控制器的通用性,采用DE Only控制方式,即仅使用外部视频信号的DE和DCLK两个时序信号来产生显示屏栅源驱动器等所需的所有控制信号。

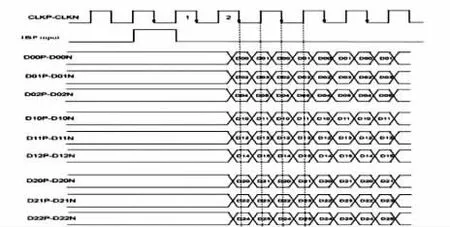

源驱动器主要信号的时序关系如图7所示。

图7 源驱动器主要信号的时序关系Fig.7Timing sequence of source-driver’s signals

与源驱动器相关的信号有:

(1)HSP1/2:源驱动器的启动脉冲输出或输入。

(2)CLKN,CLKP:RSDS标准的移位时钟。

(3)DXXP,DXXN:RSDS标准的视频数据。

(4)STB:数据锁存脉冲。

(5)POL:极性控制信号。

(6)R/L:左右移位方向控制。

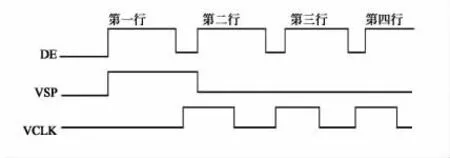

栅极驱动器主要信号的时序关系如图8所示。

图8 栅极驱动器主要信号的时序关系Fig.8Timing sequence of Gate-driver’s signals

与栅极驱动器相关的信号有:

(1)VSP1/2:栅驱动器的启动脉冲输出或输入。

(2)VCLK:栅驱动器的时钟。

(3)U/D:上下移位方向控制。

3.4驱动电压产生电路

时序控制器外部供电为直流+3.3 V,通过DC/DC变换,产生FPGA工作所需的+2.5 V、+1.2 V以及液晶面板工作所需的VDD1(+3.3 V),VDD2(+10 V),VGH(+20 V),VGL(-8 V)。GAMMA电压有14路,分别是Vγ1~Vγ14,1路公共电极电压VCOM,采用TI公司的BUF16821来实现[14]。BUF16821是可编程的GAMMA电压发生器和VCOM校准器,它能提供16条可编程GAMMA电压通道,以及2路可编程VCOM电压通道。所有GAMMA和VCOM通道提供一个轨到轨输出,此输出在10 mA负载时,通常在任一电源轨的150 mV内摆动,具有较高的精度。NiosII软核通过一个I2C接口对所有通道进行编程,最终的GAMMA和VCOM设定值可被存储在时序控制器上非易失性存储器中。

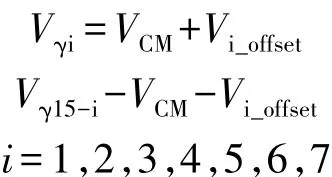

3.4.1GAMMA电压的设置

GAMMA电压Vγ1~Vγ7与Vγ8~Vγ14以中点电压VCM为中心在高低电压区对称分布,VCM固定设置为VDD2的一半。NiosII软核程序中以7个偏移量V1_offset~V7_offset为变量来调整14组GAMMA电压。

GAMMA电压值设定公式为:

通过对7组对称的GAMMA电压的设定,使LCD面板满足GAMMA=2.2的要求。

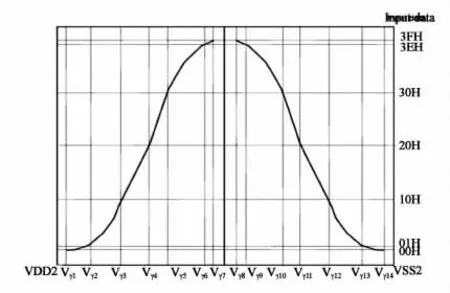

如图9所示GAMMA电压与视频数据关系: Vγ1,Vγ14对应灰阶00H,Vγ2,Vγ13对应灰阶01H,Vγ3,Vγ12对应灰阶10H,Vγ4,Vγ11对应灰阶20H,Vγ5,Vγ10对应灰阶30H,Vγ6,Vγ9对应灰阶3EH,Vγ7,Vγ8对应灰阶3FH。

GAMMA为2.2时亮度与灰阶的关系为:

其中x为灰阶值,F(x)为其所对应的亮度,Lmax最高亮度值,Lmin最低亮度值。

我们先将信号源的灰阶设为最高(3FH),通过调整V7_offset变量值使LCD面板达到最高亮度Lmax,再将信号源的灰阶设为最低(00H),通过调整V1_offset使LCD面板达到最低亮度Lmin。确定Lmax和Lmin后便可以调整其他GAMMA电压的偏移量,使各灰阶亮度满足公式的要求,从而使LCD面板的GAMMA特征为2.2。

图9 GAMMA电压与视频数据关系[1]Fig.9Relationship between GAMMA voltages and image data

3.4.2VCOM电压的设置

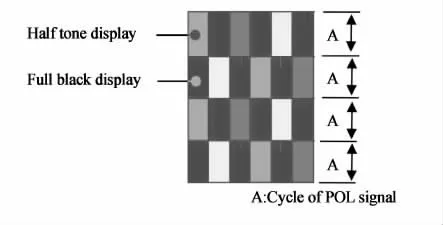

从理论上看,VCOM应设定在GAMMA电压的对称中心,即VCOM应等于中点电压VCM,然而实际上LCD面板内的TFT寄生电容,会产生电压耦合效应,使像素电压在TFT关闭时,受到栅极电压变化的影响,而偏离由数据线所写入的电压。为了补偿这个电压变化,VCOM必须调整到低于中点电压的某一值。

根据面板驱动的反转模式,采用如图10所示的按亚像素反转的测试画面作为显示信号源,PC机通过串行口发送指令和参数给NiosII软核,通过一个I2C接口调整VCOM值,用专用仪器测量其“flicker”值,当画面的“flicker”值最小时VCOM值为最佳值。

GAMMA电压和VCOM电压的设置参数值被存入可掉电保存的存储器中。在上电复位后被读出来设定GAMMA电压和VCOM电压。

图10 “flicker”测试画面Fig.10Image for flicker testing

4 BIT检测电路设计

为了提高时序控制器的可检测性,设计了若干嵌入式检测电路。检测状态可通过NiosII软核经由串行通讯口送出。

4.1外部视频信号有效性检测

为了提高LVDS解码电路的可靠性,在图3所示电路的TEST_VIDEO模块中设计了外部视频检测电路,通过检测外部输入的DCLK和DE信号的频率来判断外部视频信号有效性。当外部视频中的DCLK和DE的频率特征符合VESA标准时序时,便判定为有效视频,不符合则判外部视频失效,并置标志位,供软核读取,此时将内部产生的蓝底“无信号”白字视频的警示信息切换至视频数据处理电路,通过时序控制电路在TFT液晶面板上显示,并同时定时复位锁相环,以保证定时判断DCLK和DE信号的频率,当满足标准时,TFT液晶面板恢复显示外视频。

实际应用中在极端低温环境下,PLL常失锁且不能恢复,造成显示器显示失效,该电路的应用保证了显示屏的可靠性。

4.2驱动电路工作状态检测

在液晶面板的栅源驱动电路中都有一组双向移位寄存器,寄存器的位数与所控制的行列驱动线数一致,栅驱动电路中有768个寄存器,源驱动电路中有1 024×3个寄存器。移位寄存器的数据端接行列启动脉冲,双向移位寄存器的移位方向分别决定了显示屏的左右倒向和上下倒向显示。驱动电路按照特定的时序运行,栅驱动电路的启动脉冲频率与场频一致,移位时钟为行同步脉冲,移位寄存器周而复始地逐条开启/关闭扫描线,在逐行扫描768行后,移位寄存器末端输出被送入到时序控制电路。源驱动电路的启动脉冲频率与行频一致,移位时钟为数据时钟,移位寄存器重复逐条开启/关闭数据锁存器,使数据锁存器顺次接收显示数据,在逐点扫描1 024点后,移位寄存器末端输出被送入到时序控制器。

从上分析可知,栅源驱动电路在正常工作时都会输出一个与行列启动脉冲频率一致,相位相异的信号到时序控制器,通过检测此信号的有无便能知悉面板驱动电路是否正常工作。

5 设计结果

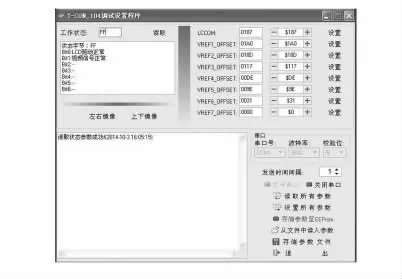

我们所设计的时序控制器连接LCD面板的产品实物图如图11所示,PC机上运行的调试软件界面如图12所示。

图11 TCON产品实物图Fig.11Performance of the TCON board

图12 调试软件界面图Fig.12Interface of debug software

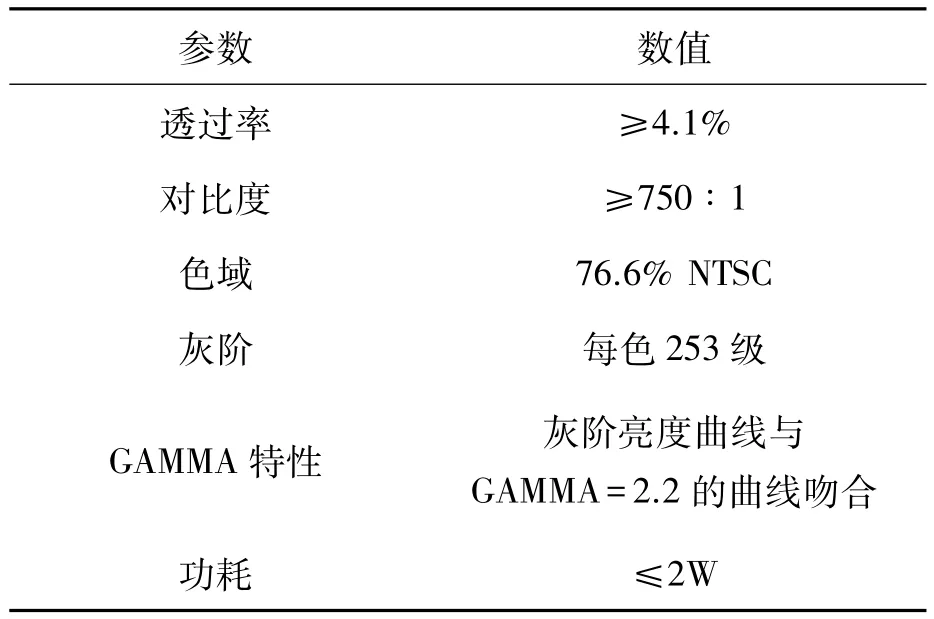

使用本文所述的时序控制器后,液晶显示面板的主要光电性能指标如表1。

表1 主要光电参数Tab.1Major optical parameters

6 结论

使用该时序控制器,液晶显示面板的灰阶体现正确,画质稳定,功耗比常规产品要低。

时序控制器所具有的嵌入式检测功能,提高了产品的可检测性;采用数字编程的GAMMA及VCOM电压,数据位达10 bit,调整精度高,稳定性可以得到充分保证。

时序控制器还可由跳线设定转入显示其自产生的老练画面,简化了产品老练工序。

时序控制器所有元器件、原材料均按工业级标准严格选用、筛选,设计上充分考虑参数的冗余度,核心芯片采用了工业级FPGA作为主控芯片进行设计,提高了可靠性,经实验验证,产品可以在-55~+75℃的温度范围内稳定工作,具有良好的环境适应性。

该时序控制器已广泛应用在轮船、车辆、飞行器使用的各种液晶显示设备中,其集成度高、功耗低,结构简单等特点,获得了较高的使用价值。

[1]NLT Technologies,Ltd.NL10276HC20-39 Preliminary Data Sheet[CD].USA:NEC,2012.

[2]金强宁,洪乙又,李慧芝,等.基于mini-LVDS技术的TFT-LCD彩色液晶显示屏的驱动研究及应用[J].光电子技术,2009,29(3):196-200.

Jin Q N,Hong Y Y,Li H Z,et al.The application and study of Color TFT-LCD panel driver based on mini-LVDS technology[J].Optoelectronic Technology,2009,29(3):196-200.(in Chinese)

[3]刘杰,程松华,张永栋,等.基于Mini-LVDS技术的TFT-LCD时序控制器的设计[J].液晶与显示,2014,29(2): 238-244.

Liu J,Cheng S H,Zhang Y D,et al.Design of TFT-LCD timing controller based on mini-LVDS technology[J].ChineseJournal of Liquid Crystals and Displays,2014,29(2):238-244.(in Chinese)

[4]戴亚翔.TFT LCD面板的驱动与设计[M].北京:清华大学出版社,2008:42.

Dai Yaxiang.Design and Operation of TFT LCD Panel[M].Beijing:Tsinghua University Press,2008:42.(in Chinese)

[5]杨军,张伟平,赵嘎,等.面向SOPC的FPGA设计与应用[M].北京:科学出版社,2012.

Yang J,Zhang W P,Zhao G,et al.FPGA Design and Application for the SOPC[M].Beijing:Science Press,2012.(in Chinese)

[6]宋跃,卢俊平,雷瑞庭,等.基于Nios II的液晶屏控制器SOPC设计[J].液晶与显示,2014,29(1):48-54.

Song Y,LU J P,Lei R T,et al.SOPC design on LCD controller based on Nios II[J].Chinese Journal of Liquid Crystals and Displays,2014,29(1):48-54.(in Chinese)

[7]刘东华.Altera系列FPGA芯片IP核详解[M].北京:电子工业出版社,2014:344-365.

Liu D H.Altera IP core series FPGA Chip Comments[M].Beijing:Electronic Industry Press,2014:344-365.(in Chinese)

[8]VESA.TV Panels Standard[S].USA:VESA,2006.

[9]JEIDA.JEIDA-59-1999 Digital Interface Standards for Monitor[S].Japan:JEIDA,1999.

[10]陈建军,周旭,张小芸.感应灰阶的产生技术及其在液晶显示器上的应用[J].光电子技术,2013,33(2):113-114.

Chen J J,Zhou X,Zhang X Y.An algorithm of spatial grey-scale and application for liquid crystal display[J].Optoelectronic Technology,2013,33(2):113-114.(in Chinese)

[11]Limb J O.Design of dither waveforms for quantized visual signals[J].Bell System Technical Journal,1969,48: 2555-2582.

[12]Floyd R W,Inberg L S.An Adaptive Algorithm for spatial grey scale[C].Proceedings of the SID,Los Angeles,1976,17 (2):75-77.

[13]Robin S H.Process for producing shaded colored images using dithering techniques:USA,5757347[P].1998-05-26.

[14]Texas Instrument Incorperated.Programmable Gamma_voltage generor and Vcom calibrator with integrated two-bank memory[CD].USA:TI,2011.

FPGA-based TFT LCD timing controller design

CHEN Jian-jun1,2,JIN Qiang-ning1,2*,ZHANG Peng1,2,LIU Kai-li1,2

(1.National Engineering Research Center for FPDs,Nanjing 210016,China; 2.The 55thResearch Institute of China Electronics Technology Group Corporation,Nanjing 210016,China)

A FPGA-based SOPC embedded system timing controller is designed for some LCD panel driver chips which only bonding with source and gate circuits.It uses FPGA logic circuits to implement the functions such as LVDS video signal decoding,grayscale expansion,RSDS signal encoding,and control timing conversion display.Through the serial port setup parameters in FPGA soft-core Nios II,GAMMA and VCOM voltage can be programmed.Those parameters have power-down protection.The timing controller also adds BIT detection circuit which check the operation status in real-time.This high integration,low power consumption,simple structure timing controller circuit is suitable for special applications with high use value.

TFT-LCD;timing controller;FPGA;SOPC;BIT

TN141

A

10.3788/YJYXS20153004.0647

陈建军(1966-),男,江西高安人,高级工程师,长期从事图像处理方面的研究。E-mail:nedichen@aliyun.com

金强宁(1962-),男,江苏南京人,研究员,长期从事平板显示、光电子技术方面的研究。E-mail:jqn2004@126.com(联系人)

1007-2780(2015)04-0647-08

2014-12-06;

2015-01-21.

*通信联系人,E-mail:jqn 2004@126.com

章鹏(1987-),男,安徽滁州人,硕士,助理工程师,从事平板显示技术方面的研究。E-mail:zpzone5971@ 163.com

刘凯丽(1988-),女,江苏泰州人,硕士,助理工程师,从事平板显示技术方面的研究。E-mail:kelly07050505@ 126.com