基于FPGA的线阵CCD实时图像采集系统

2015-06-22章金敏张菁陈梦苇

章金敏,张菁,陈梦苇

(武汉理工大学理学院,湖北武汉430070)

基于FPGA的线阵CCD实时图像采集系统

章金敏,张菁,陈梦苇

(武汉理工大学理学院,湖北武汉430070)

设计了一种基于现场可编程逻辑器件的线阵CCD实时图像采集系统。系统采用线阵CCD TCD2252D作为图像传感器,使用CCD专用信号处理芯片AD9826对CCD信号去噪并实现高速A/D转换,同时用USB接口芯片完成CCD数据的传输,最后在上位机显示采集的图像数据。整个系统由基于Verilog的CCD驱动模块、CCD输出信号处理模块、双口RAM缓存模块、USB接口控制模块等组成,结合上位机模块实现对CCD输出图像的准确采集、显示和保存。实验结果表明,该系统能实时采集和显示图像信息,USB传输速度可达28 MB/s,系统实时性好。

实时采集;电荷耦合器件;现场可编程逻辑器件;信号处理

0 引言

目前,随着科学研究和工业生产的需要,越来越多的场合需要实时高速的图像采集处理系统。线阵CCD作为一种光电转换图像传感器,它利用光电转换原理将图像光信号转换为电信号,经过预处理和A/D转换后变为数字信号,通过一种上位机通信方式,可在逻辑器件的控制下实现对图像数据的采集传输,并在PC端进行后续处理。利用CCD采集图像具有检测精度高、处理速度快、抗干扰能力强、运行稳定等优点,其已广泛应用于图像采集、非接触式测量和实时监控等诸多领域[1]。

CCD器件的正常工作需要外加驱动时序脉冲,时序脉冲的产生方法有很多种,如数字电路驱动法、单片机驱动法、EPROM驱动法。虽然这些方法都可以产生时序脉冲,但是电路设计的难度大,兼容性差。本文直接使用FPGA来产生时序脉冲。FPGA高速、并行等优势使系统的设计非常灵活;FPGA的资源丰富,尤其是内部存储资源,可作为CCD数据的缓存,能够大大简化系统硬件电路的设计。

本文设计了一种基于FPGA的线阵CCD实时图像采集系统,它采用FPGA+USB的平台结构,以线阵CCD作为图像传感器,使用CCD专用信号处理芯片AD9826对CCD信号去噪并实现高速A/D转换,同时用USB接口芯片完成CCD数据的传输,最后在上位机上显示采集的图像数据。

1 系统设计方案

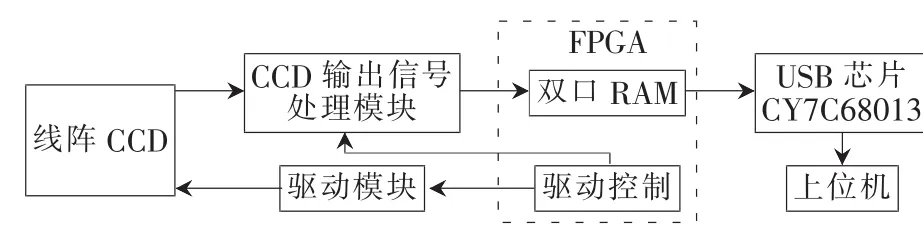

系统主要由CCD驱动模块、信号处理模块、数据缓存模块、双口RAM缓存模块、USB接口模块和上位机模块等组成,系统结构框图如图1所示。上电后,线阵CCD图像传感器在FPGA的驱动下接收前端图像信息,将光信号转换成电信号输出;然后,模数转换器AD9826对CCD输出信号作相关双采样并转换成数字信号,FPGA配置内部双口RAM作为数字信号的缓存区;最后,USB接口控制芯片把数字信号传输到上位机,在VS2008环境下开发上位机应用程序,实现图像数据的实时显示和存储,以便后续数据处理。

图1 系统结构框图

1.1 主控制器FPGA

FPGA是整个系统的核心,只有深入了解其内部结构,才能有效利用它。FPGA能够用较少资源实现较高的性能和更多的功能,满足低成本要求。本设计中的FPGA采用Altera公司的Cyclone IV系列的EP4CE6E22C8,其内部具有6 272个逻辑单元,30个M9K内存单元,270 Kbit嵌入式存储器,2个锁相环,92个用户I/O,可自由分配其功能与外部电路的连接。在该系统中,FPGA主要负责CCD的驱动控制、AD9826的采样控制、双口RAM的配置以及对USB接口芯片的控制。经过资源估算,该FPGA完全可以实现系统的功能。

1.2 CCD驱动模块

线阵CCD是采集系统的重要器件,完成光信号向电信号的转换。本文采用的线阵CCD是东芝公司生产的TCD2252D。TCD2252D是一款高灵敏度、低暗电流的双沟道彩色线阵CCD,它由光敏区、转移栅、模拟移位寄存器及信号输出单元组成。该器件包含3列2 700有效像元的光敏二极管,分别采集红绿蓝三色,最小像素单元尺寸为8μm×8μm,相邻光敏列间距为64μm[2]。

在线阵CCD图像采集应用中,CCD对驱动时序要求较为严格,只有精确的时序驱动才能保证CCD输出正确的像素信号。所以在CCD的应用中,首先要设计满足时序要求的驱动电路。根据芯片手册,该器件工作在5 V驱动脉冲、12 V电源条件下,其中6路驱动脉冲分别是转移脉冲SH、二相驱动脉冲F1和F2、采样保持脉冲SP、复位脉冲RS和箝位脉冲CP。

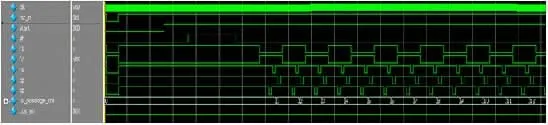

图2所示为TCD2252D驱动时序仿真波形,这六路驱动时序有着严格的时序关系。转移脉冲SH高电平期间驱动脉冲F1必须为高电平,而且SH的下降沿必须对应F1的高电平才能保证光敏区的信号电荷向模拟移位寄存器并行转移。驱动脉冲F1和F2是两个占空比为1∶2、频率为0.5 MHz且极性相反的方波脉冲;SP、RS、CP均是占空比为1∶8、频率为1 MHz的方波脉冲。SH脉冲的周期决定了光积分时间的长短。由于CCD正常输出时会有76个哑元像素和2 700个有效像素,所以在一个行周期内至少要有2 776个RS脉冲,从而可以计算出每次光积分所需的时间为TSH>2 776TRS=2 776μs。为了保证后续AD9826对CCD信号的有效采样,在仔细分析CCD输出信号特点后,设置一个RS上升沿计数器,当该计数器计数到64时置1,AD9826开始对CCD有效输出信号进行相关双采样。

图2 TCD2252D驱动时序

TCD2252D需要5 V的CMOS驱动电平,但FPGA输出为3.3 V的TTL电平,因此需要使用电平转换电路增强FPGA输出信号的驱动能力。TI公司研发的电平转换芯片SN74LVC4245能实现8位总线的3.3 V和5 V逻辑电平的双向转换,工作频率高达10 MHz,能满足本系统CCD驱动频率1 MHz的要求。

1.3 信号处理模块

由于CCD输出的是带有暗电流噪声和输出放大器复位脉冲串扰的模拟信号,因此必须进行信号处理才能为后续电路使用[3]。本系统中,使用ADI公司生产的专用CCD信号处理芯片AD9826,该芯片集成16位ADC,速度可达15 MS/s。作为模数转换芯片,其片内集成相关双采样(Correlated Double Sampler,CDS)等多种功能电路,提高了信号预处理的质量,简化了电路的设计。

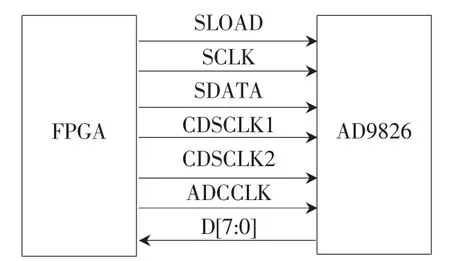

AD9826由VINR、VNG、VINB三路独立采样通道电路组成,每个采样通道都由输入箝位电路、相关双采样电路、偏移DAC和可编程增益放大器组成,并通过多路复用(MUX)接入一个16位模数转换器,采样输出信号通过8位并行数据总线分时输出16位数据。此处系统设计只取一路线阵CCD输出,选择VINR红色通道作为信号输入,采用单通道CDS和16 bit转换模式。CCD输出R信号经过隔直电容,将有效信号耦合输入到AD9826中VINR通道采样,其他两个通道要做接地处理,以防止对VINR通道产生干扰,如图3所示。

图3 模数转换电路接口

AD9826的工作模式可通过三线双向串行接口(SCLK、SLOAD、SDTATA)配置内部寄存器来设定。串行时钟SCLK最高频率为10 MHz,系统采用5 MHz频率,由主时钟50MHz分频可得。CCD输出信号幅值为0~4 V,不需要AD9826内部增益放大。

AD9826工作在单通道CDS工作模式下,CDS电路在每一像素周期内对输入的CCD信号采样两次。CDSCLK1的下降沿采样参考信号,CDSCLK2的下降沿采样有效信号。CDS电路输出的是两次采样值之差,消除了噪声,此时信号即为有效视频信号。

分析CCD输出信号特点,FPGA内部产生AD9826的工作时序,确保对CCD输出信号的正确采样。CCD连续输出2 700个有效像素单元信号之前,先输出64个哑元信号,此处在CCD第64个复位脉冲上升沿到来后FPGA设置采样使能信号cds_en有效。考虑到单通道CDS模式下,模数转换的数据会延迟3个采样时钟周期输出,在第2 768个复位脉冲上升沿后拉低采样使能cds_en,这样才能采集到完整的2 700个CCD像素信号。由于TCD2252D输出像元频率为1 MHz,AD9826的相关双采样时钟CDSCLK1、CDSCLK2和采样时钟ADCLK都设置为1 MHz。

1.4 数据缓存模块

数据缓存模块的功能是保证数据采集与传输的连续性。由于USB接口芯片的传输速率和A/D转换后的数据速率不同步,需要在两者之间增加一个数据缓存单元。目前常用的数据缓存器件有SRAM、双口RAM、FIFO等。高速数据采集系统中,常使用异步FIFO进行数据缓存,但只能对FIFO顺序地读/写数据。当需要存取特定单元的数据而非全部存储空间时,系统的灵活性大大降低。因此本设计采用双口RAM进行数据缓存,较好地解决了时钟不匹配的问题。

为了有效利用FPGA片内资源,简化电路设计,本文在FPGA内部定制双口RAM来缓存模数转换后的数字信号。EP4CE6E22C8内部集成了30个M4K RAM块,足够CCD输出一帧图像数据(2 700×16 bit)的缓存。此处在FPGA内部配置深度为4 096、位宽为16 bit的双口RAM。写时钟和AD9826的采样时钟ADCLK一致,写地址计数到2 699时,开始读RAM。读时钟与写USB端点FIFO的时钟IFCLK一致,保证数据传输的完整性和稳定性。

1.5 USB接口模块

USB接口模块的功能是将FPGA内部缓存的图像数据读出来,传输给上位机。USB电路设计的主要对象是USB接口控制芯片。目前,市场上多家半导体厂商提供USB接口控制芯片。本系统采用Cypress公司的EZUSB FX2系列USB接口控制芯片CY7C68013来传输图像数据。CY7C68013是一款具有USB2.0协议的微控制处理器,最高传输速率可达480 Mb/s,其片内集成USB2.0收发器、增强型的8051控制器、智能串行接口引擎(SIE)、4 KB的FIFO存储器和可编程I/O接口。

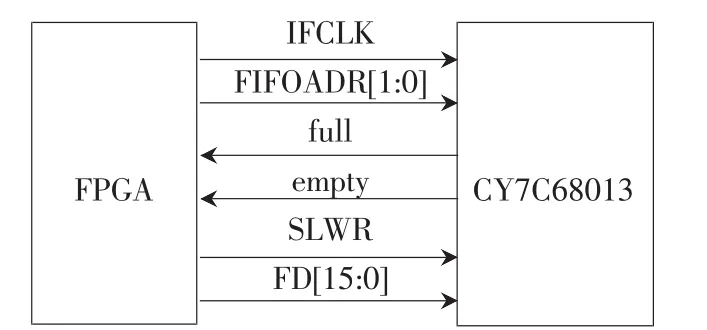

由于FX2芯片集成度高,用户在不熟悉复杂的USB底层协议的情况下也可以顺利开发USB接口设备。FX2有Slave FIFO和GPIF两种接口方式。此处采用Slave FIFO接口方式进行数据通信。在该模式下,FPGA作为主机,与USB通信传输数据不经过CPU的控制,而是经过芯片内部端点FIFO来传输,传输速度和CPU使用率更高。CY7C68013与FPGA的接口电路如图4所示,CY7C68013的并行数据引脚和控制状态引脚直接与FPGA接口相连即可。

图4 FPGA与FX2接口电路

USB接口设计主要是设计FPGA对USB接口芯片的逻辑控制[4]。FX2工作于Slave FIFO模式时,FPGA可以像对普通FIFO一样对FX2中端点的数据缓冲区进行读写。FPGA提供给芯片普通的时序信号、握手信号、读写信号和输出允许信号。本系统FX2工作于同步写方式,接口时钟由FPGA提供。当SLWR有效时,FD总线上的数据在每个时钟信号IFCLK上升沿时被写入FIFO。

FPGA程序中采用状态机实现同步写Slave FIFO方式,状态描述如下:(1)IDLE:总线空闲,当双口RAM中存储的数据达到设定深度时,写事件发生,转到状态state1;(2)state1:指向IN FIFO端口,激活FIFOADR[1:0],选择端点6,然后转向状态state2;(3)state2:判断FIFO“满”标志FLAGB的状态,如果为假,即FIFO不满,则转向状态state3,否则停留在该状态;(4)state3:写数据到总线上,激活SLWR,写数据到FIFO并增加FIFO指针,然后转向状态state4;(5)state4:检测是否有更多的数据要写,如果有则转向状态state2,否则转向状态IDLE。

1.6 上位机模块

上位机用来检测USB设备的连接状态,显示采集到的CCD数据。上位机采集有两个采集模式:实时采集模式连续地接收来自CCD的图像数据并显示;单帧采集模式单次接收来自CCD的图像数据并显示。保存数据将当前显示的一帧像素数据保存在安装目录下。

正常情况下,系统的USB设计包括三个方面的程序设计:固件程序设计、设备驱动程序设计和上位机应用程序设计[5]。Cypress公司为开发者提供了完善的软件开发工具包,开发者只需在官方例程固件框架上修改TD_Init函数即可变为自己的固件,至于USB驱动程序可以使用工具包自带的通用驱动程序,只需将驱动引导文件中对应的VID和PID修改成与固件一致即可。上位机程序在VS2008环境下开发,用户可以使用CYIOCTL控制函数类和CyAPI控制函数类来实现对USB设备读取数据。

2 实验分析

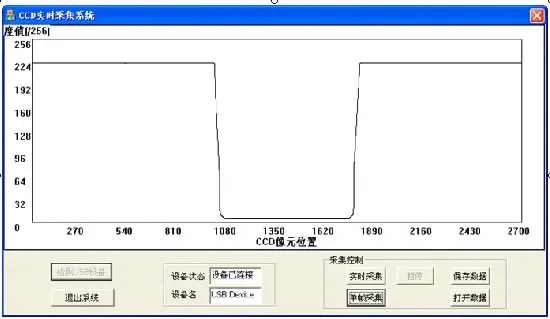

在室光条件下,系统以线阵CCD作为图像传感器,采集外界图像信息。当双口RAM中一帧数据存储完信号和读使能信号有效时,USB接口芯片开始传输CCD图像数据,送给上位机显示。图5为线阵CCD传感器部分遮光时采集到的一帧图像,图中低电平为CCD被遮部分的光强分布。由采集到的数据和上位机显示可以看出采集系统能够实现CCD数据的实时采集。

图5 CCD采集上位机显示

3 结论

本文设计了基于FPGA的线阵CCD实时采集系统,以线阵CCD作为图像传感器,使用CCD专用信号处理芯片AD9826对CCD信号去噪并实现高速A/D转换,同时用USB接口芯片完成CCD数据的传输,最后在上位机上显示采集的图像数据。系统采用集成了相关双采样、可编程增益放大器的专用CCD处理芯片,而不是像以往那样采用分立元件搭建模拟处理电路,并且充分利用FPGA内部RAM作数据缓存,简化了电路设计,减小了功耗,增加了系统的灵活性。系统扩展性较强,适用于机器视觉、非接触测量等领域。

[1]王庆有.CCD应用技术[M].天津:天津大学出版社,2000.

[2]陆荣鑑,陈丰饶.基于CPLD的彩色线阵CCD在木板色选系统中的应用[J].机电工程,2012(6):737-740.

[3]黄涛,廖胜,韩维强.基于AD9978A双通道的CCD相机设计[J].电子技术应用,2013,39(3):57-60.

[4]辛凤艳,孙晓晔.基于FPGA和线阵CCD的高速图像采集系统[J].计算机技术与发展,2012(8):205-207,212.

[5]薛圆圆,赵建领.USB应用开发宝典[M].北京:人民邮电出版社,2011.

Image real-time acquisition system based on FPGA and linear CCD

Zhang Jinmin,Zhang Jing,Chen Mengwei

(College of Science,Wuhan University of Technology,Wuhan 430070,China)

This paper presents a real-time image acquisition system which based on the linear CCD of FPGA.In the system,TCD2252D,the linear CCD,is used as image sensor,and AD9826,a complete analog signal processor for CCD,is used to sample the CCD analogy signal and realize high-speed A/D conversion,then CCD digital data are transferred to computer through USB interface chip,displayed in real time.The whole system consists of CCD driving module,CCD signal processing module,dual-port RAM module and USB interface module.The system can realize accurate acquisition,display and storage of CCD output pixel combined with USB application program.The result shows,the system can acquire and display the CCD image in real-time,and USB transmission speed can reach 28 MB/s.

real-time acquisiton;CCD;FPGA;signal processing

TN36

A

1674-7720(2015)13-0042-03

2015-02-06)

章金敏(1990-),男,硕士研究生,主要研究方向:光电检测与图像处理。

张菁(1990-),女,硕士研究生,主要研究方向:颜色识别与算法研究。

陈梦苇(1988-),女,硕士研究生,主要研究方向:光电信号处理、位移传感器研究。