基于FPGA的曼彻斯特编解码研究及IP核设计

2015-06-21章洁

章洁

(成都信息工程学院,四川成都 610225)

基于FPGA的曼彻斯特编解码研究及IP核设计

章洁

(成都信息工程学院,四川成都 610225)

曼彻斯特码在通信中有广泛的应用,其编解码器的设计是影响整个总线系统的关键因素,但是曼彻斯特码的时序很复杂。本文采用FPGA技术,深入研究曼彻斯特编解码原理,完成了曼彻斯特编解码的IP核设计,经过仿真验证了设计方法的正确性和工程应用性。

曼彻斯特编码 FPGA 解码器

1 引言

曼彻斯特码是一种双向码或分相码,是常用二元码的一种,曼彻斯特编码是一种自动同步的编码方式,常用于通信中对串行数据进行编码,其特点是利用码元中2种不同的电平跳变来对传输数据进行编码的,此外编码后每对码元都存在着电平跳变,这种特性和时钟信号的特性相同,可以在曼彻斯特码中提取出时钟信号;曼彻斯特码的每对码元都含有跳变,编码不会出现3个或者3个以上的“1”或者“0”,所以采用曼彻斯特码进行通信,可以确保数据在传输过程中没有直流成分,而且编码中暗含有时钟信号,数据的接收端能提取出数据发送端的时钟,因此,采用曼彻斯特码可以实现数据在接收和发送的同步。曼彻斯特码以其高稳定性和同步性而被广泛的应用于通信中,且更适合用于传输条件较差的环境中进行信息传输。

本文对曼彻斯特码的原理进行深入研究,选用VHDL或Verilog语言,编写曼彻斯特码的功能模块,将各模块组成一个通用的IP核,并用EDA设计工具进行仿真、综合和验证。不同于其他曼彻斯特编码器设计,本文设计中引入了储存器模块,最后把各模块组成一个通用的IP核。

2 编解码模块设计

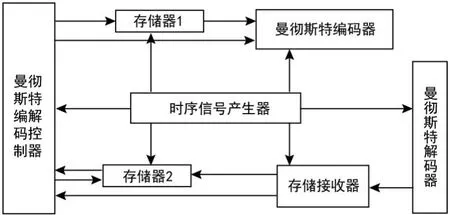

曼彻斯特编解码系统设计要完成的任务是实现数据的编码发送,同时还能解码接收,并进行整个通信过程的验证,因此,必须有一个模块化的整体设计。曼彻斯特编解码IP内核包括6个模块,即时序信号产生模块、存储器模块、曼彻斯特编解码控制模块、曼彻斯特编码模块、曼彻斯特解码模块、存储器接收模块,系统的结构框图如图1所示。

图1 曼彻斯特编解码系统结构图

其中时序信号产生器主要是为整个系统提供所需的各种时钟信号和复位信号;曼彻斯特编解码控制器是系统的核心,为系统提供输入数据和各个部分的控制信号;编码器是对传输的数据进行编码输出;解码器是对接收到的曼彻斯特码进行解码和串并转换;存储接收器为接收的数据分配相应的存储空间;存储器是在FPGA中开辟专门的存储空间对数据进行暂时的存储。

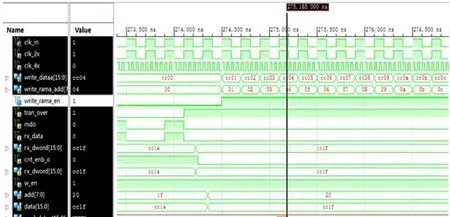

图3 数据编码和解码的波形仿真

如图4所示,当存储接收器开始向存储器2发送数据后,会通w_en反馈给控制器,控制器开始接收数据,控制器通过信号read_rama_en控制存储器2发送数据,存储器2根据控制器发送的地址信号,把对应存储空间的数据发送给控制器。

3 FPGA实现及测试

图4 控制器接收数据的波形仿真

至此系统的整个工作过程验证完毕,仿真中没有出现任何掉帧的问题,仿真和理论设计相符合。

本文对曼彻斯特码的数据通信过程进行验证。设计主要是完成数据从编码—发送—接收—解码的整个通信过程的验证,整个系统的验证如图2所示。

4 结束语

本文设计了基于FPGA的曼彻斯特编解码IP核,以通信功能为主,完成了系统各个模块的设计,并对各个模块进行了仿真和验证。从中可以看出曼彻斯特码的稳定性是很高的,作为IP软核,具有可兼容性及可扩展性,从仿真结果看,该曼彻斯特编解码IP核能完全达到光纤通信的要求,有一定的工程意义。

系统的工作开始是从控制器向存储器1发送数据开始的,存储器1起到一个对数据暂时存储的作用,控制器向存储器1发送数据的同时也向编码器发出控制信号,命令编码器开始工作。

图3是系统编码发送和解码输出的仿真,图中mdo是数据的曼彻斯特码传输,在控制器发送数据给存储器1时,也控制编码器工作,编码器一帧一帧的接收数据并对数据编码输出,当解码检测到编码中的同步字后,解码器开始对编码进行解码输出,rx_dword是解码器解码并进行串并转换后输出给存储器接收器的数据,存储器接收模块接收数据后,按照规定为数据分配相应的地址信息,并把地址信号和数据发送给存储器2。

[1]刘福奇.FPGA嵌入式项目开发实战[M].北京:电子工业出版社,2009.

[2]张剑,郭莉.基于Xilinx ISE的FPGA/CPLD设计与应用[M].北京:电子工业出版社,2009.

[3]何建新,高胜.数字逻辑设计基础[M].北京:高等教育出版社, 2012.

[4]何道君,谭明.FPGA的设计与应用[M].北京:清华大学出版社,2006.

[5]张伟.基于FPGA的通信接口模块设计与实现[J].电子科技, 2012,25(7):95-98.

Research on Manchester Encoding and Decoding Based on FPGA and Design on Its IP Core

ZHANG Jie

(Chengdu University of Information Technology,Chengdu Sichuan 610225,China)

Manchester code is used widely in field of communication.The design on codec is a key factor which affects the whole bus-system,and the time sequence of Manchester code is very complex.In this paper,the principle of Manchester code is studied in depth by using the FPGA technology,and the IP core design is completed for Manchester coding and decoding.The simulation results show that this design method is correct and has some engineering application value.

Manchester coding;FPGA;decoder

F224-39

A

1008-1739(2015)12-67-2

定稿日期:2015-05-26

四川省教育厅2013年自然科学基金课题(13ZB0082)