基于FPGA的可反馈式同步串行通信技术

2015-06-15蒋欣等

蒋欣等

摘 要: 为了实现可反馈式高速同步串行总线设计,提出基于FPGA使用硬件描述语言(HDL)和利用串行通信的本身电气特性设计出可反馈式电路,实现高可靠、高速率的同步串行总线通信方法。在工程应用中验证了其高速率和高可靠性的总线传输特性,为提高LRM(现场可更换单元)级之间总线速率提供参考。

关键词: 数据传输; FPGA; 串行总线; LVDS; 高级数据链路控制规程

中图分类号: TN915?34 文献标识码: A 文章编号: 1004?373X(2015)12?0139?04

0 引 言

同步串行高速总线在通信领域、自动控制领域发展迅猛,同时具有高可靠性、高传输速率的串行通信总线也在机载航电系统中得到广泛应用。同步串行高速总线不仅在成本、抗干扰能力和抗电磁干扰(EMI)的能力等方面能够大大满足现在高度综合化、高度小型化的现场可更换模块(LRU模块)级机箱内模块与模块之间的通信要求,也能够利用同步串行总线灵活简单的物理特性设计出可反馈式电路,增加通信的可靠性。

本文提出了一种基于FPGA的可反馈式硬件电路设计,采用硬件描述语言(HDL)实现了最高可达12.5 Mb/s的同步串行总线。

1 方案设计

随着高集成度、高综合化的机载航电设备的研制要求,在硬件设计中采用超大规模的FPGA和可反馈式电路设计,满足体积小、重量轻、功耗低的高可靠性的航电设备设计需求。

1.1 原理设计

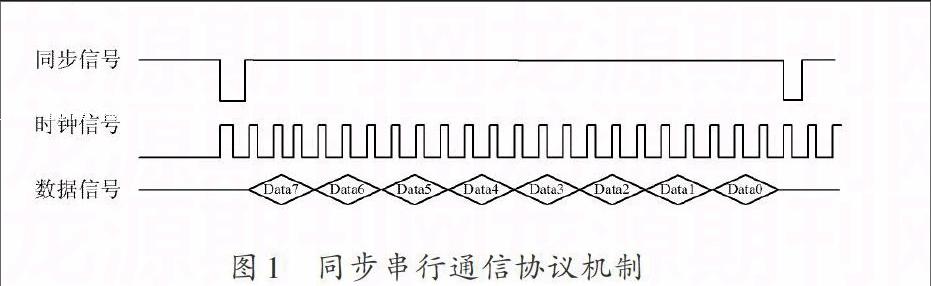

高速同步串行通信机制采用三线制同步串行通信,其中包括:帧同步信号、时钟信号和串行数据。同步信号是发送端在同步时钟的上升沿发出一个“低脉冲”给接收端,进行串行数据通信握手。在低脉冲上升沿完结后的第一个同步时钟周期的上升沿,连续发送8 B的串行通信数据,发送端数据发送完毕后的第一个时钟周期的上升沿,发送端发送一个“低脉冲”给接收端,进行释放数据通信握手。同步串行通信的时序图,如图1所示。

图1 同步串行通信协议机制

串行同步传输过程中,发送端和接收端必须使用共同的时钟源,才能保证它们之间的通信同步。同步数据传输时,在帧同步脉冲信号触发下,串行数据信息以连续的数据帧形式发送,每个时钟周期发送l B的数据。

采用LVDS标准的同步串行通信模式,利用LVDS标准的差分数据传输的电气特性,提高串行通信线路的抗干扰能力和长距离数据传输的准确性。在控制模式上,在发送端利用编码器把待发送数据和同步时钟组合在一起,通过物理差分数据线发送到接收端;接收端的解码器按照特定的数据格式(数据帧)从数据流中解析出同步时钟频率和数据,共计4对LVDS差分线,实现发送端和接收端的全双工同步串行通信。

在LVDS标准的电气特性上,数据通信格式采用了HDLC(高级数据链路控制规程)以“帧”为数据传输的基本单位(如表1所示),在所发送数据帧的帧头增加数据标志序列,接收端检测出该标志序列来实现同步。帧格式如表1所示。

表1 帧格式

1.2 硬件设计

将具有同步机制的串行通信应用在一个高度综合化的航电设备中,不仅需要通信原理的高可靠性,也需要在物理电气连接上的高可靠性。在实现高速、稳定的同步串行通信时,也需要进行发送响应触发机制和接收备份机制,保证发送数据的一致性和可侦测性,以及接收数据的有效性,因此,本文的同步串行通信硬件电路设计增加了发送端和接收端的可反馈式硬件电路设计。

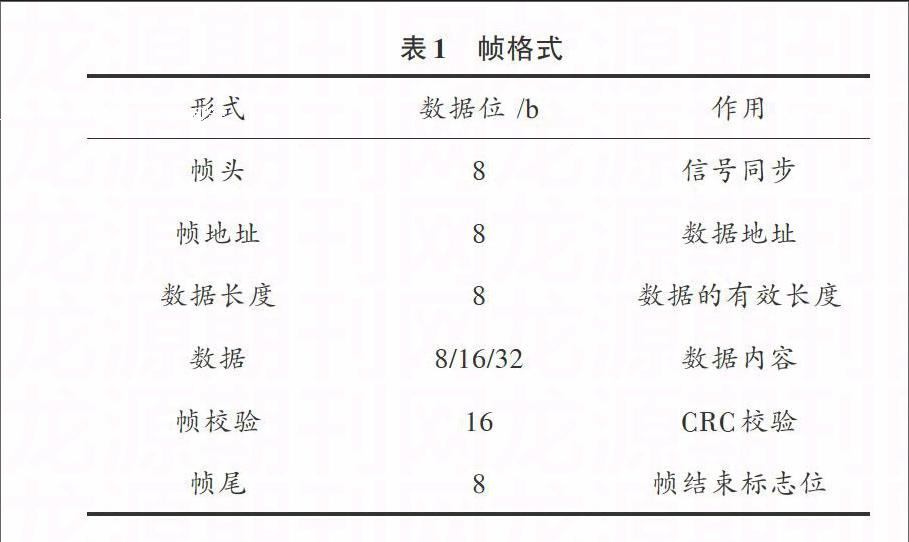

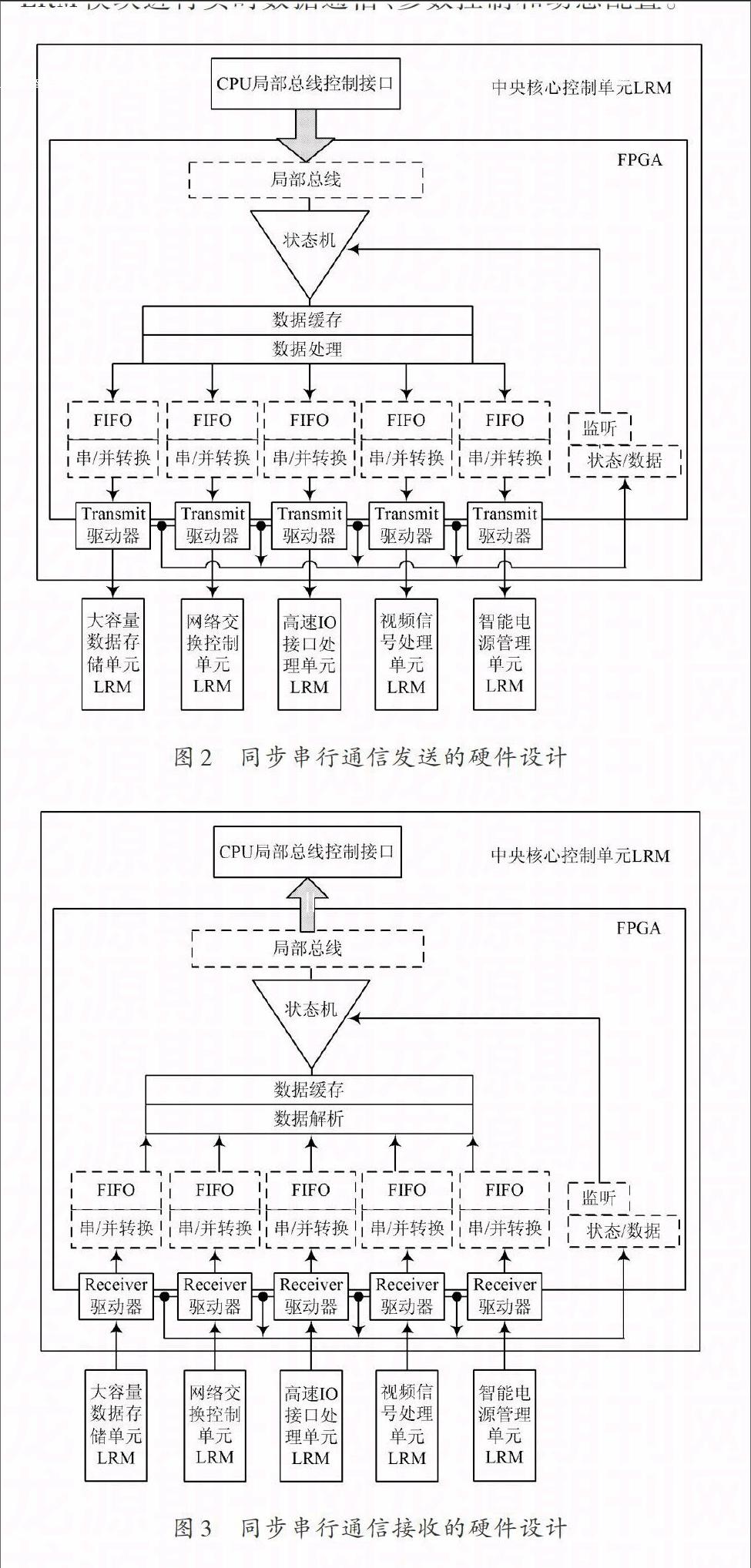

FPGA的串行通信接口与LVDS驱动器连接,发送端设计了硬件的发送反馈,在接收端设计了硬件的接收备份,同时在FPGA的内部采用发送比较器和接收缓冲器的冗余处理,以保证发送端的数据监听正常,接收端的数据双重备份,防止数据在发送或接收的过程中,产生丢数或者误码。高可靠性的同步串行通信电路硬件设计如图2和图3所示。

将可反馈式同步串行通信在速率快和通道多的综合化航电设备中使用,则具有高可靠的通信机理是保证综合化航电设备运行正常的基础。可反馈式同步串行通信的工程化应用设计如图4所示,其中,综合化航电设备都是采用现场可更换模块(以下简称“LRM”),中央核心控制单元LRM与其他5个LRM模块之间需要实时响应。

中央核心控制单元LRM通过同步串行通信采用点对点全双工模式,分别与智能电源管理单元LRM,高速I/O接口处理单元LRM,视频信号处理单元LRM,大容量数据存储单元LRM,网络交换控制单元LRM这5个LRM模块进行实时数据通信、参数控制和动态配置。

如果中央核心控制单元同时接收、解析这5个LRM模块的串口通信数据,面临的困境有:

(1) 依照目前CPU集成的串口控制器的处理速度将不能满足综合化航电设备通信的实时性要求;

(2) 采用传统的点对点的通信方式,CPU不能有效监控数据是否发送成功,只能等待握手时间超时,严重影响系统正常运行。

要实现如此高速可靠的串行通信,采用基于硬件的反馈机制处理同步串行通信保证了综合航电设备内部各个LRM模块之间通信的可靠性,并且在FPGA内部实现上百兆时钟的逻辑处理和并行多通道控实现高速多通道同步串行通信,保证了综合航电设备内部各个LRM模块之间通信的实时性。

在中央核心控制LRM模块中,通用FPGA内部设计了串行通信管理状态机(分为接收状态机和发送状态机),并行地解析和处理串行通信线路上的数据,进行缓存后再通知CPU来接收数据,或者CPU接收到发送状态机的指令,集中处理要发送的数据放入到FPGA的发送缓存中,由发送状态机自行按照各个通道的串口通信状态独立控制发送。如图2和图3所示,FPGA完成同步串行通信通道的管理。这样由FPGA完成各个通道同步串行通信的任务,同时根据反馈式原理,保证串行通信线路上数据的有效性。这样就将中央核心控制LRM的CPU解放,不需要CPU参与串口通信寄存器的保护和恢复现场,以及与外部存储器通信所带来的庞大时间开销,由此来满足中央核心控制单元与能电源管理单元、高速I/O接口处理单元、视频信号处理单元、大容量数据存储单元和网络交换控制单元的高速同步串行总线的通信时序要求。

综合航电设备上电后,中央核心控制LRM模块同时给各个LRM模块发出“握手信号”,中央核心控制LRM给各个LRM模块发出同步串行通信数据帧。中央核心控制LRM模块的FPGA集成一个微控制器(硬核),仅需要通知中央核心控制LRM的CPU,通过CPU的局部总线接口(LocalBus)将所有的发送各个LRM模块的数据放到一个数据缓存中,再发送一个启动发送指令,FPGA内部的状态机自行将数据缓存中的数据进行发送数据处理,再向各个通道的FIFO中放入待发送数据,启动串并转换协议向同步串行通道发送数据,同时反馈电路接收到各个通道的LVDS驱动器发送数据后,FPGA将反馈数据与FIFO数据进行比对,分为以下两种情况:

(1) 如果正确,记录发送状态,清除FIFO中待发送数据,等待下一帧待发送数据;

(2) 如果不正确,启动应急处理,给接收端发送“数据丢弃”帧,同时再从FIFO中发送数据,再通过反馈电路进行比对,如再错,记录发送状态,发出告警同步给CPU,放弃该通道的同步串行数据发送。

中央核心控制LRM模块的同步串行通信接收端也是FPGA+LVDS驱动器实现的。FPGA中的状态机自行解析各个通道同步串行数据,同时启动反馈电路采集各个通道的数据,FPGA状态机进行比对,分为以下两种情况:

(1) 如果正确,将有效的帧数据存放到FPGA内部的数据缓存中,并通知FPGA中集成的微控制器读取数据放入CPU的数据缓存中,记录接收状态;

(2) 如果不正确,该通道的发送端发送“接收错误”帧,记录接收状态,要求发送端再次发送,同时清除该通道反馈电路中的数据,等待再次发送的数据,如果再次接收比对正确,修改接收状态,再不正确,记录接收状态,发出告警同步给CPU,放弃该通道的同步串行数据接收。

根据以上的工作原理,设计了发送和接收的FPGA逻辑控制流程,流程图如图5所示。

2 设计验证

在综合化航电设备中,启动中央核心控制LRM模块分别与其他5个LRM模块同时进行数据发送和数据接收,要求每50 ms周期内,需完成中央核心控制模块分别向各5个LRM模块连续发送320 B数据,并完成数据组包和数据发送。同时,要求每30 ms周期内需完成中央核心控制LRM分别接收5个LRM模块的数据发送来的128 B数据,并完成数据解析和数据处理。通过连续发送和接收测试,监测是否会存在丢包现象。

通过20 000帧数据为周期,持续近2 h的测试工作,未发现丢包及异常现象。在监测过程中,实测的传输速率达到12.25 Mb/s。通过人为在传输线路上注入故障,中央核心控制模块和各个LRM模块能够准确检测到传输通道故障。

3 结 语

该方案设计的实现大大减轻了CPU的处理负荷,有效利用超大规模的FPGA内部资源实现高速可靠的同步串口通信技术,不易受外界干扰,推广到目前综合化航电设备的高速数据传送系统中。

参考文献

[1] 张磊,张小林,杨百平.无人机机载设备串行通信测试系统的设计[J].计算机测量与控制,2010,18(1):26?28.

[2] 郭先树.利用TL16C550B实现DSP与PC机的异步串行通信[J].华东交通大学学报,2003,20(2):63?66.

[3] 任晓东.CPLD/FPGA高级应用开发指南[M].北京:电子工业出版社,2003.

[4] 杨小强,黄智刚,张军,等.基于空地数据链的飞机状态监控系统的实现[J].电讯技术,2003,43(1):68?72.

[5] 冯春阳,张遂南.三线制同步串行通信控制器接口设计[J].现代电子技术,2009,32(19):80?82.

[6] 杜晓斌,陈兴文.FPGA和单片机串行通信接口的实现[J].微计算机信息,2004(9):71?72.

[7] 魏祎,许永辉.基于PXI总线的航空串行总线专用通讯模块研制[J].现代电子技术,2014,37(17):86?89.

[8] 邱伟.机载电子设备间高速数据传输研究[J].现代电子技术,2014,37(12):30?31.