基于CPCI总线的FPGA+DSP架构通用视频图像处理系统的设计

2015-05-10于洪松韩广良孙海江李桂菊武治国李赓飞

于洪松,韩广良,孙海江,李桂菊,武治国,李赓飞

(1.中国科学院 长春光学精密机械与物理研究所,吉林 长春 130033;2.中国科学院大学,北京 100049)

1 引 言

高速视频图像处理具有数据量大和实时性高的特点。由于高速视频应用现场监测的环境条件复杂多变,因此经常需要进行系统的软硬件升级,这导致了高速视频图像处理系统具有复杂性高、设计难度大、设计周期长等特点[1-2]。可编程通用系统的优点在于不需要对硬件进行频繁改动,只需要对配置文件进行重新烧写、对上位机进行升级及少量的改动,而这些工作是可以在不影响现场使用的条件下就进行的,因此可以大大降低系统设计时间及成本[3]。

FPGA+DSP架构在图像处理系统中得到了广泛的应用,FPGA的并行处理及可编程的特性使得硬件能获得很高的实时性,而DSP高效的乘加结构及超高的运算性能又特别适合进行图像处理的算法实现,这使得这种架构尤其适用于实时图像处理[4-9]。

Compact-PCI总线(以下简称CPCI总线)是一种成熟的计算机总线,其支持热插拔及完善的标准定义使得CPCI架构具有很高的可靠性,再加上其兼容性高、集成度高且便于扩展,使得CPCI架构很适合高速视频信号处理系统的控制相关处理[2,10]。

本文介绍了基于CPCI总线的FPGA+DSP架构的通用高速视频信号处理系统的设计及应用。文中采用Xilinx公司专门用于高性能逻辑设计的 Virtex-IV 系列 FPGA XC5VLX50T、TI公司高性能定点数字信号处理器TMS320C6455及PLX公司的总线控制器芯片PCI9656设计了基于CPCI总线的FPGA+DSP架构的通用视频图像处理系统。实验表明,本文设计的系统具有实时性高、稳定性高、集成度高、扩展性好等特点。

2 通用视频图像处理系统主要模块的设计

2.1 视频图像处理系统概况

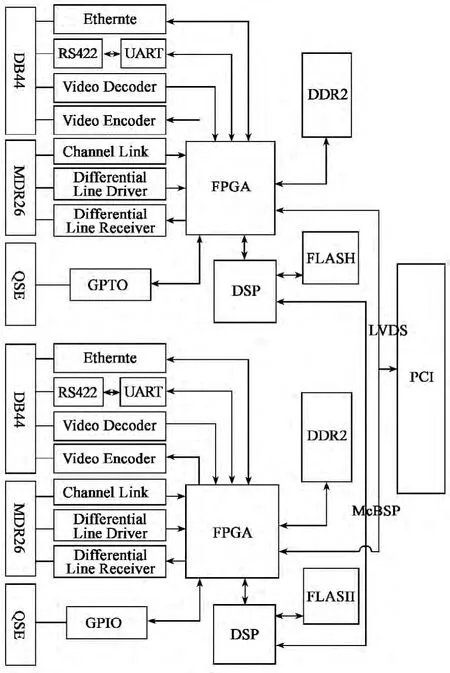

图1为通用视频图像处理系统的原理框图。系统包含两个几乎完全相同的部分。每一部分都有图像采集、数据处理、视频显示及PCI控制等模块,同时配备了丰富的扩展接口,包括串口、千兆以太网接口、扩展GPIO接口等。DSP之间通过McBSP相连接进行通信,FPGA之间通过LVDS相连接进行通信。

图1 通用视频图像处理系统的硬件框图Fig.1 Block diagram of general-purpose video image process system

DSP挂接4MB的Flash-ROM,可扩展为8MB,用于存储程序代码。FPGA采用PROM方式进行加载,断电重启后程序不会丢失,并配有状态指示灯便于观察PROM加载及FPGA的工作状态。

FPGA采用Camera Link的Base模式与相机连接,用于采集数字图像;FPGA挂接一片ADV7188视频解码芯片,可采集模拟图像,数字化后输出给FPGA进行处理。FPGA挂接一片1 GByte的DDR2SODIMM内存条,时钟速度可达200MHz,访问宽度64bit,用于存储图像数据。FPGA挂接一片ADV7176视频编码器,用于输出模拟复合视频信号到监视器。FPGA挂接两路UART,一路用于RS422串口,另一路用于Camera Link的命令串口,用于与相机通信,进行相机工作模式的配置及基本控制信号的收发。FPGA挂接一个千兆以太网接口,用于与上位机通讯。QSE接口用于与视频显示增强板进行高速连接。

2.2 主要器件的选型

考虑到系统的通用性,首先确定负责主要算法的DSP器件的选择,之后根据DSP选择协处理器FPGA,最后选择存储器件。

实时视频处理要求DSP器件必须具有主频高、内部存取速率高、外部接口速率高等特点,为此选用美国 Texas Instruments公司出品的TMS320C6455(以下简称6455)。6455为高性能定点处理器,最高工作主频高达1.2GHz。片内高速存储空间采用改进的哈佛结构,分为两级Cache。具有多达64个独立通道的EDMA数据传输控制器。与片外的接口包括高速64bits宽度的EMIFA及32bits宽度的DDR2扩展存储器接口,最高吞吐能达到1 064MB/s。同时还提供两路高速的缓冲串口 McBSP,以供通信使用[11]。

协处理器FPGA负责原始数据流的控制、转换及接口的适配,由于实时视频处理具有数据量大、数据速率高、运算速度快的特点,因此FPGA应具有时钟模块便于管理、存储器容量大、接口速率高及具有足够的硬件加速器等特点。为此采用美国Xilinx公司专用于高性能逻辑应用的Virtex-5系列FPGA LX50T。Virtex-5系列 FPGA具有灵活的时钟管理器,内嵌6个时钟模块。内部具有高达16.4Mbits的增强型存储器Block RAM,并具有内置FIFO控制逻辑。最新的ChipSync技术简化了针对高带宽存储器和其它源同步接口板的设计。内置的时钟主频高达550 MHz的DSP48Eslice具有能够提高DSP性能的乘累加器结构,加强了硬件加速的技术[12]。

由于6455具有预置的DDR2存储器接口,而Xilinx公司对于Virtex-5系列FPGA也提供了针对DDR2的参考设计,又兼高速视频处理所需的存储空间很大,故选用 micron公司-MT8HTF12864HZ-667H1型号的DDR2 SDRAM作为本系统的存储器。MT8HTF12864 HZ-667H1总容量高达1 024Mbytes,位宽64 bit,数据带宽可达5.3GB/s[13]。

2.3 图像采集模块的设计

为了增加本处理系统的通用性,支持模拟输入图像和数字输入图像两种采集方式。

针对数字输入的图像,采用Camera Link进行图像的采集。Camera Link总线标准专门为数字相机制定,针对相机图像数据及相机控制信号的定义、相机的工作模式、数据位的分配及连接件标准做了详细的规定,由于其具有更少的连接线、更高的传输速率以及更小的电磁干扰的特性而成为市面上主流的相机接口。

图2为本系统针对数字输入图像的采集模块的硬件框图。

图2 数字输入图像采集模块的硬件连接Fig.2 Hardware interconnection of image acquisition module for digital input

本设计采用Camera Link的base模式,采集命令到达后,状态机启动,数字相机输出的LVDS差分数据经过处理芯片转换成28位并行数据,其中包括24位视频数据,帧同步信号、行同步信号、数据同步信号以及一个备用信号[14]。

针对模拟输入的图像,采用ADI公司的ADV7188视频解码芯片进行图像采集。

ADV7188具有12路模拟输入通道,4路内部集成54MHz、12-bit ADCs,支持包括 NTSC,PAL及SECAM等多种常用色彩制式,支持I2C协议对芯片进行配置,具有色度瞬态增强及数字噪声衰减特性[15]。

图3为本系统针对模拟输入图像的采集模块的硬件连接框图。

在摄像头采集到视频后,在FPGA中设置芯片的寄存器,在DSP中通过I2C协议对芯片进行配置,对模拟输入图像进行A/D转换。采用外部27MHz晶振作为工作时钟。

图3 模拟输入图像采集模块的硬件连接Fig.3 Hardware interconnection of image acquisition module for analog input

2.4 数据处理模块的设计

数据处理模块主要涉及算法实现及数据存取的相关操作。

算法实现的核心器件为FPGA及DSP。DSP通过AWE#和AOE#控制读写使能,通过EMIF方式将20位地址线和32位数据线连接到FPGA上进行数据交换及相应的算法处理。DSP是系统的核心处理器,负责算法的调度,接收来自FPGA的数据后进行相应算法的实现,得到的结果发送给上位机以供监测或者存入DDR2中进行存储。FPGA作为协处理器,负责数据流的控制,同时完成对视频编解码器等设备的复位及寄存器的配置;对采集到的原始图像进行字节截断及一些时序控制操作,以配合DSP的运算及控制操作。

数据存取涉及到FPGA与DSP对DDR2的操作。FPGA由于可以建立具有高速缓存的DPRAM而能够完成对DDR2的直接操作。FPGA对DDR2SDRAM操作的程序采用Xilinx公司的针对DDR2SDRAM的IP核MIG(Memory Interface Generator)进行配置并自动生成[16]。

视频数据通过FPGA入口处的DPRAM缓冲进入FPGA后,在FPGA中进行原始视频数据到字节数据的转换,写入FPGA出口处的DPRAM中。当检测到写入一行图像后,启动写DDR2操作,将该行图像数据存入DDR2,写满一帧数据后,地址自动指向下一帧数据存储空间的首地址。

DSP与CPCI通过FPGA以总线占用的方式对DDR2进行间接操作,以中断的方式相互通信。DSP操作DDR2的流程图如图4所示。

图4 DSP操作DDR2的流程图Fig.4 Flowchart of DSP accessing DDR2

具体操作步骤如下:

(1)查询DDR2被占用的标识地址0x42000寄存器是否为1;

(2)若为1,则DDR2正在被占用,跳回步骤(1)继续查询;若为0,则主动占用,执行步骤(3)进行主动占用;

(3)向标识地址寄存器0x42000写1完成对DDR2的占用;

(4)完成对DDR2的占用后,若需对DDR2进行读操作,则转向步骤(5)初始化读操作;若需对DDR2进行写操作,则转向步骤9)初始化写操作;

(5)向地址0x42002写入高16位地址;

(6)向地址0x41001写1发起读DDR2命令;(7)从地址0x40000~0x40fff取数;

(8)若需要继续操作DDR2,转向步骤(4)进行对DDR2操作的流程判断;若操作已完成,则向0x42000地址写0释放对DDR2的占用;

(9)向地址0x42001写入高16位地址;

(10)向地址0x40000~0x40fff写入4K×32bit的数据;

(11)若需继续操作 DDR2,则转向步骤(4)进行对DDR2操作的流程判断;若是操作已完成,则向0x42000地址写0释放对DDR2的占用。

2.5 视频显示模块的设计

在对视频数据进行处理后,需要对视频数据进行准确的回放显示。

采用ADI公司具有高性能视频编码功能的ADV7176芯片,在FPGA中设置芯片的寄存器,在DSP中通过I2C总线协议对芯片进行配置,将数字信号转换成PAL制式电视信号,通过常用的模拟视频监视器即可对输出信号进行监测。

ADV7176具有4路10bits的高性能模拟输出通道,支持ITU-R BT601/656YCrCb到PAL/NTSC等多种制式,高达80dB的视频信噪比也使得视频的编码能够应对各种复杂现场的需求[17]。

2.6 PCI控制模块的设计

传统的基于FPGA+DSP架构的视频图像处理系统与上位机的人机交互一般通过通信口实现,难以做到对系统的灵活控制。本系统上位机通过CPCI总线控制视频处理单元,因此可以进行一些对图像算法的复杂控制及对整个系统的调控,增强了视频图像处理系统的通用性。以红外可见双通道的目标跟踪系统为例,上位机程序可以选择脱靶量来源、跟踪通道、跟踪方式、边沿选取模式、阈值的人工调整及跟踪目标的数量等。

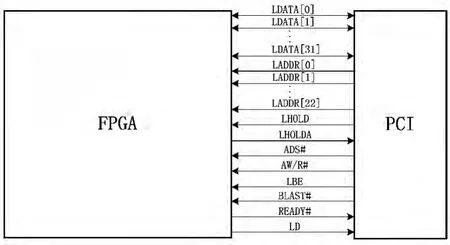

针对PCI接口的设计一般有两种方案,一种是在FPGA内部直接进行逻辑设计,但是这种方案需要耗费的资源很多,而且调试周期长,难度大;另一种方案是采用总线控制芯片来简化设计,为此选用PLX公司生产的为高速PCI总线应用设计的通用I/O芯片PCI9656。

PCI9656具有面向三种处理器局部总线类型的连 接 模 式:M 模 式——适 配 Motorola MPC850、MPC860以及IBM PowerPC 801系列的处理器;C模式——适配Intel i960、DSPs、定制的ASICs、FPGAs以及其他的处理器;J模式——适配Intel i960、IBM PowerPC 401、DSPs以及一些其他处理器。基于通用性的考虑,设计中采用了适配大多数处理器的C模式。

PCI9656具有3种数据传输模式:直接主控模式、直接从动模式以及DMA模式。本系统中,大数据量连续传输采用DMA模式,其他参数的传输采用直接主控模式以及从动模式[18]。

PCI9656的配置需要3部分:首先由与PCI9656对应的EEPROM芯片对其初始化参数进行设置,其次在FPGA程序中对PCI9656进行初始化配置,最后在上位机进行其他的设置。图5为PCI9656芯片与FPGA的连线图。PCI9656芯片的驱动程序可以从PLX公司提供的配套开发包中获取,开发包中还提供了与上位机进行通信的动态链接库文件,内有丰富的函数可供调用,通过VC++环境即可编写出相应的上位机控制界面。限于篇幅,在此不再具体介绍上位机程序的工作流程。

图5 PCI9656芯片与FPGA的硬件连接Fig.5 Hardware interconnection between PCI9656 and FPGA

3 系统测试

为验证本系统的有效性,搭建实物平台,进行实验验证。平台实物图如图6所示。

图6 实验平台Fig.6 Platform of experiment

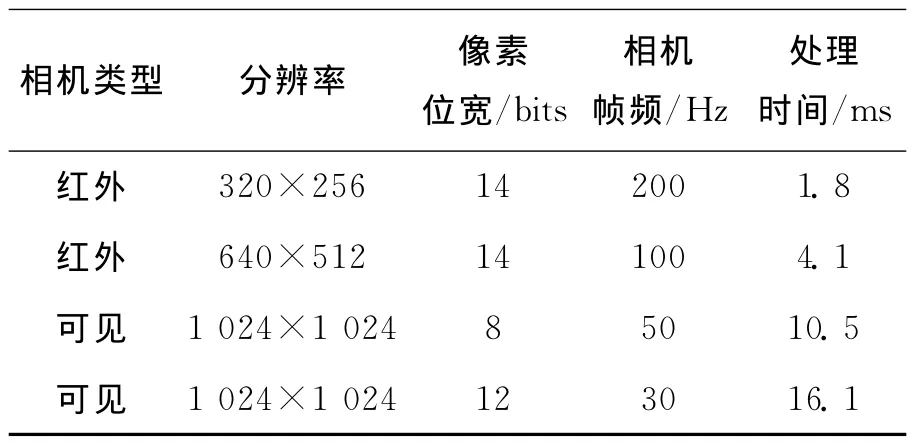

分别采用4种工程常用的相机进行本系统的实时性验证实验,两台红外相机的分辨率分别为320×256及640×512,像素位宽均为14bits,两台可见相机的分辨率均为1 024×1 024,像素位宽分别为8bits及12bits。分别采用相同的目标跟踪算法,在DSP内编写了上位机控制程序进行软硬件实验。

图7 本系统的目标跟踪效果图Fig.7 Result of the system aiming at target tracking

实验以月球上亮度高的区域为跟踪目标,采用图像预处理、直方图自适应阈值及重心跟踪方式,进行全视场多目标捕获。上位机通过cPCI总线控制选择跟踪目标,锁定目标后跟踪稳定,实现了实时跟踪,效果良好。跟踪的效果图如图7所示。

表1列出分别采用4种相机实现全视场捕获所用的时间及相关的相机信息。

表1 针对不同相机的实验结果Fig.1 Results of the system at different cameras

4 结 论

设计并实现了基于CPCI总线的FPGA+DSP架构通用视频图像处理系统,通过PCI总线与传统FPGA+DSP架构的结合,扩展了图像处理系统的应用范围。实验表明,本文设计的视频图像处理系统在实际应用中具有实时性高、集成度高、交互性好、扩展性好等特点,已被应用于某目标跟踪系统中,满足了实际应用的需求。

[1] 樊博,王延杰,孙宏海,等 .FPGA实现高速实时多端口图像处理系统的研究[J].液晶与显示,2013,28(4):620-625.Fan B,Wang Y J,Sun H H,et al.High speed real-time multiport image processing system realized on FPGA [J].Chinese Journal of Liquid Crystals and Display,2013,28(4):620-625.(in Chinese)

[2] 叶有时,赵保军,唐林波,等.多目标实时跟踪可编程片上系统的软件优化[J].光学精密工程,2011,19(3):681-689.Ye Y S,Zhao B J,Tang L B,et al.Software optimization of multi-target real-time tracking SOPC system[J].Optics and Precision Engineering,2011,19(3):681-689.(in Chinese)

[3] 王本明,赵前晟,丁海锋,等 .基于CPCI总线的通用FPGA信号处理板的设计[J].电子科技,2009,22(10):25-28.Wang B M,Zhao Q S,Ding H F,et al.Design of general FPGA signal processing board based on CPCI bus[J].Electronic Science and Technology,2009,22(10):25-28.(in Chinese)

[4] 苏宛新,程灵燕,程飞燕 .基于DSP+FPGA的实时视频信处理系统设计[J].液晶与显示,2010,25(1):145-148.Su W X,Cheng L Y,Cheng F Y.Design ofreal-time video signal processing system based on DSP+ FPGA[J].Chinese Journal of Liquid Crystals and Display,2010,25(1):1145-148.(in Chinese)

[5] 张向阳,程勇策,曲思潼 .基于DSP+FPGA的Camera Link接口相机的图像处理平台设计[J].电视技术,2013,37(15):215-219.Zhang X Y,Cheng Y C,Qu S T.Camera withcamera link interface image process platform based on DSP and FPGA[J].Video Engineering,2013,37(15).(in Chinese)

[6] 王静轩,尹传历 .基于DSP和FPGA的嵌入式实时图像增强系统[J].液晶与显示,2013,28(3):459-463.Wang J X,Yin C L.Embedded color image enhancement system based on DSP and FPGA[J].Chinese Journal of Liquid Crystals and Display,2013,28(3):459-463.(in Chinese)

[7] 朱明,鲁剑锋 .基于DSP+FPGA结构图像处理系统设计与实现[J].计算机测量与控制,2004,12(9):866-869.Zhu M,Lu J F.Design andimplementation of digital image processing system based on DSP + FPGA architecture[J].Computer Measurement and Control,2004,12(9):866-869.(in Chinese)

[8] 高杨,刘荣科,胡伟 .基于FPGA+DSP的高清视频图像系统设计与实现[J].电子测量技术,2011,34(1):69-73.Gao Y,Liu R K,Hu W.Design and implementation of high definition video image system based on FPGA+ DSP[J].Electronic Measurement and Technology,2011,34(1):69-73.(in Chinese)

[9] 李易难,牛燕雄,杨露 .基于DSP+FPGA视频图像采集处理系统的设计[J].电子测量技术,2014,37(1):58-61.Li Y N,Niu Y X,Yang L.Design ofvideo image sampling and processing system based on DSP and FPGA[J].Electronic Measurement and Technology,2014,37(1):58-61.(in Chinese)

[10] PICMG.PICMG 2.0compact PCI specification[R].PCI Industrial Computers Manufactures Group,1999.

[11] Texas Instruments.TMS320C6xoptimizing C compiler user guide[R].Texas Instruments Incorporated,1999.

[12] Xilinx Incorporated.Virtex-5family overview[R].Xilinx Incorporated,2009.

[13] Micron Technology.Datasheet of MT8HTF3264HY-667[R].Micron Technology,2004.

[14] AIA.Specifications of the camera link interface standard for digital cameras and frame grabbers[R].2004.

[15] Analog Devices.Datasheet of ADV7188[R].Analog Devices,2007.

[16] Xilinx.Interfacing micron DDR2memory modules to Xilinx Virtex5FPGAs:A step-by-step guide[R].Xilinx,2008.

[17] Analog Devices.Datasheet of ADV7175A/7176A[R].Analog Devices,2000.

[18] PLX Technology.PCI 9656BA data book[R].PLX Technology,2003.