基于PowerPC的主动雷达信号处理软件的设计与实现

2015-02-22王亚莉童卫勇吕卫祥姜小祥

王亚莉,童卫勇,吕卫祥,姜小祥

(1.91404部队,河北 秦皇岛 066001;2.中国船舶重工集团公司第七二四研究所,南京211153)

基于PowerPC的主动雷达信号处理软件的设计与实现

王亚莉1,童卫勇2,吕卫祥2,姜小祥2

(1.91404部队,河北 秦皇岛 066001;2.中国船舶重工集团公司第七二四研究所,南京211153)

摘要:介绍了PowerPC处理器的主要特点,设计并实现了基于PowerPC平台的主动雷达信号处理算法软件。通过引入局部性原理对PowerPC的存储器山分析,改善了软件的时间和空间局部性,优化了软件的性能,提高了软件运行的实时性。

关键词:雷达;信号处理;PowerPC8640D;局部性原理;存储器山

0引言

近年来,随着电子技术迅猛发展,各种高性能器件如DSP、FPGA、CPU等的不断涌现和更新换代,使得雷达信号处理从专用硬件的开发转向基于通用平台的软件开发。现代雷达的发展需要对高速海量的数据进行实时的传输和处理,而串行RapidIO(SRIO)是当前主流的数据传输方式。PowerPC处理器很好地提供了对SRIO的支持,同时其多核机制可以实现海量数据的并行快速处理。另一方面,VxWorks是应用最为广泛和可靠的实时操作系统。因此PowerPC处理器和VxWorks操作系统的搭配为雷达信号处理提供了很好的软件化处理平台。

本文将基于PowerPC8640D处理器设计实现主动雷达的信号处理算法,并就8640D的存储器山模型分析对算法软件进行优化改进,从而实现对雷达回波信号的实时处理。

1PowerPC处理器的特点

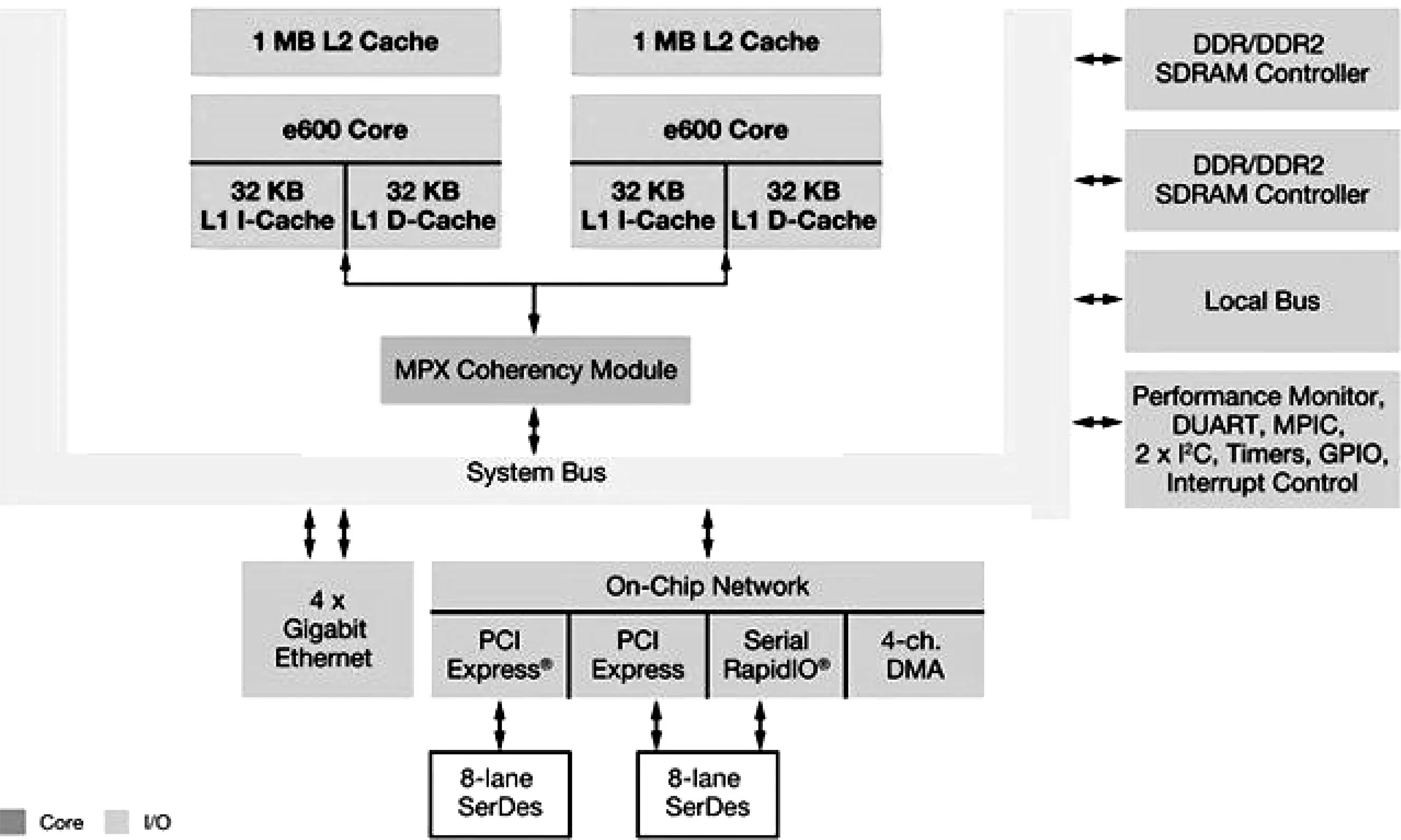

1.1 PowerPC8640D处理器简介

FreeScale公司研发的PowerPC8640D/8641D处理器是目前最为先进的处理器,其内部集成两个e600内核。每个内核的工作主频最高可达1.5 GHz。内核集成两个32 KB一级缓存和一个1 MB的二级缓存。另外,e600内核还具有强大运算能力的AltiVec矢量处理引擎。e600通过MPX总线与系统总线进行通信,其中高速千兆网接口、高速SerDes接口提供了对PCI-E和SRIO的访问支持,以获取高速的数据传输能力、集成的双内存控制器可实现对内存的低延迟、高带宽访问等[1-2]。PowerPC8640D处理器内核组成框图如图1所示。

图1 PowerPC8640D处理器内核组成框图

作为嵌入式处理器的典型代表,PowerPC在雷达信号处理领域不仅提供了比Intel、AMD系列处理器更低的功耗以及对SRIO高速串行接口更好的支持,而且在算法编程方面给予了DSP和FPGA所不具有的灵活性,从而在节约了研发成本的同时缩短了研发周期、降低了软件升级维护难度。此外,PowerPC处理器有着对实时操作系统VxWorks的强大兼容性。因此,在雷达这种强实时、高速数据率的系统中,PowerPC处理器具有更好的适应性和应用前景。

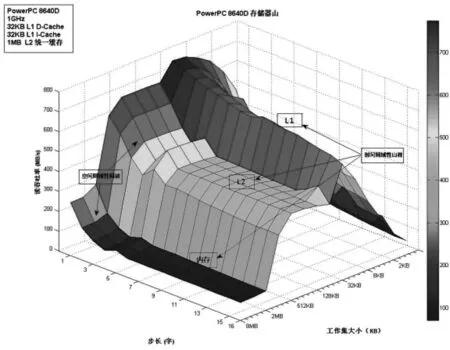

1.2 PowerPC8640D存储器山

一个高性能的程序应该具有良好的局部性。它倾向于引用邻近于其最近引用过的数据项,或者最近引用过的数据项本身。这种倾向性被称为局部性原理[3]。局部性原理主要有两种不同的形式:时间局部性和空间局部性。时间局部性是指在一定的时间内重复访问同一个地址的次数越多程序的时间局部性越好。空间局部性表现为如果程序两次访问的地址越接近,则程序的空间局部性越好。局部性原理对硬件和软件系统的设计和性能有着极大的影响。

计算机的存储器系统通常设计成一个存储器层次结构,从最高层的寄存器到高速缓存再到内存以及最底层的硬盘。各层次存储器的容量越来越大,访问速度越来越慢,成本越来越低。存储器层次结构的运行策略就是尽量让当前被频繁访问的存储区和其临近元素的内容驻留在较高层存储器,而把不常访问的存储区的内容置换到较低层存储器。因此,一个具有良好的局部性的程序要尽可能地适应存储器层次结构,也就是尽可能地访问高层的存储器,享受到最高的访问速率,从而提高程序运行效率。

笔者通过编写一个测试分析程序来研究存储器层次结构对程序的运行效率的影响。测试程序以不同的步长扫描固定长度数组中的不同大小元素集合即工作集,从而测试数据的吞吐率,最后采用K次最优测量方法得到最优测试结果。测试函数中数据的大小和步长控制产生读序列的局部性程度。数据越小,得到的工作集越小,时间局部性越好。步长的值越小,空间局部性越好。以不同的时间局部性(工作集大小)和空间局部性(访问步长)对存储器进行访问,就能得到存储器系统在不同的局部性下的性能(即访问速率),从而得到一个读带宽的时间局部性和空间局部性的二维函数,即图2所示PowerPC8640D的存储器山模型。

图2 PowerPC8640D存储器山模型

存储器山以工作集大小的变量为x轴,访问步长的变量为y轴,存储器访问速率为z轴。它看起来像一座有着山峰、山脊和山坡的小山,垂直于工作集轴的是3条山脊,分别对应于工作集完全在L1高速缓存、L2高速缓存和主存内的时间局部性区域。重点观察L2和主存山脊。在L2和主存山脊上随着步长的增加有一个空间局部性的斜坡,此时意味着程序空间局部性的下降。显然,尽可能地让工作集位于高速缓存中,程序的运行速度比工作集位于主存中优势明显。然而,当工作集太大不能全部工作在高速缓存时,主存山脊的最高点也比它的最低点高了将近3倍。因此,不难发现,当程序的时间局部性很差时,利用好空间局部性仍然可以补救时间局部性带来的性能损失。

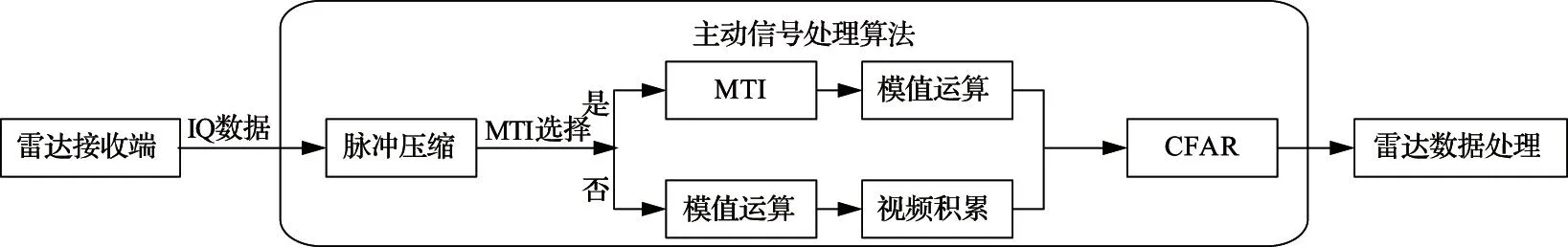

2信号处理软件的实现

信号处理软件运行于一个PowerPC处理器,通过RapidIO协议接收雷达数据,信号形式为每个脉组脉冲数为8个、重复周期为1000 μs的I、Q正交数据。算法流程如图3所示。

图3 主动信号处理算法流程图

(1) 脉冲压缩

脉压主要采用频域卷积法,将脉压系数和I、Q数据进行FFT后再IFFT实现。

(2) MTI

由于一个脉组含8个脉冲组成,因此采用多阶FIR高通滤波器来实现MTI,在设计好高通滤波器后,将脉组内主触发的I、Q数据与滤波器参数数组复数值进行乘累加运算即可完成动目标处理;

(3) 模值运算

为了计算雷达回波的幅度值需要对I、Q数据进行线性检波的模值运算,即求得I、Q信号的平方和后再进行开方运算。

(4) 视频积累

当不选择MTI处理时,模值运算后对脉组内脉冲求和后对积累系数做除法得到的商即为视频积累的结果。

(5) CFAR

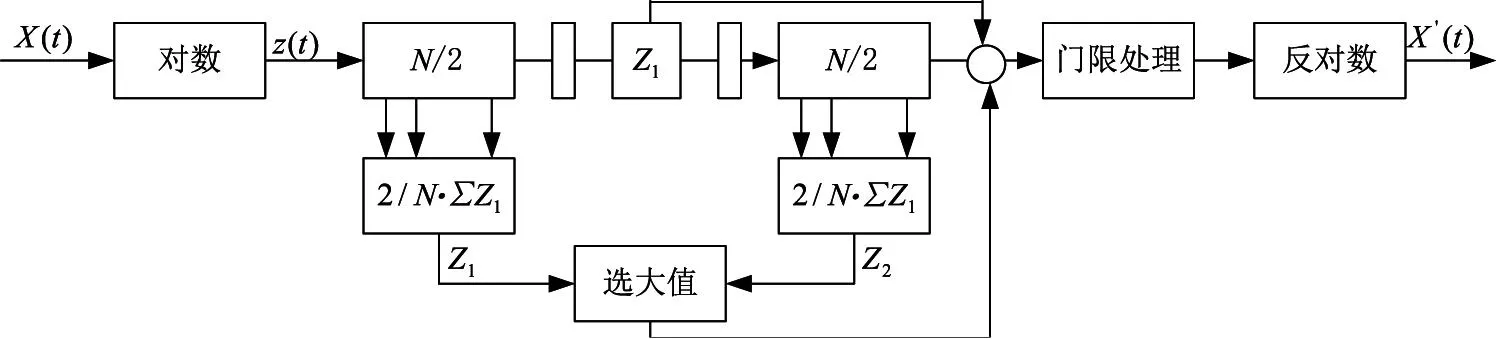

常用的CFAR算法是两侧单元平均选大法恒虚警GOCA-CFAR,即分别计算主触发保护单元左、后两侧的快门限和,再将两侧快门限和选大的结果取平均后与CFAR系数相乘,其结果与输入脉冲的对应距离单元的模值比较,若大于输入脉冲值则输出0,反之输出值为脉冲当前距离单元值。

雷达数据以脉组(一个脉组共8*1000=8000 μs)形式传输。当算法选择MTI处理时,此时不需要视频积累。经耗时测试,平均每个脉组信号处理耗时3880 μs(<8000 μs),满足系统实时性要求;而不选择动目标处理时则需要视频积累,此时平均每个脉组处理耗时6010 μs(<8000 μs),同样满足系统实时性要求。考虑到功能升级的需要,有必要对软件进行改进和优化。

3软件的优化

根据Amadahl定律,要提高整个算法的运行速度,必须首先提高对运行速度影响最大的那部分程序运算速度[3]。由于本算法中MTI处理和视频积累作为可选模块,而CFAR则作为必选处理,同时经测试CFAR执行耗时668 μs,算法耗时占比较大,因此有着较大的优化空间。本软件中CFAR算法采用GOCA-CFAR[4],其基本原理如图4所示。

图4 两侧单元平均选大恒虚警率原理框图

算法设定平均单元数为16个,保护单元数为左右各1个,平均单元和的计算可采用两种方法:其一使用传统方法逐个相加,其二使用滑窗相减技术。使用传统方法求和,此方法简单直观,但存在着冗余计算,其时间复杂度为O(mn),其中n为距离单元个数,m为相加的平均单元数;若采用滑窗相减方法,第i个单元zi的平均单元距离和s0,紧邻后续单元zi+1的前后距离单元和可以用结果s0加上第i+16+1的距离单元值减去第i-16的距离单元值,后续单元的和以此类推。

相比传统方法,滑窗相减法减少了计算量,其时间复杂度为O(n),运行效率提高了m倍。但是,采用滑窗相减法需要一直计算左右单元和,程序的时间局部性,空间局部性并不理想,缓存的命中率比较低,仔细观察不难发现,第i个单元的右侧和变成了其滑过16+1个单元后的第i+16+1个单元的左侧和。因此,可以对滑窗相减法进行改进,从第1个单元开始,程序将滑窗法计算过右侧的和存储到一个平均和数组中,当计算到第i+16+1个单元的左侧平均单元和即是平均和数组中的第1个值,而第i+16+1个单元右侧的和则继续用滑窗相减计算,并存到平均和数组中,供后面的计算左侧平均单元和时直接调用。

相比滑窗相减法,改进后的算法通过对平均和数组的调用即可完成相应左侧平均单元和的赋值,从而算法只需顺序访问右侧的平均单元即可完成右侧和计算,并存入平均和数组中作为后续的左侧平均和使用。显然,改进后滑窗相减法的工作集大小减半,不需频繁访问左右两侧数据,提高了缓存命中率,其时间局部性和空间局部性都得到了明显的改善,运行效率又提高了将近一倍。通过测试,优化改进后的CFAR算法耗时158 μs,相比优化前提高了将近5倍,软件的性能得到了显著的提高。

4结束语

本文针对PowerPC处理器的主要特点,实现了一个基于PowerPC平台的主动雷达信号处理典型流程的算法软件设计,并对PowerPC8640D存储器山进行建模分析。通过对算法的优化,改善了程序运行的局部性,提高了软件运行的效率,从而为后续在PowerPC平台上进行实时信号处理算法的优化设计提供了新的思路。

参考文献:

[1]e600 PowerPC Core Reference Manual[Z].FreeScale Rev.0,2006.

[2]MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications[Z].FreeScale,2008.

[3]Randal E Bryant,David O’Hallaron.深入理解计算机系统[M].北京:中国电力出版社,2004.

[4]Merrill I Skolnik.雷达手册[M].北京:电子工业出版社,2010.

※※※※※※※※※※※※※※※※※※※※※※※※※

Design and implementation of signal processing software

based on PowerPC for active radar

WANG Ya-li1, TONG Wei-yong2, LU Wei-xiang2, JIANG Xiao-xiang2

(1.Unit 91404 of the PLA Navy, Qinhuangdao 066001, China;

2. No.724 Research Institute of CSIC, Nanjing 211153)

Abstract:The main characteristics of the PowerPC processor are introduced, and the signal processing algorithm software is designed and implemented based on the PowerPC platform for the active radar. The memory mountain of the PowerPC is analyzed by introducing the principle of locality, improving temporal and spatial locality and real-time operating capability of the software, and optimizing the software performance.

Keywords:radar; signal processing; PowerPC8640D; principle of locality; memory mountain

中图分类号:TN311.52

文献标志码:A

文章编号:1009-0401(2015)04-0064-04

作者简介:王亚莉(1973-),女,高级工程师,研究方向:雷达工程和雷达数据处理;童卫勇(1981-),男,工程师,硕士,研究方向:数据处理;吕卫祥(1975-),男,研究员,工程硕士,研究方向:雷达总体及信号处理;姜小祥(1984-),男,工程师,硕士,研究方向:雷达信号与数据处理。

收稿日期:2015-06-11;修回日期:2015-07-17