应用于SAR ADC的高能效电容阵列DAC*

2015-02-18胡云峰李斌吴朝晖

胡云峰 李斌 吴朝晖

(1.华南理工大学 电子与信息学院, 广东 广州 510640; 2.电子科技大学中山学院, 广东 中山 528402)

应用于SAR ADC的高能效电容阵列DAC*

胡云峰1,2李斌1†吴朝晖1

(1.华南理工大学 电子与信息学院, 广东 广州 510640; 2.电子科技大学中山学院, 广东 中山 528402)

摘要:电容阵列数模转换器(DAC)是逐次逼近型模数转换器(SAR ADC)的主要能耗来源之一.为降低电容阵列DAC的能耗,提出了一种高能效电容阵列DAC结构,该结构电容阵列中各电容单元通过开关依次连接.在前两次比较周期中,由于采用了顶板采样和电压移位技术,电容阵列DAC没有产生能耗;在之后的比较周期中,由于采用电荷共享和电压单调降低技术,电容阵列DAC产生了很少的能耗.仿真结果表明,相比于传统的电容阵列DAC结构,文中提出的高能效电容阵列DAC结构可降低99.22%的能耗,节省75%的面积.

关键词:逐次逼近寄存器;模数转换;电容阵列DAC;高能效

近年来,逐次逼近型模数转换器(SAR ADC)因其能耗低而广泛应用于植入式、便携式和穿戴式电子设备[1-8].SAR ADC由电容阵列DAC、比较器和逐次逼近开关控制器3部分组成,其中电容阵列DAC和比较器是SAR ADC能耗的主要来源[9].到目前为止,已有不少可减少电容阵列DAC能耗的结构[9-15],与传统的电容阵列DAC结构相比,电荷回收结构[9]、电荷共享结构[9]、电容分裂结构[9]、分裂结合结构[10]、单调结构[11]、共模电压结构[12]、三电平结构[13]、共模电压单调(VMS)结构[14]、混合电容(HCS)结构[15]的能耗分别降低了12.52%、24.99%、37.48%、74.96%、81.26%、87.52%、96.89%、97.66%和98.84%.为进一步降低电容阵列DAC的能耗,文中提出了一种高能效电容阵列DAC结构,并对该结构的能耗进行了分析.

1高能效电容阵列DAC结构

文中设计的8位差分SAR ADC的高能效电容阵列DAC结构如图1所示,该电容阵列DAC由同相电容阵列和反相电容阵列组成,同相电容阵列和反相电容阵列分别包含7个电容单元,从右到左编号依次为1-7,其中分别包含1、1、1、2、3、4、5个子电容,总电容值分别为C、C、2C、4C、8C、16C和32C,第2个电容单元至第7个电容单元之间依次通过开关连接.各电容单元的顶板通过开关依次连接到外部信号输入端和比较器输入端之间,底板通过开关选择连接共模电压Vcm或参考电压Vref或地.

2高能效电容阵列DAC工作流程

图2为N位高能效电容阵列DAC工作流程图,具体工作步骤如下.

图1 高能效电容阵列DAC结构图Fig.1 Architecture of energy-efficient capacitor array DAC

图2 N位高能效电容阵列DAC工作流程图Fig.2 Flowchart of N-bit energy-efficient capacitor array DAC

(1)

2)第1次比较.比较器对同相输入端和反相输入端的保持信号进行比较,输出第1次比较结果D[1].

3)第2次比较.根据第1次比较结果D[1],若D[1]=1,则反相电容阵列中所有电容单元的底板接入参考电压,比较器输入端信号为

(2)

若D[1]=0,则同相电容阵列中所有电容单元的底板接入参考电压,比较器输入端信号为

(3)

将电容阵列中所有电容单元的内部开关断开,比较器对同相输入端和反相输入端的信号大小进行比较,输出第2次比较结果D[2].

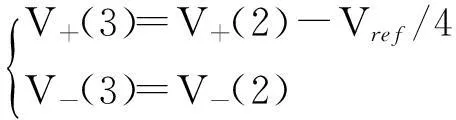

4)第3次比较.根据第1和第2次的比较结果,若D[1]D[2]=11,则同相电容阵列第2个电容单元的子电容的底板接入地,比较器输入端信号为

(4)

若D[1]D[2]=10,则反相电容阵列第2个电容单元的子电容的底板接入共模电压,比较器输入端信号为

(5)

若D[1]D[2]=01,则同相电容阵列第2个电容单元的子电容的底板接入共模电压,比较器输入端信号如式(4)所示.

若D[1]D[2]=00,则反相电容阵列第2个电容单元的子电容的底板接入地,比较器输入端信号如式(5)所示.

比较器对同相输入端和反相输入端的信号大小进行比较,输出第3次比较结果D[3].

5)第i次比较.根据第1、第2和第i-1次比较结果D[i-1],若D[1]D[2]=11且D[i-1]=1,则同相电容阵列第i-1个电容单元的第1个子电容的底板接入地,比较器输入端信号为

(6)

若D[1]D[2]=11且D[i-1]=0,则所有电容单元的第1个子电容的底板接入电压保持不变,比较器输入端信号为

(7)

若D[1]D[2]=10且D[i-1]=1,则所有电容单元的第1个子电容的底板接入电压保持不变,比较器输入端信号为

(8)

若D[1]D[2]=10且D[i-1]=0,则反相电容阵列第i-1个电容单元的第1个子电容的底板接入共模电压,比较器输入端信号调整为

(9)

若D[1]D[2]=01且D[i-1]=1,则同相电容阵列第i-1个电容单元的第1个子电容的底板接入共模电压,比较器输入端信号如式(6)所示.

若D[1]D[2]=01且D[i-1]=0,则所有电容单元的第1个子电容的底板接入电压保持不变,比较器输入端信号如式(7)所示.

若D[1]D[2]=00且D[i-1]=1,则所有电容单元的第1个子电容的底板接入电压保持不变,比较器输入端信号如式(8)所示.

若D[1]D[2]=00且D[i-1]=0,则反相电容阵列第i-1个电容单元的第1个子电容的底板接入地,比较器输入端信号如式(9)所示.

将同相电容阵列第i-1个电容单元和反相电容阵列第i-1个电容单元的内部开关闭合,比较器对同相输入端和反相输入端的信号大小进行比较,输出第i次比较结果D[i],其中4≤i≤N.

6)i=i+1,返回步骤5),直到输出第N次比较结果D[N]为止.

图3给出了两种4位电容阵列DAC输出码为1101时DAC的输出电压变化情况.如图所示,相比于传统结构,高能效电容阵列DAC每次只有一个电容阵列输出电压调整.

图3 电容阵列DAC的输出电压波形Fig.3 Output voltage waveforms of capacitor array DAC

3高能效电容阵列DAC的能耗分析

4位高能效电容阵列DAC的转换过程如图4所示,在进行第1次比较时,由于采用顶板采样技术[11],输入信号直接连接至比较器输入端,因此不需要对比较器输入端电压进行调整,电容阵列没有产生能耗, E1=0.

在进行第2次比较时,由于采用电压移位技术[13],电压较小的比较器输入端连接的电容阵列上所有电容底板的连接电压都切换到参考电压Vref,因此,电压较小的输入端电压提高Vref/2,但没有发生电容充、放电情况,故第2次比较电容阵列没有产生能耗, E2=0.相比于传统结构,高能效电容阵列DAC节省了两个最高位比较能耗.

在进行第3次比较时,由于采用电压单调降低技术[11],电压较大的比较器输入端连接的电容阵列第2个电容单元的电容底板的连接电压降低Vref/2,此时只有第1、第2个电容单元的电容参与转换,故能耗相比传统结构显著降低.

图4 4位高能效电容阵列DAC的转换过程图Fig.4 Switching procedure of 4-bit energy-efficient capacitor array DAC

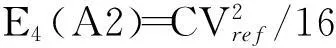

对于A转换,比较器反相输入端电压没有发生变化,反向电容阵列电容没有产生能耗,同相电容阵列第2个电容单元接地,没有产生能耗,因此只有同相电容阵列的第1个电容单元产生了能耗,参考文献[9]的能耗计算方法:电容能耗可由电容两端电压差的变化来表示,A的转换能耗为

E3(A)=CVcm{[Vcm-V+(3)]-[Vcm-V+(2)]}

(10)

由式(4)有V+(3)-V+(2)=-Vref/4,式(10)可整理为

(11)

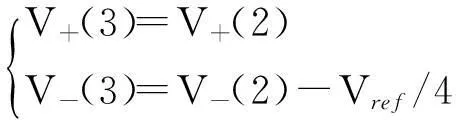

在进行第4次比较时,第3个电容单元的电容底板接入电压调整有两种情况:接入电压保持不变、接入电压降低Vref/2,分别属于电荷共享技术[10]、电压单调降低技术[11],这两种技术都能降低电容阵列DAC的能耗.

对于A1转换,由于电压调整采用电压单调降低技术,同相电容阵列第3个电容单元的电容接入电压转为接地,没有产生能耗,因此只有同相电容阵列的第1个电容单元产生了能耗,A1的转换能耗为

E4(A1)=CVcm{[Vcm-V+(4)]-[Vcm-V+(3)]}

(12)

由式(6)有V+(4)-V+(3)=-Vref/8,式(12)可整理为

(13)

对于A2转换,由于电压调整采用电荷共享技术,同相电容阵列第3个电容单元的电容接入电压保持接Vcm不变,因此同相电容阵列的第1、第3个电容单元都产生了能耗,A2的转换能耗为

E4(A2)=CVcm{[Vcm-V+(4)]-[Vcm-V+(3)]}+

2CVcm{[Vcm-V+(4)]-[Vcm-V+(2)]}

(14)

由式(7)有V+(4)-V+(3)=Vref/8,由式(4)和式(7)有V+(4)-V+(2)=-Vref/8,式(14)可整理为

(15)

在进行第i次比较时,转换能耗为

(16)

由于第1和第2次比较没有产生能耗,因此一个采样周期的电容阵列转换能耗为第3到第N次比较的转换能耗之和,即

Ecycle(D[1]D[2]…D[N])=

(17)

N位SAR ADC的输出码有2N种情况,将所有输出码的电容阵列转换能耗取平均即为平均能耗,即

(18)

在Matlab中进行仿真,几种10位电容阵列DAC结构的平均能耗如表1所示,转换能量随输出码的变化如图5所示,平均能耗随位数的变化如图6所示.从表1可知,高能效电容阵列DAC的平均能耗均比现有结构低,比传统结构减少了99.22%.

图5 几种10位电容阵列DAC的能耗随输出码的变化情况Fig.5 Changes of energy consumption of several 10-bit capacitive array DACs with output codes

从图5可知,高能效电容阵列DAC所有情况输出码的电容阵列转换能耗都比其他结构小.从图6可知,几种结构的平均能耗随着位数的增加而增加,高能效电容阵列DAC的平均能耗增加率比其他结构小.

表1 几种10位电容阵列DAC的转换能耗和面积减少率比较Table 1 Comparison of conversion energy consumption and area reduction for several 10-bit capacitive array DAC

4结论

文中提出了一种应用于SAR ADC的高能效电容阵列DAC,在前两次比较转换中由于采用顶板采样和电压移位技术,故电容阵列DAC没有产生能耗;从第3次比较转换起因采用了电荷共享和电压单调降低技术,故能耗相对其他结构显著降低.仿真结果表明,相比于传统结构,文中提出的高能效电容阵列DAC能耗降低了99.22%.该高能效电容阵列DAC能有效降低SAR ADC的整体功耗,可应用于植入式、便携式和穿戴式电子设备.

参考文献:

[1]Lin J Y,Hsieh C C.A 0.3 V 10-bit 1.17 f SAR ADC with merge and split switching in 90 nm CMOS [J].IEEE Transactions on Circuits and Systems Ⅰ:Regular Papers,2015,62(1):70-79.

[2]Lee H,Park S,Lim C,et al.A 100-nW 9.1-ENOB 20-kS/s SAR ADC for portable pulse oximeter [J].IEEE Transactions on Circuits and Systems Ⅱ:Express Briefs,2015,62(4):357-361.

[3]Chung Y H,Wu M H,Li H S.A 12-bit 8.47-fJ/conversion-step capacitor-swapping SAR ADC in 110-nm CMOS [J].IEEE Transactions on Circuits and Systems Ⅰ:Regular Papers,2015,62(1):10-18.

[4]Tao Y H,Lian Y.A 0.8-V,1-MS/s,10-bit SAR ADC for multi-channel neural recording [J].IEEE Transactions on Circuits and Systems I:Regular Papers,2015,62(2):366-375.

[5]Chen W M,Chiueh H,Chen T J,et al.A fully integrated 8-channel closed-loop neural-prosthetic CMOS SoC for real-time epileptic seizure control [J].IEEE Journal of Solid-State Circuits,2014,49(1):232-247.

[6]Long Y,Harpe P,Pamula V R,et al.A 680 nA ECG acquisition IC for leadless pacemaker applications [J].IEEE Transactions on Biomedical Circuits and Systems,2014,8(6):779-786.

[7]Judy M,Sodagar A M,Lotfi R,et al.Nonlinear signal-specific ADC for efficient neural recording in brain-machine interfaces [J].IEEE Transactions on Biomedical Circuits and Systems,2014,8(3):371-381.

[8]Chiu S W,Wang J H,Chang K H,et al.A fully integrated nose-on-a-chip for rapid diagnosis of ventilator-associated pneumonia [J].IEEE Transactions on Biomedical Circuits and Systems,2014,8(6):765-778.

[9]Ginsburg B P,Chandrakasan A P.An energy-efficient charge recycling approach for a SAR converter with capacitive DAC [C]∥Proceedings of 2005 IEEE International Symposium on Circuits and Systems.Kobe:IEEE,2005:184-187.

[10]Lee J S,Park I C.Capacitor array structure and switch control for energy-efficient SAR analog-to-digital converters [C]∥Proceedings of 2008 IEEE International Symposium on Circuits and Systems.Seattle:IEEE,2008:236-239.

[11]Liu C C,Chang S J,Huang G Y,et al.A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure [J].IEEE Journal of Solid-State Circuits,2010,45(4):731-740.

[12]Zhu Y,Chan C H,Chio U F,et al.A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS [J].IEEE Journal of Solid-State Circuits,2010,45(6):1111-1121.

[13]Yuan C,Lam Y.Low-energy and area-efficient tri-level switching scheme for SAR ADC [J].Electronics Letters,2012,48(9):482- 483.

[14]Zhu Z M,Yu X,Song X L.VCM-based monotonic capacitor switching scheme for SAR ADC [J].Electronics Letters,2013,49(5):327-329.

[15]Xie L B,Wen G J,Liu J X,et al.Energy-efficient hybrid capacitor switching scheme for SAR ADC [J].Electro-nics Letters,2014,50(1):22-23.

High Energy-Efficient Capacitor Array DAC for SAR ADC

HuYun-feng1,2LiBin1WuZhao-hui1

(1. School of Electronic and Information Engineering, South China University of Technology, Guangzhou 510640, Guangdong,

China; 2. Zhongshan Institute, University of Electronic Science and Technology of China, Zhongshan528402, Guangdong, China)

Abstract:Capacitor array digital-to-analogue converter (DAC) is one of the main energy consumption sources of successive approximation register analogue-to-digital converter (SAR ADC). In order to reduce the energy consumption of capacitor array DAC, this paper proposes a high energy-efficient capacitor array DAC structure. In the structure, each capacitor part is connected in turn through a switch. In the first two comparison cycles, owing to the top-plate sampling technique and the level shift technique, there is no switching energy consumption in the capacitor array DAC; in the rest of comparison cycles from the third to the nth, owing to the charge sharing technique and the voltage monotonic down technique, there exists a low switching energy consumption in the capacitor array DAC. Simulation results show that, in comparison with the traditional capacitor array DAC structure, the proposed structure can decrease the energy consumption by 99.22% and reduce the number of capacitors by 75%.

Key words:successive approximation register; analog to digital conversion; capacitor array DAC; high energy-efficiency

中图分类号:TN432

doi:10.3969/j.issn.1000-565X.2015.09.008

作者简介:胡云峰(1982-),男,在职博士生,电子科技大学中山学院讲师,主要从事逐次逼近型模数转换器研究.E-mail: shanhuyf@163.com†通信作者: 李斌(1967-),女,教授,博士生导师,主要从事半导体器件与模拟集成电路研究.E-mail: phlibin@scut.edu.cn

*基金项目:国家自然科学基金资助项目(60976026);国家自然科学基金面上项目(61571196)

收稿日期:2015-03-17

文章编号:1000-565X(2015)09-0047-07

Foundation items: Supported by the National Natural Science Foundation of China(60976026)and the General Program of the National Natural Science Foundation of China(61571196)