基于FPGA的多功能信号发生器设计与实现

2014-12-18刘艳昌左现刚李国厚

刘艳昌,左现刚,李国厚

(河南科技学院 信息工程学院,新乡 453003)

0 引言

信号发生器在工业、科技、教学等领域中已得到广泛应用,通常情况下使用较多的设计方案是利用FPGA、单片机等处理器芯片来控制专用信号发生芯片,这种设计方案与传统采用模拟分立器件来设计信号发生器的方法相比,具有信号频率更稳定、精度更高、信号参数易调节等优点,但存在电路设计复杂,成本较高等问题。随着电子技术和EDA技术的快速发展和深入研究,DDS技术得到飞速发展[1],使得信号发生器的设计和实现更加容易和灵活。DDS即直接频率合成器,与传统频率合成技术相比,具有频率分辨率高、频率切换速度快、频率改变时相位连续性保持不变和频率稳定度高等优点,因此极易实现信号的频率、相位和幅度控制。

针对采用VHDL或Verilog HDL语言设计一个所需的DDS模块存在编制源程序复杂问题,本文利用Altera公司推出的DSP Builder与MATLAB配合使用可以很方便搭建DDS模块,然后通过SignalCompiler工具对DDS模块进行编译,转化为可在QuartusII软件中使用的VHDL文件,最终将该VHDL文件生成实体化模块,以便与控制模块和D/A转换模块配合完成基于FPGA的多功能信号发生器的设计与实现。本文设计的多功能信号发生器,可输出正弦波、方波、三角波、锯齿波四种基本波形及其对应调幅波性和2ASK、2FSK、2PSK三种数字调制波波形,输出频率范围为1Hz~20MHz之间,输出幅度范围为1mV~5V且具有频率、相位和幅度可调功能。

1 基于DSP Builder的DDS实现

1.1 DDS设计原理

DDS是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写,它是从相位概念出发,建立在采样定理基础上的一种新的频率合成技术[2~4]。它主要由基准时钟源、相位累加器、相位调制器、波形存储器、幅度调制器、D/A转换器和低通滤波器LPF组成,其中N位相位累加器是核心。DDS原理结构图如图1所示[5~8]。

图1中时钟源fc为本系统的参考时钟,其频率fc=50MHz,输出信号的频率fo、幅度和相位可由频率控制字FCW、幅度控制字ACW和PCW字的值来控制,即通过改变不同的FCW、ACW和PCW控制字来获得输出不同的频率、幅度和相位信号。设相位累加器的位宽为N(频率输入控制字位宽),相位调制器位宽为M,则DDS的输出信号频率为:

输出信号的相位相移为:

输出信号的相对幅度为:

1.2 DDS系统模型的建立及仿真

1.2.1 基本波和AM调制波的DDS系统模型建立及仿真

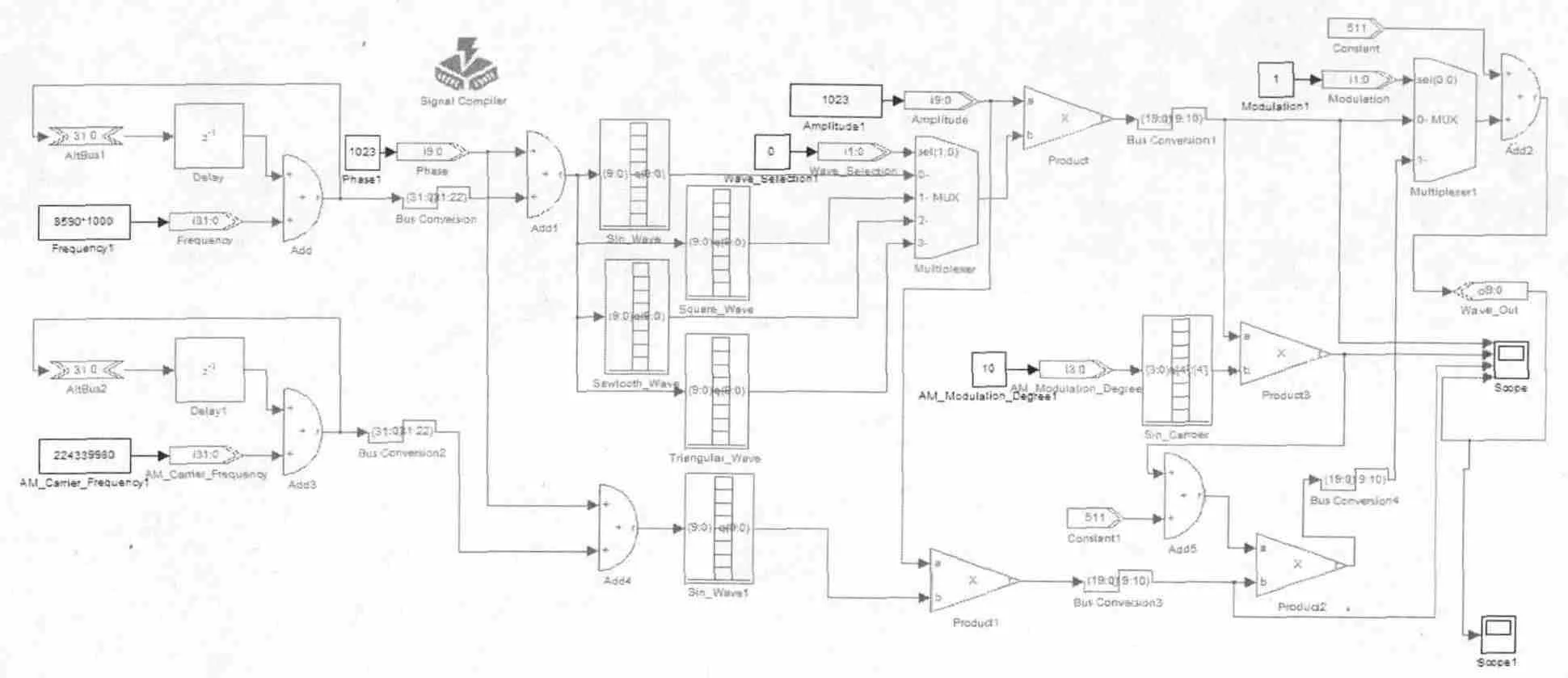

启动MATLAB软件,打开Simlink窗口新建一个.mld文件,然后调用Altera DSP Builder Blockset里面的模块搭建基本波和AM调制波的DDS系统模型如图2所示。

该系统主要由基本波形信号发生器、载波信号发生器、AM调制器和多路选择器组成。其波形参数设置时需在“MATLAB Array”编辑框中分别输入“511*sin([0:2*pi/1023:2*pi]),511*square(2*pi*[0:1/1023:1],50),511*(sawtooth(2*pi*[0:1/1023:1],1)),511*(sawtooth(2*pi*[0:1/1023:1],0.5))”,即可在SignalCompiler编译过程中,自动产生1024个相应的正弦波、方波、锯齿波和三角波数据。在搭建模块时,数据类型采用默认设置,即有符号整型,由于D/A转换芯片输入数据都是无符号正数,因此在总模块输出时通过加法器在输出端加511,就可把处在纵坐标负半轴的搬移到正半轴,以便在示波器上正确显示(其他加法器也是同样的道理)。

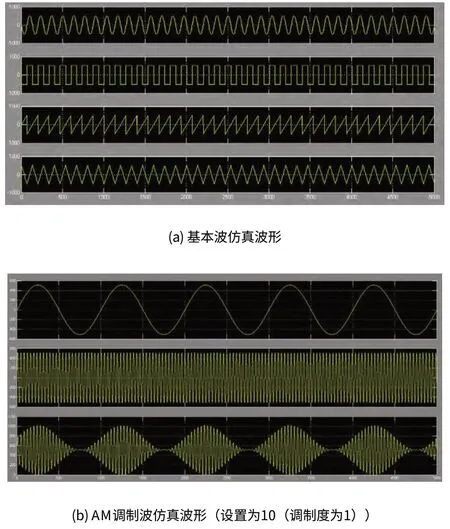

在图2中分别设置频率控制字为8590×1000,载波频率控制字为224339980,幅度控制字为1023,相位控制字为1023,载波调制深度为10(即幅度控制字为1023),数据选择器Multiplexer的波形选择Wave_Selection控制字取0(正弦波),数据选择器Multiplexer1的波形选择Wave_Selection控制字取1(正弦波调制)时的仿真波形如图3所示。

1.2.2 数字调制波的DDS系统模型建立及仿真

在1.2.1基本DDS模型设计基础上,利用其产生的正弦波作为载波信号,以二进制数字基带信号为调制信号,即可实现二进制数字调制信号。数字调制波的DDS系统模型如图4所示,主要由基本DDS模型及2ASK、2FSK和2PSK数字调制模块组成,通过改变幅度输入字、频率输入字和相位输入字即可实现2ASK、2FSK和2PSK的数字调制信号。

图2 基本波和AM调制波系统模型

图3 基本波和AM调制波仿真波形

按图4参数设置完成后,将基波和载波的波形输出接入同一个显示窗口便可启动仿真,其数字调制波仿真波形如图5所示:当二进制数字基带信号输出为0时,多路选择器Multiplexe、Multiplexe1和Multiplexe2选择0通道,即2ASK输出幅度为0,2FSK输出低频,2PSK输出0相位;当二进制数字基带信号输出为1时,多路选择器Multiplexe、Multiplexe1和Multiplexe2选择1通道,即2ASK输出幅度为511,2FSK输出高频,2PSK输出π相位,当多路选择器Multiplexe4输入端sel为00、01和10时,可分别实现2ASK、2FSK和2PSK调制波输出。

图4 数字调制波系统模型

图5 数字调制波仿真波形

2 多功能信号发生器硬件实现

2.1 DDS系统模块的生成

在上述基本波和AM调制波系统模型和数字调制波系统模型中首先双击Signal Compiler图标,然后选定Altera公司的EP2C5T144芯片类型后开始分析,可将在Simulink中设计的sin_GN.mdl和Binary_Keying_GN.mdl模型文件自动转化为.vhdl文件,最后在QuartusII环境中打开已创建的dgnxhfsq.bdf工程文件,将得到的.vhdl转化为sin_GN.bsf和Binary_Keying_GN.bsf文件,即为所生成的信号发生模块硬件符号,如图6所示。

图6 信号发生模块硬件符号

2.2 D/A转换模块

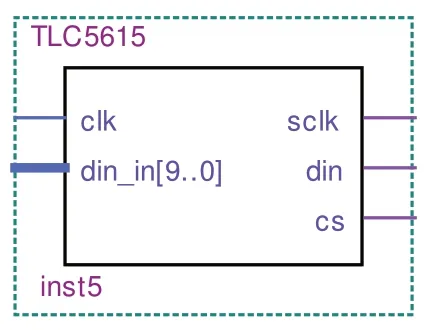

D/A转换器选择TLC5615芯片,该芯片是10位高速数模转换器。只需通过3根串行总线就可以完成10位数据串行输入,功耗低,使用方便。本系统只用一片TCL5615芯片,因此工作方式选择第一种。根据TLC5615工作时序,在QuartusII软件中通过verilog HDL语言编写驱动程序,然后将其生成模块硬件符号,如图7所示。为了提高输出波形的频率和分辨率,D/A芯片扫描时钟采用400MHz,这里利用QaurtusII内的IP核定制锁相环实现对信号的倍频。

其中clk为400MHz时钟信号;sclk为TLC5615芯片串行时钟输入信号;din_in[9..0]为输入的并行10位数据;din为经并-串转换后的数据输出送给TLC5615芯片输入端;sc为TLC5615的片选信号,低电平串行数据写入,高电平禁止。

图7 D/A驱动模块硬件符号

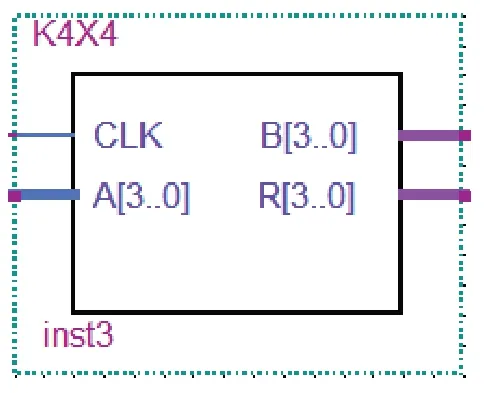

2.3 4×4矩阵键盘模块

矩阵键盘电路采用4×4行列式结构,将4条I/O线作为行线,与4条I/O列线进行交叉,便得到16个交叉点,在每个交叉点上接入一个按键,就构成4×4矩阵键盘。在判断具体哪个按键按下时,采用逐行扫描低电平方式,检查行输入是否处于低电平的状态来确定。根据各按键实现功能,在QuartusII软件中通过verilog HDL语言编写其驱动程序,然后将其生成模块硬件符号,如图8所示。

图8 4×4键盘驱动模块硬件符号

其中CLK为50MHz时钟信号;A[3..0]为键盘4位行线输入;B[3..0]为键盘4位列线输出;R[3..0]为键盘键值输出。

2.4 键值输入处理模块

键值输入处理模块主要实现对16个输入按键的具体功能进行处理,其中数字键10个,调制方式选择键、波形选择键、波态选择键、调制度键、确认键和删除键各1个。根据键值输入处理模块实现功能,在QuartusII软件中通过verilog HDL语言编写其驱动程序,然后将其生成模块硬件符号,如图9所示。

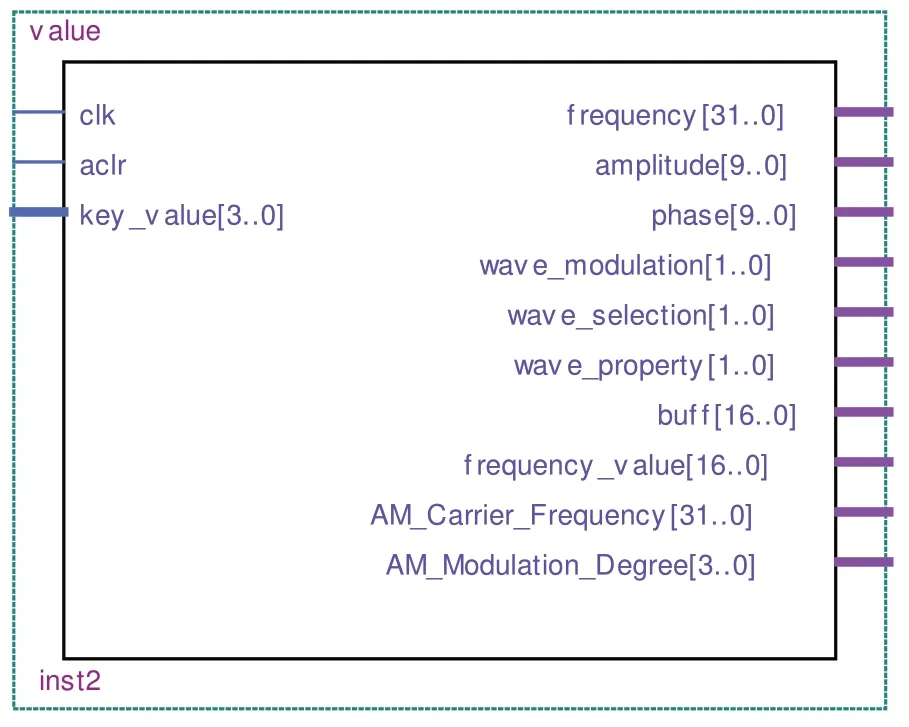

图9 输入键值处理模块硬件符号

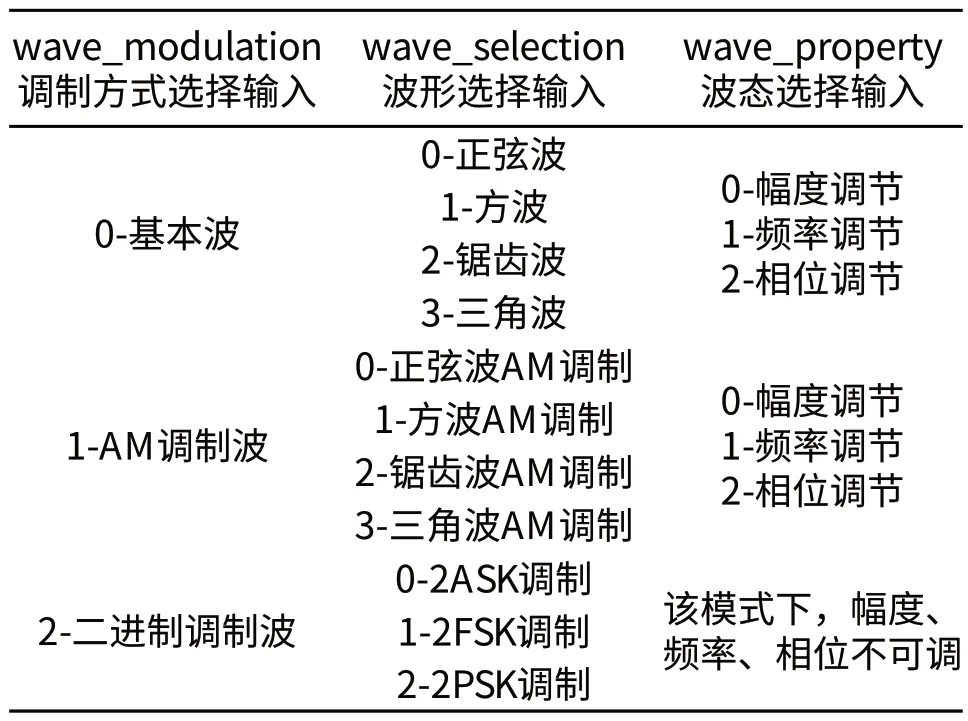

其中输入端口key_value[3..0]为键值输入;输出端口:frequency_value[16..0]为频率控制字输出;amplitude[9..0]为幅度控制字输出;phase[9..0]为相位控制字输出;buff[16..0]为缓存数据输输出;frequency_value[16..0]为频率值输出;AM_Carrier_Frequeny[31..0]为载波频率输出;AM_Modulation_Degree[3..0]为调幅波调制深度输出;其余输出端口控制功能如表1所示。

表1 波形输入端口控制功能

2.5 LCD显示模块

LCD显示模块采用带中文字库的12864型LCD液晶显示,主要用来显示输出波形的频率、幅度和相位值。根据显示功能,在QuartusII软件中通过verilog HDL语言编写显示驱动程序,然后将其生成模块硬件符号,如图10所示。

图10 LCD显示驱动模块硬件符号

其中输出端口:rs、rw、en、data[7..0]分别为LCD12864液晶显示器的读、写、使能、数据控制端口。

3 多功能信号发生器硬件下载与系统测试

3.1 多功能信号发生器硬件下载

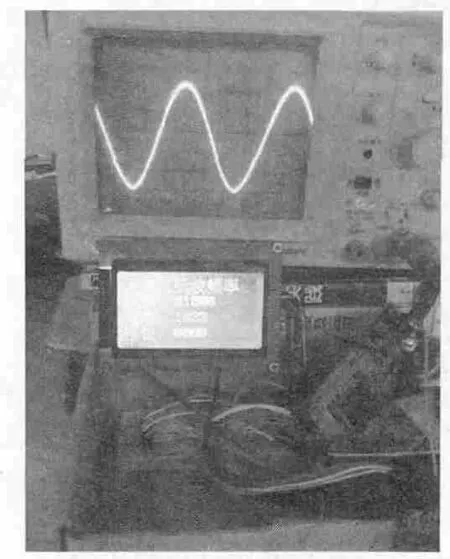

在QuartusII环境中打开已创建的dgnxhfsq.bdf工程文件,将上述各模块添加到该工程里,将其保存后设为顶层,编译、综合成功后将生成的dgnxhfsq.sof文件,通过JTAG模式下载到ALTERA公司的EP2C5T144C8芯片中得到实际硬件电路。文件下载成功后,通过键盘调试使其输出频率为1KHz,幅度为3V,相位为0的正弦波,其显示结果如图11所示。

图11 硬件下载结果

3.2 多功能信号发生器系统测试

为准确对系统性能进行分析,以正弦波为例从波形输出频率角度和幅度角度进行定量测试。采用频率计对多组特定频率及其稳定度进行定量测试,实测数据如表2所示。

表2实测结果表明,正弦波的输出频率范围为1Hz~20MHz,其中频率稳定度达到数量级10-5的输出信号频率范围为10Hz~5MHz,且多数频率测量点都存在正方向偏移。实测频率存在正误差的主要原因是由基准时钟精确性不高和数值处理过程中取舍误差造成的,通过改善基准时钟的精确性和提高运算速度能够改善该频率精度和稳定度。

采用示波器对正弦波输出幅度进行定量测试,实测数据如表3所示。

表3 正弦波输出幅度数据

从表3测试数据可知,10Hz~1MHz的正弦波输出信号幅度与满值5V输出相比,其最大偏差为0.2V,最小偏差0.02V,能够满足实际需要,且比较稳定。当输出频率大于1MHz时,幅度下降较大,输出20MHz时偏差最大。其主要原因是D/A转换精度不高和放大滤波电路增益衰减造成的,通过采用高精度D/A转换芯片和提高滤波器带宽及增益能够改善这个问题。

4 结束语

本文采用MATLAB/Simulink、DSP Builder对基波、AM调制波和数字调制波的DDS系统模型进行设计、仿真和建模,利用DSP Builder中的Signal Compiller工具将图形化建立的DDS模型转化为可在QuartusII软件中使用的VHDL文件,在QuartusII环境中生成硬件符号,并将其添加到工程中,然后再把各模块连接好的顶层实体下载到目标器件中,最终实现多功能信号发生器的设计。与传统的频率合成方法相比不仅避免了DDS模块编程的复杂性、节约了FPGA的逻辑资源,而且具有频率切换时间短、频率分辨率高、相位变化连续,功能扩充容易、成本较低、稳定度较高、抗干扰能力强、参数修改灵活和开发周期短等优点,能够满足实验室的基本需要,具有广阔的应用前景。

[1]朱凤武,邹丽娜,等.基于FPGA和DDS的数字调制信号发生器设计与实现[J].电子设计工程,2013,6(21):90-93.

[2]韩旭,郑磊.基于FPGA的任意波形发生器的设计与实现[J].电子测量技术,2013,7(32):62-66.

[3]万志江.基于FPGA的DDS IP核的研究与设计[J].微电子学与计算机,2013,8(30):98-102.

[4]张浪.DDS IP核设计及其在信号发生器中的应用[J].信息化研究,2010,10(36):46-48.

[5]王康佳,刘诗伟,孙番典.基于Matlab/DSP Builder任意波形信号发生器的两种设计.现代电子技术,2011,3(34):179-184.

[6]刘楠.基于FPGA的DDS信号发生器的实现[D].哈尔滨:哈尔滨理工大学,2011.

[7]肖炎根.基于SOPC的DDS函数信号发生器的设计[D].长沙:中南大学,2011.