VHDL语言在电子设计中的应用

2014-11-23王彩凤李卫兵

王彩凤,李卫兵,卞 丽

(滨州学院 a.光电工程系;b.教务处,山东 滨州 256603)

近年来,随着电子技术和计算机技术的迅速发展以及大规模集成电路的应用,电子设计变得越来越复杂,正朝着高速度、大容量、小体积的方向发展,使用传统的自底向上的设计方法进行系统及芯片设计已经不能满足要求,迫切需要提高设计效率。能大大降低设计难度的 VHDL设计方法正在被越来越广泛地采用,且运用硬件描述语言完成硬件设计成为电子设计的趋势,并朝着自动化方向发展,有效地缩短了开发周期,提高了开发效率及产品的可靠性[1-4]。

1 VHDL概述

VHDL语言是超高速集成电路硬件描述语言,是一种对数字电路系统进行性能描述和模拟的语言,由美国国防部在1983年创建,并在1987年作为“IEEE标准1076”发布,从此成为硬件描述语言的业界标准之一。1993年,IEEE对VHDL进行了修订,从更高的抽象层次和系统描述能力上扩展了VHDL的内容,公布了新版本的VHDL,即IEEE标准的1076-1993版本。现在,VHDL作为IEEE的工业标准硬件描述语言,得到众多EDA公司的支持,在电子工程领域,已成为事实上的通用硬件描述语言。现在公布的最新VHDL标准版本是IEEE 1076-2002[5]。

2 VHDL的特点

VHDL语言主要用于描述数字系统的结构、行为、功能和接口,与其他硬件描述语言相比,VHDL语言有如下优越之处:

1)VHDL语言具有很强的电路描述和建模能力,能从多个层次对数字系统进行建模和描述,从而大大简化了硬件设计任务,提高了设计效率和可靠性。

2)VHDL语言具有与具体硬件电路无关和与设计平台无关的特性,并且具有良好的电路行为描述和系统描述的能力,并在语言易读性和层次化、结构化设计方面,表现了强大的生命力和应用潜力[6]。

3)VHDL语言支持自上而下(top down)和基于库(library-base)的设计方法。在面对当今许多电子产品的生命周期缩短,需要多次重新设计以融入最新技术、改变工艺等方面都表现出了良好的适应性[7]。

4)用VHDL语言进行电子系统设计时,设计者可以专心致力于其功能的实现,而不需要对不影响功能的与工艺有关的因素花费过多的时间和精力。

3 VHDL的设计流程

VHDL语言的设计方法是一种高层次的设计方法,也称为系统级的设计方法。

1)设计输入

将电路系统以VHDL硬件描述语言的表达方式输入计算机。

2)综合

利用HDL综合器对设计进行综合是十分重要的一步。因为综合过程将把软件设计的HDL描述与硬件结构挂钩,是将软件转化为硬件电路的关键步骤,是文字描述与硬件实现的一座桥梁。综合就是将电路的高级语言(如行为描述)转换成低级的,可与FPGA/CPLD的基本结构相映射的网表文件或程序[8]。

3)布线布局(适配)

适配器也称结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件。适配器就是将综合后网表文件针对某一具体的目标器件进行逻辑映射操作,其中包括底层器件配置、逻辑分割、优化、布局布线操作。

4)仿真

1)任务型教学法有利于发挥学生的主体作用,是真正以学生为本的教学方法。在任务型教学中,教师设计的各项教学活动都是以学生为主体,学生在教师的指导下,自主完成各项教学“任务”,教师帮助学生掌握学习方法,学会独立思考和处理问题。这一方法给了学生自由地认知语言的空间,让学生通过完成任务,探索所需的知识,寻找语言学习的规律,掌握认知语言。

仿真就是让计算机根据一定的算法和一定的仿真库对EDA设计进行模拟,以验证设计,排除错误。仿真包括:

(1)时序仿真。就是接近真实器件运行特性的仿真,仿真文件中已包含了器件硬件特性参数,因而仿真精度高。

(2)功能仿真。是直接对VHDL描述的逻辑功能进行测试模拟,以了解其实现的功能是否满足原设计要求的过程。仿真过程不涉及任何具体器件的硬件特性。

5)下载和硬件测试

把适配后生成的下载或配置文件,通过编程器或编程电缆向FPGA或CPLD进行下载,以便进行硬件调试和验证。最后,将含有载入了设计的FPGA或CPLD的硬件系统进行统一测试,以便最终验证设计项目在目标系统上的实际工作情况,以排除错误,改进设计[9]。

4 VHDL在电子设计中的应用实例

以十进制计数器的设计为例说明VHDL语言在电子设计中的应用,该计数器具有异步清零和同步时钟使能的特点。

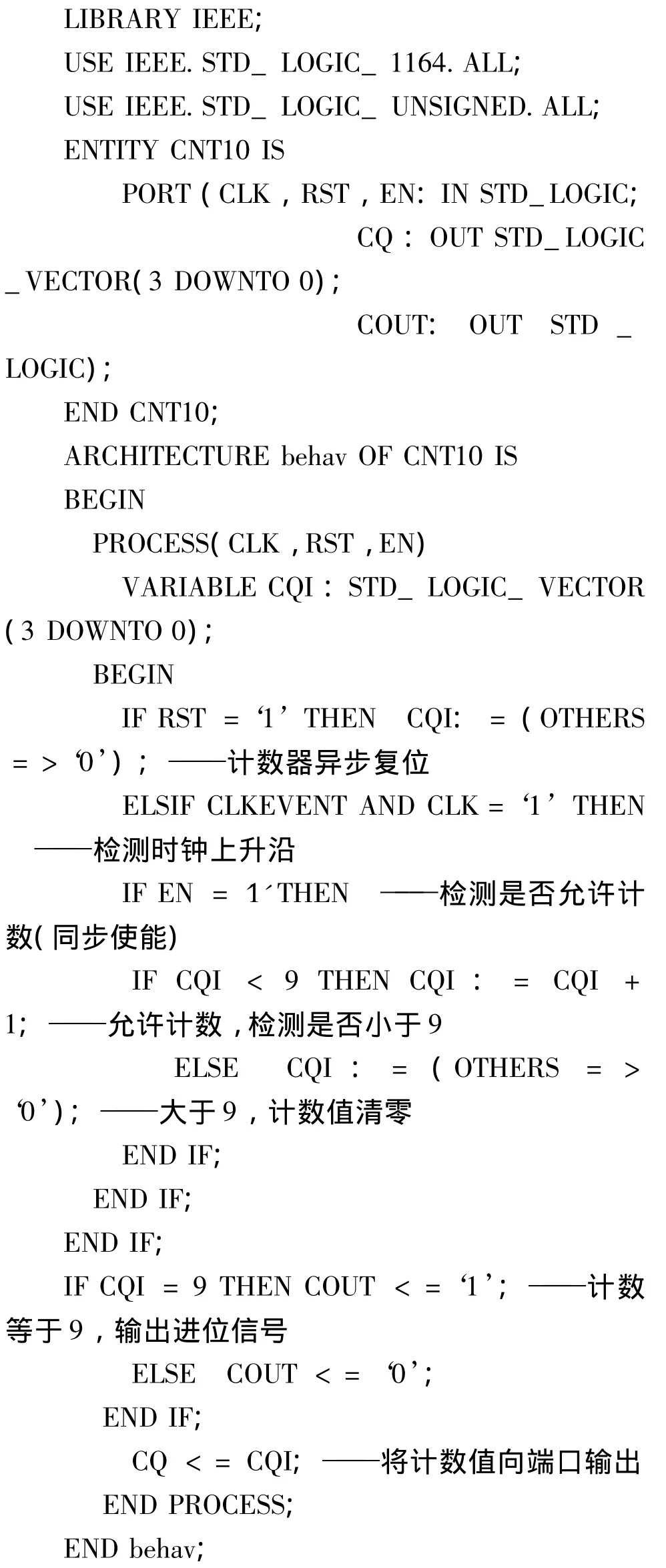

4.1 VHDL程序设计

可见程序相当简单而且逻辑清晰。这种自顶向下的设计方法使一个较大的系统设计分解为若干个可操作的模块,易于分工合作,并且可以对这些模块分别进行模拟仿真。由于设计的主要模拟仿真是在高层上实现的,所以能及早发现系统中的错误并改正,提高设计的效率。

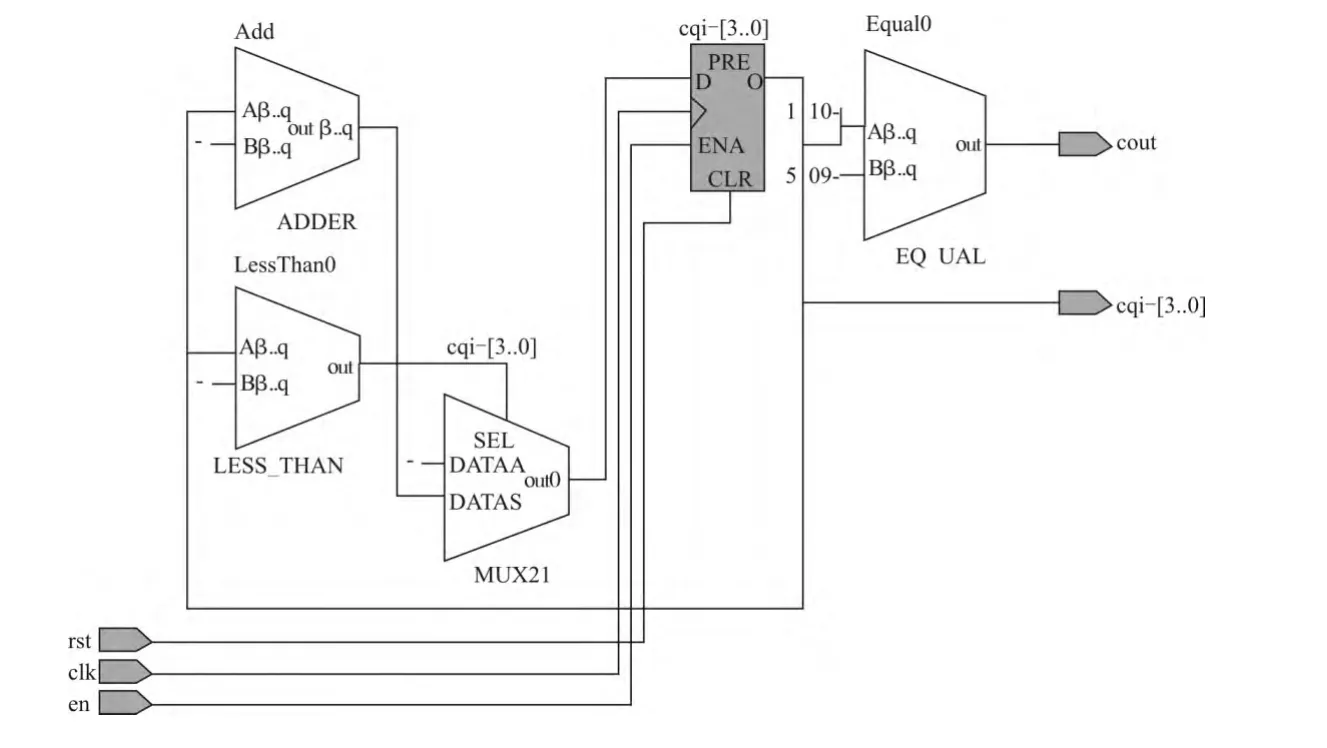

4.2 RTL电路图

图1是利用著名的HDL综合器Synplify对上例的综合结果。如电路图所示,电路含有比较器、组合电路加1器、2选1多路选择器、4位锁存器等。

图1 CNT10的RTL电路图

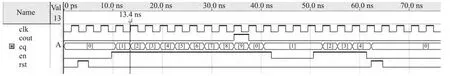

4.3 仿真结果

仿真结果表明,VHDL程序所描述的功能与上述波形是完全一致的,而且从图1所示的电路图也能得到相同的结果,图2中:

1)当RST为高电平,EN为低电平时,CQ输出为0,即计数清零,并禁止计数。

2)当RST为低电平,EN为高电平时,每一个CLK的上升沿后,CQ输出加1,而当CQ输出为9时,COUT输出高电平进位信号。

3)当EN为低电平时,计数器保持原有的计数“1”,当EN为高电平时则继续计数。

图2 CNT10的仿真波形图

5 结束语

用VHDL语言实现电子设计,是一个以软件设计为主,器件配置相结合的过程,能从多个层次对数字系统进行设计,设计数字电路更为灵活方便,设计周期也可大大减小,提高了设计效率和可靠性。目前,VHDL已成为电子设计自动化领域进行自顶向下设计的应用方向,是专用数字集成电路设计描述的有力工具,也是逻辑综合和优化的重要基础。作为一种重要的高层设计技术,VHDL已成为当代电子设计者们必须掌握的重要工具,并将会给硬件的设计领域带来很大的变革。

[1] 夏莉莉.浅议VHDL语言在电子设计自动化中的应用[J].信息安全与技术,2012(7):44-46.

[2] 李要球,卢璐.VHDL硬件描述语言在数字电路设计中的应用[J].实验室科学,2011,14(5):97-100.

[3] 邬锡琴.VHDL语言在数字电路教学中的应用[J].电脑知识与技术,2008(21):573-576.

[4] 夏益民,禹思敏,谢云,等.“VHDL程序设计”课程教学改革探讨[J].广东工业大学学报 :社会科学版 ,2009(9):117-118,124.

[5] 潘松,黄继业.EDA技术与 VHDL[M].3版.北京:清华大学出版社,2009:4-5.

[6] 张文英.基于VHDL语言的数字电路设计[J].中国仪器仪表,2006(3):95-96.

[7] 夏琰,师卫.硬件描述语言与数字电路设计[J].电力学报,2009,24(4):156-158.

[8] 王利,弓楠.VHDL语言在数字电路实验中的应用[J].现代电子技术,2007(6):162-163.

[9] 王彩凤,胡波,李卫兵,等.EDA技术在数字电子技术实验中的应用[J].实验科学与技术,2011,9(1):4-6.