PCB信号完整性测试技术研究

2014-11-05苏新虹胡新星

刘 丰 苏新虹 胡新星

(珠海方正印刷电路板发展有限公司,广东 珠海 519170)

在计算机,通信,视频和网络系统等电子信息领域,随着数字系统设计人员越来越高地追求时钟和数据速率,信号完整性作为一个需求不断增长的性能,已渐渐占据电子系统性能的优先级位置。在今天的高工作频率下,任何影响到信号的上升时间,脉冲宽度,定时抖动或噪声含量都会影响系统级的可靠性。

印制电路板(PCB)是电子设备结构中装载组件的平台,同时提供了部件之间重要的电气连接。几乎所有的信号完整性问题都开始和结束于PCB。近年来,高密度超大规模集成电路、更高的处理速度的要求和更快的数据传输速率,导致PCB变得越来越复杂。

PCB的信号完整性问题越来越突出,如何正确设计以降低PCB本身的损耗已成为一个既符合成本效益又关乎功能性的课题,越来越多的PCB制造商加入到了研究PCB信号完整性中,而这一切的前提便是PCB信号完整性测试。

要判断一个系统的好坏,首先就需要精确的测试工作,当年,PCB制造行业仅仅满足于线路阻抗合格的时代已逐渐远去,代之的是更严格的阻抗控制标准和插入损耗标准。

图1 高速PCB、电子产品与信号完整性

1 PCB信号完整性和阻抗控制

业内有句话说得好,做得好阻抗,不一定做得好信号完整性;做不好阻抗,就一定做不好信号完整性。阻抗控制是PCB信号完整性中十分重要的一环。业界目前一般应用TDR来测试线路的阻抗。阻抗在时域范畴内分析,作为时间的函数,将沿着线路长度方向波动。

1.1 基于TDR的阻抗测试

1.1.1 历史

TDR(Time Domain Refl ector,时域反射计)测试最早始于20世纪30年代后期,开始被地质学家和其他科学家所关注。他们认识到土壤,岩石等材料的介电特性与其水分含量之间有显著关系。到20世纪60年代已经广泛应用于电子信息行业。

1.1.2 原理

TDR的工作原理同于雷达。设备使用脉冲或阶跃信号发生器,发射一个快速边沿的信号,沿着电缆传导下来,入射和反射电压波由在线路上的特定点的宽带示波器监视。通过测量输入电压之比的反射电压的计算简单的不连续的阻抗。当该信号到达电缆末端,或电缆故障点时,部分或全部的脉冲能量将被反射回至发射端,此时不连续点可以通过时间的函数确定。不连续(容性或感性)的类型也可以通过响应来判断。

1.2 阻抗控制

1.2.1 线路阻抗测试

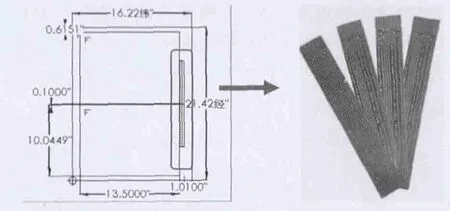

对于线路阻抗测试,在线路板厂中间流行的一种方法是在大板板边增加阻抗测试条,模拟客户提供的各种阻抗规格,测试条长度一般在100 mm(4 in)到150 mm(6 in)之间,且PCB厂家有各自的标准。图2所示。

图2 板边阻抗条

这种做法存在很大风险:阻抗条本身靠近板边,线路蚀刻效果与板内信号线存在较大差异,同样,层压时板边流胶量相对较大,存在介质层偏薄的风险……在这些工艺因素的限制下,要使板边阻抗条能够准确反映出板内阻抗的大小,对设备能力和工程设计技巧的要求是非常高的。

图3 阻抗波形中某一段无法代表整个阻抗值

至于测试标准,业界也一直无法统一。更多的是线路板厂在测量阻抗时,按照各自对阻抗测量的理解设定品质标准。例如,究竟是以哪一段的阻抗作为阻抗条最终取值难以确定,有很多公司以50%~70%的阻抗波形平均值作为最终阻抗值,于是按这样的取值标准,其他波段的阻抗变化无法反映在内,从而导致阻抗监控失效。如图3所示。也有公司取全波段的阻抗平均值作为结果,这造成了另一个问题,与阻抗线连接的过孔通常会拉低或者拉高阻抗线本身的阻抗值,且过孔引入的不确定因素相当高。如图4所示。

另外,当阻抗条达到一定长度时[如:大于200 mm(8 in)],在远端会由于损耗的原因,造成波形末端上翘,阻抗值向上波动的情况。当然,在当前技术水平下还不至于影响整体阻抗值。

图4 过孔阻抗变化拉低全波段阻抗

以现有的PCB发展水平来看,更为稳妥和现实的方法是:(1)阻抗条拼在大板内,而非靠近板边;(2)有条件的板厂尽量使用可调间距的差分阻抗探头(图5)监控板内的差分阻抗线,而非阻抗条数据;(3)阻抗条长度在合适的范围内,一般保证阻抗线长200 mm(4 in)即可。阻抗波形读取25%~75%区间最大、最小值和平均值。

图5 间距可调差分阻抗探头

1.2.2 过孔阻抗测试

几乎没有客户会要求PCB供应商测量过孔阻抗,但很多情况下,PCB损耗过高很大一部分是过孔阻抗与传输线阻抗不匹配问题导致的。当过孔与传输线阻抗相差过大时,会由于反射而引起信号的衰减,影响PCB信号完整性。

通过一个案例说明过孔阻抗对PCB损耗的影响。如表1为同一种材料,按相同的叠构、线路规格等在其内层L5层分别制作一对200 mm(4 in)长的差分带状线,经由过孔引出。过孔分别在两家具有不同规模和技术水平的工厂制得,两家工厂制作的过孔阻抗相差甚远,且孔阻抗与线路阻抗差别较大的,其传输线总体损耗值增加了0.1 dB/in,这是十分可怕的。

表1 不同过孔阻抗差分带状线的损耗测试结果

PCB过孔相对很短,其阻抗与孔径大小、焊盘、反焊盘都有联系。PCB设计者在研发伊始会做细致而复杂的仿真实验,其中就包含过孔的影响因素在内。以现阶段的传输速率和留给PCB的损耗余量,只要PCB供应商能够按设计者的要求加工,过孔阻抗就还没有达到非控不可的地步。但高端服务器、路由器等产品中有数以万计的过孔,互相之间有千丝万缕的联系,一旦过孔阻抗失配,将严重影响PCB功能。

小结:做好阻抗控制是保证PCB信号完整性的前提,从前15%的阻抗控制公差已无法满足PCB高速产品需要,业内已有7%的阻抗公差标准,这意味着,在高速时代对PCB阻抗控制要求必将越来越严苛。

有越来越多的PCB制造商已引入先进的仿真技术,对PCB工程设计和工艺进行仿真,寻求改善阻抗的最佳参数,这种理念也同样适用于对过孔阻抗的优化和控制,利用仿真工具辅助PCB制造,将成为新的技术趋势。

2 PCB信号完整性测量

信号完整性是一个广义的概念,包括由于互连、电源、器件、PCB等引起的所有信号质量及延时问题,从而造成误码、信号畸变等问题,这些都是信号完整性问题。对于裸板PCB,信号完整性的研究相对来说比较简单, 这里只针对插入损耗测量加以阐述。

2.1 基于VNA(矢量网络分析仪)的测试

2.1.1 历史

在20世纪60年代,安捷伦推出了第一台8407射频网络分析仪,惠普公司研发出8410网络分析仪,最高可扫频到12 GHz,到了80年代中期,网络分析仪起到了长足的发展和广泛的应用。

2001年,安捷伦E5071C投入市场,它是第一台在大批量应用中测试四端口网络参数的仪器,动态范围20 GHz。2006年,可达67 GHz超高测试频率的PNA诞生。

2.1.2 基于VNA的PCB信号完整性测试

矢量网络分析仪(VNA)号称动态范围最广的测试设备,当测试频率超过15GHz时,没有任何设备可以如VNA一样游刃有余地观察待测物在高频段的信号完整性特征。它测量待测物的S参数,来达到测试信号完整性的目的。

VNA功能强大,本身一般集成TDR选件,可以同时测量待测物的时域和频域特性,包括阻抗、插入损耗、回波损耗、眼图等,直观而且方便,测试快捷迅速,耗时短。

随着高速时代的到来,矢量网络分析仪已经被引进到越来越多的PCB厂家内。VNA测试需要复杂的校正程序以保证其精度,也需要有专门的VNA测试coupon设计,而考虑到拼版利用率等实际因素,常规的PCB是不具备专门的VNA测试coupon的。

VNA测试需要高精度的外围配件,如电缆、连接头或探针等。要在PCB裸板信号测试中得到精度的数据,就必须去除这些配件的影响,进而需要细致的校正工作。VNA提供多种校正方法,精度要求不高时,使用传统的Deskew方法即可;要得到高精度,就需要进行TRL(Thru、Reflect、Line)校准。一个高精度的TRL校准程序包含开路、短路、负载、thru的校准,对于不同频率段的测量,还包括相对应的从低频到高频区间的校准图形(图6)。业界一直没有停止追求VNA和TRL校准精度的脚步。

图6 TRL校准设备和常用图形

当然,VNA 也并不是万能的,它的精确度是建立在复杂校准的基础上;此外,VNA也不能直接在直流情况下进行测量,当被测件很长时(电缆),完成低频测量也要花费很长时间。这就是VNA和TDR相结合的魅力,矢量网络分析仪搭配时域反射计的测试方法已完美地覆盖了信号测试的各个频率范围。

使用VNA测试PCB信号完整性性能,需要注意以下几点:

(1)需要建立完善的测量校准体系。PCB制造商通常需要建立专用的校准模型和测试模型(图7)。设备方面,电缆、校准器件、连接头或探针是必不可少的,如今一台VNA已经整合了从时域到频域测量的所有模块和插件,极大地方便了使用者。

图7 VNA测试模型

(2)对于PCB厂商而言,主要压力来源于客户对PCB产品损耗、阻抗等电性要求,而板材供应商对这方面的支持又少,因此在测量中,PCB厂商应着重于材料电气特性和PCB工程设计合理性等方面的研究。如在特定频率下某材料裸板PCB的损耗和阻抗等,PCB厂商逐步收集到这些信息,建立自己的数据记录系统,做到心中有数,最主要的,依靠VNA设备,PCB厂家可以更接近和了解客户需求,有利于技术提升。

小结:VNA功能的强大不言而喻,作为PCB制造商,引进VNA设备在未来的竞争中十分必要。随着高速PCB的发展,设计者和制造商的距离将越来越近,合作也必将更加紧密。

2.2 基于SET2DIL理论的插入损耗测量:

VNA具有高精度和高动态范围的测量,但由于其测量基于复杂而严密的校准工作和测试coupon的限制,VNA仍然没有用于批量PCB产品的监控上。而SET2DIL则通过在牺牲了部分频率下精度的方式,将传统的实验室测试发展到了更广泛的批量生产中去。

2.2.1 历史

基于传统的四端口测量插入损耗的模式(如图8)需要同时在差分线的两端测量收集测试结果,耗时耗力,成本也非常高。

图8 传统四端口测量损耗(左图来自INTEL)

INTEL于2010年提出了SET2DIL测试理论,SET2DIL即single ended TDR/TDT test to derive differential loss,意为通过单端的TDR/TDT测试推导差分损耗的方法。

这种方式可以使测量者仅用一个专用探头、在一端测试(如图9),即可得到差分线的损耗值,相对于传统四端口测量节省了大量的时间和人力物力。

2.2.2 基于SET2DIL的PCB插损测试

测试设备上,配置十分简单,只需一台TDR(一般频率范围0~20 GHz,PCB厂家通常用作阻抗测试机)、INTEL授权的SET2DIL测试软件、专用SET2DIL测试探头和高频同轴电缆即可。总体配置比VNA价格低很多,由于TDR几乎是每个PCB工厂必不可少的设备,因此额外的投入也仅仅是软件和探头费用而已。

SET2DIL测试的校准流程也很方便,连接仪器、电脑和配件后,只需对整个系统做一次或几次Deskew,将信号时延同步到可接受范围内(如1 ps)即可。接下来测试按软件提示进行,测量完成后,允许使用者保存原始数据、测试波形和插入损耗值等等。

由于SET2DIL所测量的DUT(Device Under Test,被测物)都是相互独立的,PCB厂商只需要在板边针对所需要的层别和阻抗线增加coupon条即可,几乎不占用拼版资源。随着SET2DIL技术的应用和推广,已经有越来越多的终端客户在自己的产品上增加SET2DIL测试模块,达到监控产品损耗的目的。

当然,SET2DIL也有一些先天的不足之处,如:

(1)由于SET2DIL本身的算法包含有近似的理论成分,因此其有效性和准确性仅在一定的频率范围内能够得到保证,区间大约在2 GHz到12 GHz,超出这个范围的测试值和理论拟合值则会存在较大的偏差,影响结果的可信度。事实上,这个区间对于当今大多数的服务器或路由器产品已经足够;

(2)SET2DIL的探头为GSSG(地-信号-信号-地)形式,探针直径约0.1 mm(4 mil)左右,十分脆弱,接地片材质也很薄,非常容易损坏,一般一支全新探头的使用寿命在3000~5000个测试点不等,这给PCB工厂的成本带来很大负面影响。相信随着SET2DIL探头的应用越来越普遍,探头供货商增多和质量更好,这种情况会逐步改善。

小结:批量产品测量损耗是行业发展的趋势,仅仅在实验室内测试PCB产品损耗已成为过去,未来,必将有更成熟的SET2DIL测试方法产生。

图9 两端口损耗测试和SET2DIL测

3 Dk、Df提取

PCB在设计阻抗时一定会用到基材Dk值,这些Dk值最开始都是从板材供应商处得到。材料供应商流行的测量Dk的方法则是空腔谐振测试法(Cavity Resonance),测试样片为纯基材,根据特定的频率下的共振情况推导出材料的Dk值。

然而,PCB加工过程中,涉及大量化学药水和机械处理、热处理,材料的Dk和Df水平也将相应发生变化。在过去的低速时代,PCB产品主要考虑材料热可靠性,产生了一大批性能优良的无铅PCB板材。这些板材填料较为简单,电性能相对稳定。有的材料已应用近十年,Dk值已经被长期的生产过程验证,基本不会有太大的偏差。但新材料,板材供应商提供的Dk已被证明出与实际生产经验值存在显著差异,最大甚至可达到0.3左右的偏差。这对于阻抗精度控制是十分不利的。

于是,从PCB设计终端到PCB制造商,对于准确提取Dk值的研究工作开始了。有传统的基于简单的阻抗线切片和POLAR阻抗计算模型的反推法,这种方法无需额外的投入,只需制作PCB阻抗测试Coupon,通过切片测试和软件计算即可得到。然而这种测试方法忽略了频率的影响,同时引入了很大的测量误差,且无法得到Df的有关信息。

一种新型的Dk、Df提取方法基于VNA测试,首先通过专用测试Coupon提取单端带状线的S参数S1,接下来从提取的群延时计算出粗略Dk值作为其中一个变量;再通过专用软件生成一条单端带状线模型,操作者根据板材厂商提供的Df值设置另外的变量,把它和前面Dk一起代入带状线模型中仿真,并与实际测量得到的单端带状线参数S1拟合,当拟合度达到要求时,提取当时的Dk、Df即可。这种提取方法可以达到相当高的精度,并已被实验室测试成功验证,其相位精度可达到小于5度的偏差(图10)。

图10 DkDf提取软件精度的相位验证

小结:Dk、Df的研究对PCB供应商来说至关重要,特别是Dk的研究,直接关系到PCB厂商的阻抗控制能力。选择一种好的方法测量Dk,建立材料Dk数据库,对PCB供应商技术能力提升十分有益。

4 总结

高速PCB的发展日新月异,PCB信号完整性测试是发展高端信号完整性技术的基石,VNA测量技术、SET2DIL技术以及Dk/Df提取技术是其中最具代表性的技术,并具有相当高的实用性,这些技术,在不久的将来必将得到长足的发展和优化,PCB厂家应该将这些先进的测试方法作为技术储备,以应对高速时代带来的挑战。

[1]张贤士. 信号完整性基础知识[M]. 中兴通讯上海第一研究所, 2000:25.

[2]张木水, 李玉山. 信号完整性分析与设计[M]. 电子工业出版社, 2010, 2,47,88.

[3]于争. 信号完整性揭秘[M]. 机械工业出版社,2013:110,184.

[4]Jeff Loyer和Richard Kunze. SET2DIL: Method to Derive Differential Insertion Loss from Single-Ended TDR/TDT Measurements[C]. 英特尔技术论文, 2010:3,4,5,6.Agilent. Agilent Time Domain Analysis Using a

[5]Network Analyzer[C]. 安捷伦技术论文:5,6.Roger Stancliff和Joel Dunsmore, The Evolution of

[6]RF/Microwave Network Analyzers, 安捷伦技术论文:2,3,4,5.