一种基于FPGA的实时视频跟踪系统硬件平台设计*

2014-09-25刘紫燕

刘紫燕, 冯 亮, 祁 佳

(贵州大学 电子信息学院,贵州 贵阳 550025)

0 引 言

随着工业自动化水平和科学技术的不断发展和提高,人们可以不需要到达现场而通过视频跟踪系统来实现实时了解监控对象的信息,在该系统中间加上图像处理和控制部分,还可以实现对目标运动状态的判断和控制[1]。以机器视觉技术为基础的视频跟踪系统,目前已经广泛应用于人们生产、生活的各个方面[2],它通过实时图像处理技术确定视野中是否存在目标和目标的位置,获得目标参数,对运动目标进行匹配和跟踪,进而获得目标的运动轨迹,然后通过跟踪算法实现对运动目标的实时跟踪定位,同时在完成目标定位置测量的基础上实现对云台的控制。

目前,在嵌入式平台上实现视频跟踪主要有以下3种:ARM,DSP和FPGA平台。FPGA是一种半定制电路,既继承了ASIC高集成度、大规模等优点,又具有设计灵活等特点。可编程片上系统 (SOPC)是基于大规模可编程器件FPGA芯片的单片系统,它把整个系统利用逻辑编程技术集成到一个硅片上,包括硬核、软核、存储器、I/O等设备。SOPC具有开发设计灵活、可移植操作系统、实时检测、高级语言编程等优点。基于FPGA的SOPC比ARM系统处理速度快,比DSP系统控制能力强[2~4]。

本文提出了一种基于FPGA的实时视频跟踪系统硬件平台的设计方法。通过该平台,可以实现实时图像采集、缓存、显示和云台驱动;在Nios II软核处理器中加入目标检测跟踪控制代码,可以实现运动目标跟踪、定位以及产生云台PWM控制信号,使得摄像头随着运动目标的移动而改变转动方向,从而实现自主跟踪。

1 系统总体设计

1.1 系统结构图

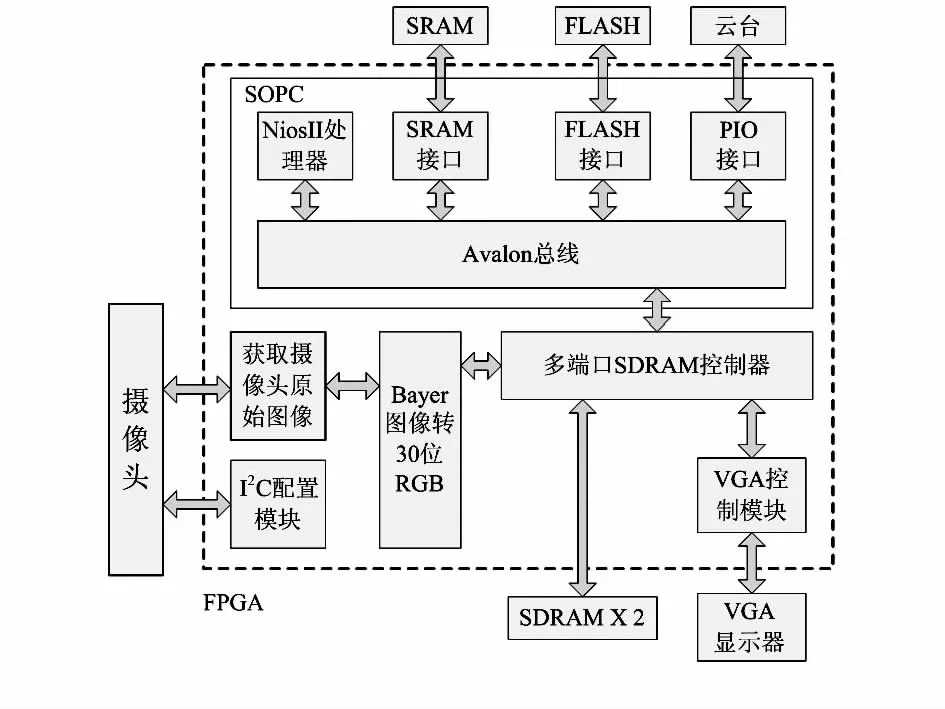

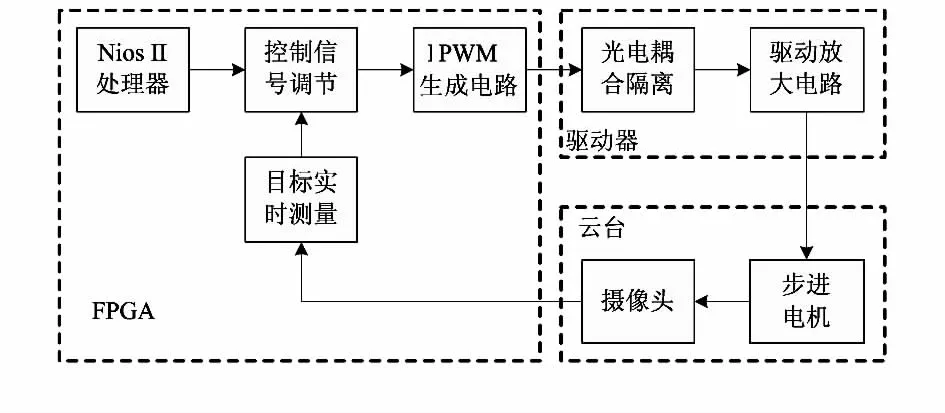

基于FPGA的视频跟踪系统主要包括视频图像的采集、图像的缓存与处理、图像的跟踪定位、图像的传输显示和云台的控制等几部分。视频图像的处理对于系统主芯片的处理能力有很高要求,如果所有的视频图像处理工作都由Nios II软核处理器来完成,将会造成Nios II软核处理器负担过重,从而无法得到很好处理效果。因此,本文将视频图像的采集、图像传感器的配置、图像转换、图像的帧缓存、图像VGA显示控制等部分全部由FPGA硬件逻辑实现,只将视频图像处理跟踪算法、云台控制等其它少部分工作交给Nios II软核处理器来完成,这样可以减少Nios II软核的处理压力,从而提高系统的整体性能[1]。视频跟踪系统的设计框图如图1所示[1,5,6]。

图1 视频跟踪系统框图

整个视频跟踪系统的设计以FPGA作为核心,图1上部分为在FPGA中搭建的SOPC,其中,嵌入了Nios II软核处理器,各个模块通过Avalon总线与Nios II处理器进行互联通信;图1下部分为跟踪系统实时图像的采集、缓存以及VGA显示等功能,各个功能模块是用硬件描述语言实现的。视频跟踪系统中的多端口SDRAM控制模块是视频跟踪系统的一个重要部分,它将图像传感器采集过来的帧图像进行缓存,然后一个端口送给VGA显示器进行显示,另一个端口送给SOPC中的Nios II软核处理器进行视频图像处理和运动目标的跟踪控制算法的实现等。

1.2 系统工作流程

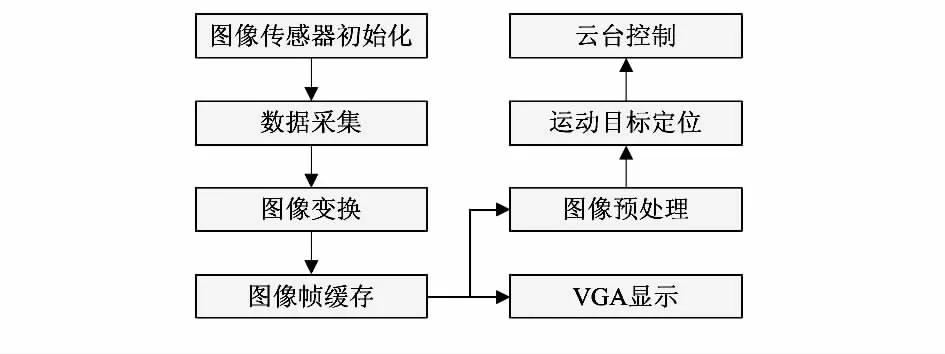

视频跟踪系统上电后,首先对CMOS图像传感器初始化,再进行视频图像的数据采集。然后将采集来的视频图像进行格式变换输出30位RGB图像数据,并通过多端口SDRAM将图像数据输入2片SDRAM进行帧缓存。同时,多端口SDRAM控制器的一个输出端口将缓存的数据送给VGA显示器进行图像显示,另一个输出端口送给SOPC中的Nios II软核处理器进行视频图像处理和运动目标的跟踪定位。图2为视频跟踪系统的工作流程图。

图2 视频跟踪系统工作流程

2 系统硬件平台设计

系统硬件平台设计包括CMOS图像的采集、图像传感器的配置、图像转换、多端口SDROM控制器设计、图像的帧缓存、图像的VGA显示、SOPC系统搭建和硬件外设电路设计等。

2.1 实时视频采集

视频图像采集模块是实时视频跟踪系统重要的组成环节,图像采集质量的好坏不仅影响后端运动目标跟踪的准确率,而且也决定实时视频预处理难度。

本平台设计中视频图像采集设备采用Terasic公司提供的TRDB—D5M摄像头。TRDB—D5M摄像头具有500万像素,可通过GPIO与FPGA相连。此外,TRDM—D5M支持手动调焦,可以避免在不同距离下图像质量出现较大的差别。

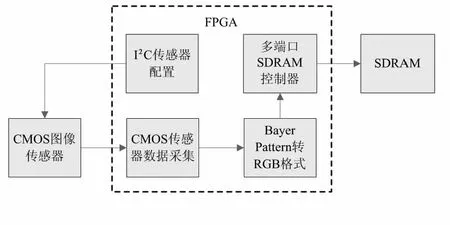

图3为视频图像采集结构图,虚线框代表的是FPGA体系结构,其它为外部元件。系统启动后,FPGA内部的I2C传感器配置模块初始化CMOS图像传感器。然后CMOS传感器数据采集模块捕获来自CMOS图像传感器的图像帧。接着CMOS传感器采集的数据进行简单的转换可以变为RGB颜色空间格式。最后,多端口SDRAM控制器将转换后的图像数据保存到SDRAM中[7]。

图3 图像采集结构图

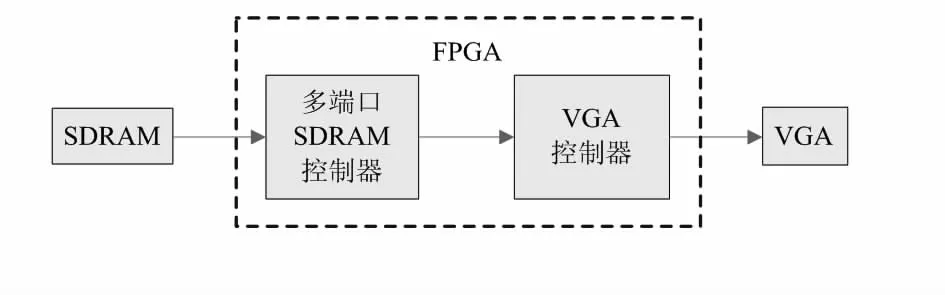

2.2 实时图像VGA显示

实时视频跟踪系统中,FPGA除了要完成跟踪等任务外,还要实现对VGA显示的接口控制,完成视频图像数据的视频显示。

在DE2—70开发板中,集成了一个支持VGA输出的16针脚D—SUB连接器。Cyclone II FPGA直接提供给VGA同步信号,同时模拟信号设备ADV7123中的3个10位高速视频芯片DAC被用作模拟数据信号(红、绿和蓝)发生器,这些电路组合最高能支持像素为1 600×1 200的分辨率。

图4为图像VGA显示结构图,多端口SDRAM控制器从SDRAM存储芯片中读出的图像数据,并且将图像数据传递到VGA控制器,用于VGA显示实时图像。图像VGA显示的能否正常工作,VGA控制器起着关键作用。

图4 图像VGA显示结构图

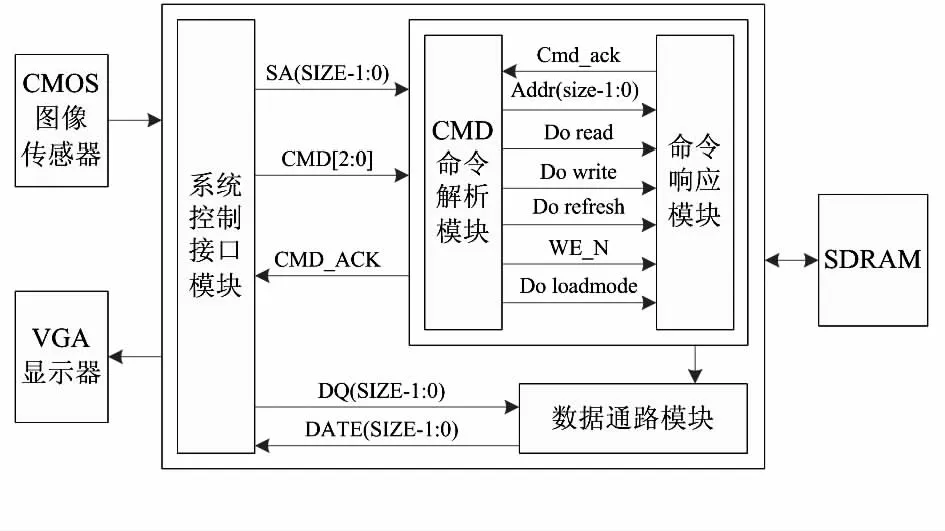

2.3 多端口SDRAM控制器

多端口SDRAM的设计是本实时视频跟踪系统硬件平台的设计重点和难点,利用FPGA的片上资源开辟了多个先进先出(first in first out,FIFO)作为视频图像数据读写的缓存,从而实现多端口SDRAM控制,使其能够从多个缓存向SDRAM芯片进行图像数据的存取。

图5是4_Port SDRAM控制器结构框图[1],通过分析SDRAM存取芯片的各个接口信号、时序要求和工作模式,将该模块内部进一步细化为系统控制接口模块、数据通路模块、CMD命令解析模块、命令响应模块。系统控制接口模块用于接收视频跟踪系统的控制信号,并进行产生不同的CMD命令组合;数据通路模块用于控制视频图像数据的输入和输出;CMD命令解析模块用于接收来自系统控制接口模块的CMD命令并解析成操作指令;命令响应模块用于接收来自CMD命令解析模块的操作指令,进而产生SDRAM的操作。

图5 4_Port SDRAM控制器结构框图

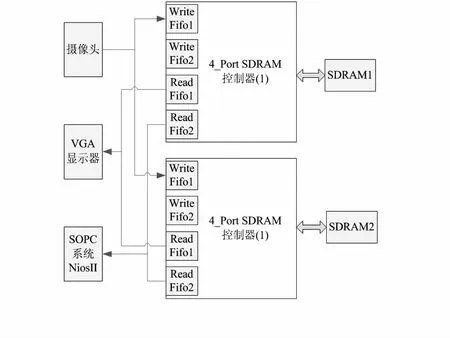

由于本平台既要将采集到的实时视频图像数据送给VGA显示器进行显示,还要送给SOPC的Nios II软核处理器进行视频图像的处理,完成实时视频中运动目标跟踪算法的实现。本系统平台设计用2块SDRAM和2个4_Port SDRAM控制模块来完成视频图像显示和视频图像处理功能。具体而言,将CMOS图像传感器采集到的实时视频图像数据分成2部分:一部分通过4_Port SDRAM控制模块1的写FIFO1写入10位R数据和高5位的G数据到SDRAM1存储芯片中;另一部分通过4_Port SDRAM控制模块2的写FIFO1写入低5位G数据和10位B数据到SDRAM2存储芯片中。VGA显示器通过读4_Port SDRAM控制模块l的读FIFO1和4_Port SDRAM控制模块2的读FIFO1来进行图像的显示。Nios II软核处理器系统通过读4_Port SDRAM控制模块1的读FIF02和4_Port SDRAM控制模块2的读FIF02来完成实时视频图像处理算法。图6为双4_Port SDRAM控制模块设计框图。

图6 双4_Port SDRAM控制模块设计框图

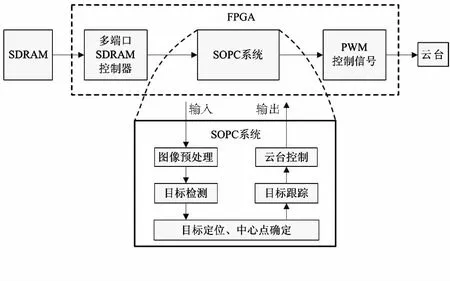

2.4 SOPC搭建

本视频跟踪系统硬件平台设计中SOPC完成的功能是通过多端口SDRAM控制器从SDRAM存储芯片中读取采集到的实时视频帧图像数据,并对视频帧图像信息进行预处理,进而完成运动目标的检测、定位跟踪算法,并通知云台控制模块驱动云台步进电机对运动目标进行跟踪,从而使摄像头随着跟踪目标的移动而转动。图7为SOPC系统图像处理流程。

图7 SOPC系统图像处理流程

一个SOPC的搭建由CPU、用户自定义的外设、标准外设、存储器接口等部分组成。SOPC Builder可以选择和自定义系统模块的各个组件和接口,用户可以简单方便地利用SOPC Builder将处理器、存储器以及其它外设模块连接在一起,构成完整的系统。其中已经包含了Nios II软核处理器和一些常用的外设接口模块,用户也可以根据需要设计自己专用的接口模块。构建SOPC系统的主要步骤如下[1]:

1)首先,对目标FPGA和系统时钟进行设置,本视频跟踪系统设计采输入时钟为50 MHz,通过内部锁相环产生100 MHz的SOPC时钟;

2)根据实际应用要求和目标FPGA中的器件约束(逻辑资源)条件,在SOPC Builder可用元件类表中双击Nios II Process添加Nios II软核处理器;

3)添加SRAM控制器和片内存储器,处理器系统至少要有一个存储器用于数据和指令;

4)添加JTAG_UART和PLL,JTAG_UART用于PC机与Nios II系统串行通信,PLL用于时钟倍频;

5)添加PIO和系统ID,通过PIO输出有序的矩形脉冲,控制2个步进电机实现正转和反转功能;

6)分配外设基地址和中断优先级;

7)生成Nios II系统。

2.5 云台电机驱动器

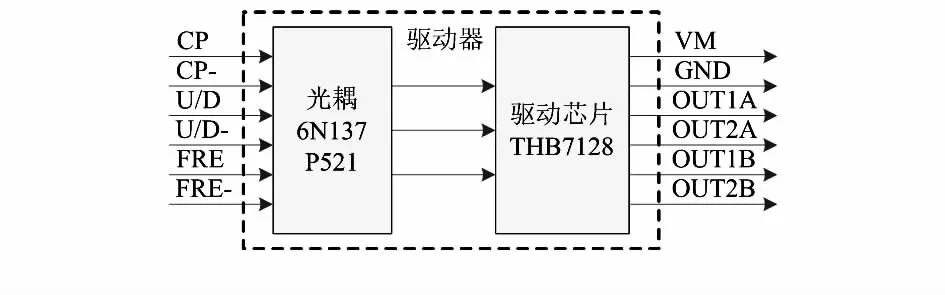

云台是视频跟踪系统的重要组成部分,是固定摄像机的支撑设备。本平台系统中,云台由2台57型两相4线混合式步进电机构成,分别实现水平和垂直方向的转动,以确保被跟踪目标始终处于监控画面的中心。步进电机的运行需要有脉冲信号和驱动器,SOPC输出的PWM控制信号通过驱动电路送达步进电机的每一相绕组,即可驱动步进电机运行。图8为云台电机系统工作框图。

图8 云台控制电路系统框图

驱动器设计的好坏关系到步进电机能否正常稳定工作,THB7128是一种专业的两相步进电机驱动芯片,它内部集成了细分、电流调节、CMOS功率放大等电路,配合简单的外围电路即可实现高性能、多细分、大电流驱动。适合驱动42,57型两相、四相混合式步进电机。图9为驱动器电路结构图。

图9 驱动器电路结构图

3 平台实现验证

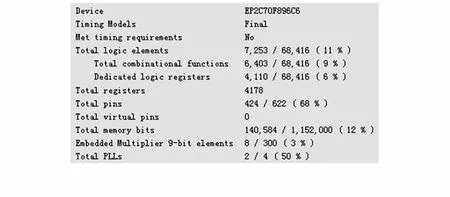

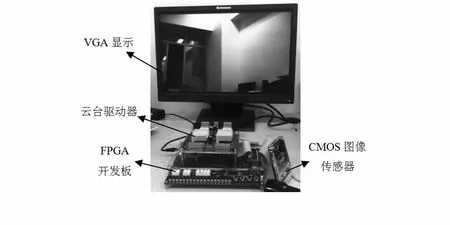

该平台在Altera EP2C70 FPGA开发板上实现,视频图像由外部CMOS图像传感器采集,处理完的图像数据由VGA实时显示,最高支持像素为1 600×1200的分辨率(100 MHz),云台驱动器采用THB7128芯片。图10为该系统FPGA硬件资源使用情况。

图10 系统平台FPGA硬件资源使用情况

为验证该平台Nios II软核处理器的正常工作,在Nios II 8.1 IDE 软件开发工具中编写了一段测试LCD显示程序,代码如下所示:

void task1(void* pdata)

{

while (1)

{

printf("Hello uCOS-II/n");

OSTimeDlyHMSM(0,0,3,0);

}

}

系统平台执行完上述代码后,EP2C70 FPGA开发板LCD显示器上有如图11所示的软核LCD显示测试结果,可以证明Nios II软核代码成功在FPGA上执行。

图11 软核LCD显示测试

为验证平台Nios II软核处理器能控制CMOS图像传感器对视频图像的实时采集,使用C语言编写了一段测试图像采集和显示程序,其中CMOS初始化代码主要如下:

∥setup CMOS

IOWR(CMOS_IF_0_BASE,4,0x00800860);

maxaddr=(640*512—128)*4;

IOWR(CMOS_IF_0_BASE,7,maxaddr);

IOWR(CMOS_IF_0_BASE,1,0x00800880);

IOWR(CMOS_IF_0_BASE,2,&buffer1);

length=128*4;

IOWR(CMOS_IF_0_BASE,3,length);

IOWR(CMOS_IF_0_BASE,6,0x0001);

软硬协同编译完成并且下载至FPGA开发板后,实时图像采集与显示结果如图12所示。

图12 实时图像的采集与显示

以上验证实验成功证明了视频跟踪系统硬件平台中纯硬件逻辑模块和SOPC系统的正常运行,为接下来Nios II软核处理器大型跟踪控制算法的移植打下了坚实基础。

4 结 论

实时视频跟踪因其数据量大、算法复杂、稳定性要求高等因素而成为一个难题,目前嵌入式平台一般由ARM,DSP实现,随着各种视频质量的不断提高和压缩格式的不断改进,对图像处理系统运算速度的要求也不断提高,其实时性、并行性、稳定性都很难满足。本文提出的基于FPGA实时视频跟踪系统硬件平台,具有速度快、开发难度低、可重构性好、成本低等优势,必将成为未来视频跟踪系统开发的理想平台。

参考文献:

[1] 姚运城.基于FPGA的嵌入式视频监控跟踪系统研究[D].大连:大连海事大学,2011.

[2] 李月静.基于视频的实时运动目标检测与跟踪系统研究[D].成都:西华大学,2012.

[3] 王 鹏.基于FPGA的实时视觉跟踪系统的研究[D].太原:中北大学,2013.

[4] 刘晓伟.基于FPGA机器视觉的运动目标检测跟踪系统[D].武汉:湖北工业大学,2012.

[5] 吴长江,赵不贿,郑 博,等.基于FPGA的动态目标跟踪系统设计[J].电子技术应用,2010(3):45-50.

[6] 朱建武,李 榕,凌 云.基于FPGA 的目标跟踪系统设计与实现[J].计算机工程,2012,38(5):243-246.

[7] Hsu Yuan Pao,Miao Hsiao Chun,Tsai Ching Chih.FPGA implementation of a real-time image tracking system[C]∥SICE Annual Conference,2010:2878-2884.