基于增加数据宽度的方法提高访存速度

2014-08-07闫庚哲

闫庚哲

(哈尔滨理工大学软件学院,哈尔滨150080)

基于增加数据宽度的方法提高访存速度

闫庚哲

(哈尔滨理工大学软件学院,哈尔滨150080)

低效率的访存操作是限制微处理器性能提高的一个关键因素。因此提高访存速度可以有效改善微处理器的性能。提出了一种基于增加数据宽度的方式来提高访存速度的方法。通过使用多字宽存储器来增加数据带宽,降低失效开销的时钟周期,从而达到提高访存效率的目的。

数据宽度;多字宽存储器;访存速度

1 引 言

输入输出子系统始终是高性能计算机系统中的瓶颈。随着IC制造工艺和RISC技术的发展,电路速度越来越快,指令执行时间越来越短,虽然连接微处理器(MPU)和存储器的I/O带宽也不断增加,但它的增长速度远远赶不上微处理器和存储器本身速度的增长。特别是先进的RISC技术,如超流水、超标量和VLIW在MPU设计中的广泛应用,使得这一矛盾更加突出。为了解决这一问题,常用的方法有:寻找高速元件、采用层次结构、单体多字系统和多体并行系统等[1]。

基于增加数据宽度的方法来提高访存的速度是通过使用多字宽存储器来增加数据带宽,降低失效开销的时钟周期,从而达到提高访存效率的目的。

2 相关知识

在计算机的组成结构中,有一个很重要的部分,就是存储器。存储器是用来存储程序和数据的部件,对于计算机来说,有了存储器,才有记忆功能,才能保证正常工作。存储器的种类很多,按其用途可分为主存储器和辅助存储器,主存储器又称内存储器(简称内存),内存在电脑中起着举足轻重的作用。因此,提高访问内存的速度就显得尤为重要。

2.1 Cache

Cache是计算机中经常遇到的概念,它位于CPU与内存之间,是一个读写速度比内存更快的存储器。当CPU向内存中写入或读出数据时,这个数据也被存储进高速缓冲存储器中。当CPU再次需要这些数据时,CPU就从高速缓冲存储器读取数据,而不是访问较慢的内存,当然,如需要的数据在Cache中没有,CPU会再去读取内存中的数据[2]。

2.2 存储器带宽

存储器带宽(memory bandwidth):单位时间里存储器所存取的信息量,体现数据传输速率技术指标(位/秒,字节/秒)[3]。

存储器带宽决定了以存储器为中心的机器获取信息的传输速度,它是改善机器瓶颈的关键因素之一。

计算方法:带宽=每个存取周期访问位数/存取周期。如存取周期为500ns,每个存取周期可访问16位,则它的带宽为32Mb/s。

2.3 访存时间

失效率与硬件速度无关,用它来评价存储系统的性能非常方便,所以生活中经常使用它。但是,它也容易产生一些误导。一种更好的评测存储系统性能的指标是平均访存时间:

平均访存时间=命中时间+失效率×失效开销[4]

平均访存时间的两个组成部分既可以用绝对时间(如命中时间为2ns),也可以用时钟周期数(如失效开销为50个时钟周期)来衡量。

2.4 访存模式

CPU直接访问的存储器是高速缓冲存储器(Cache)。Cache通常保存着一份内存储器中部分内容的副本(拷贝),该内容副本是最近曾被CPU使用过的数据和程序代码。Cache的有效性是利用了程序对存储器的访问在时间上和空间上所具有的局部区域性,即对大多数程序来说,在某个时间片内会集中重复地访问某一个特定区域。因此,如果针对某个特定的时间片,用连接在局部总线上的Cache代替低速大容量的内存储器,作为CPU集中重复访问的区域,系统的性能就会明显提高。

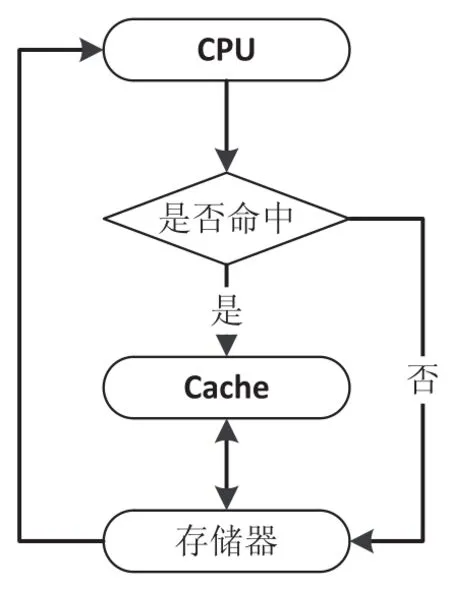

系统开机或复位时,Cache中无任何内容。当CPU送出一组地址去访问内存储器时,访问的存储器的内容才被同时“拷贝”到Cache中。此后,每当CPU访问存储器时,Cache控制器要检查CPU送出的地址,判断CPU要访问的地址单元是否在Cache中,若在,称为Cache命中,CPU可用极快的速度对它进行读/写操作;若不在,则称为Cache未命中,这时就需要从内存中访问,并把与本次访问相邻近的存储区内容复制到Cache中,如图1所示。

3 提高访存速度

3.1 单字宽存储器

由于CPU的大部分访存都是单字宽的,一般的单体单字存储器的一个存储单元存放一个存储字,每个存储周期只能访问到Cache一个存储字。在不具有第二级Cache的计算机系统中,主存的宽度一般与Cache的宽度相同,如图2所示。

图1 CPU访存模式

图2 单字宽存储器

因此其最大频宽就是w/TM。其中设存储字长与访问字长相同都为w位,TM为访问周期,在对存储器连续不间断访问的情况下,CPU获得数据信息的速度也可以达到w/TM。

3.2 多字宽存储器

如果把Cache和主存的宽度增加为原来的2倍或4倍,则主存的频带也就相应地增加为原来的2倍或4倍。对于宽度为2个字的主存来说,上述例子中的失效开销就会从4×32个时钟周期降到2×32个周期,带宽变为每个时钟周期1/4字节。

因此,当主存宽度为4个字时,失效开销就只剩下1×32个周期,带宽变为每个时钟周期1/2字节,如图3所示。

在保证存储容量m*w不变的情况下,可以把存储器的地址数相应减少n倍,则地址数为m/n个。这时可把地址信息分成两部分,其中高部分仍作为存储器的地址去访问存储器(因为存储器的字数减少,访问存储器的地址码可以缩短),低部分则去控制一个多路选择器,从同时读出的n个数据中选择一个数输出。

图3 多字宽存储器

4 对增加数据宽度提高访存速度的分析

此方法会增加CPU和存储器之间的连接通路(通常称为存储器总线)的宽度。

由于CPU访问Cache仍然是每次访问一个字,所以CPU和Cache之间需要有一个多路选择器,而且这个多路选择器可能会处在关键路径上。采用第二级Cache可以解决这个问题。这时可让第一级Cache的宽度为一个字,而在第一级Cache和第二级Cache之间放置一个多路选择器,这样它就不在关键路径上了[5]。

单体多字并行存储器的优点是实现简单,不足则是访问冲突概率略大。访问冲突主要来自以下几个方面:①取指令冲突。②读操作数冲突。③写数据冲突。④读写冲突。前两种冲突容易解决,后两种冲突的解决比较困难。从存储器本身看,访问冲突产生的原因是地址存储器和控制逻辑只有一套,如果有n个独立的数据寄存器和n套读写控制逻辑,后两种冲突就自然解决了,前两种冲突也会有所缓解。

5 结束语

提高访存速度的方法有多种,如:寻找高速元件、采用层次结构、单体多字系统和多体并行系统等,但是增加数据宽度提高访存速度是最简单的方法之一。

通过使用多字宽存储器来增加数据带宽,降低失效开销的时钟周期,从而达到提高访存效率的目的。

[1]张福新.微处理器性能分析与优化[D].北京:中国科学院研究生院,2005.

[2]H Galand.微处理器系统设计导论[M].西安:陕西科学技术出版社,1981.

[3]唐轶轩.面向多线程应用的Cache优化策略及并行模拟研究[D].安徽:中国科学技术大学,2012.

[4]Myers GJ,Budde DL.The80960 Microprocessor Architecture[M].New Jersey:Wiley-Interscience,1988.

[5]李功明.片上多处理器体系结构中Cache一致性模型研究[D].安徽:中国科学技术大学,2013.

Im provement of Memory Access Speed Based on Data W idth Increase

YAN Geng-zhe

(School of Software,Harbin University of Science and Technology,Harbin 150080,China)

The low efficiency ofmemory access operations is a key factor to restrictmicroprocessor performance,so,increasing the speed of memory access can effectively improve microprocessor performance.This paper presents an approach based on data width increase to improve the speed of memory access.The multi-word wide memory is used to increase data bandwidth and reduce failure overhead clock cycles,so as to improvememory access efficiency.

Data Width;Multi-word widememory;Memory access speed

10.3969/j.issn.1002-2279.2014.06.022

TP393

:B

:1002-2279(2014)06-0078-02

闫庚哲(1993-),男,黑龙江哈尔滨人,本科,主研方向:软件工程。

2014-02-24