基于FPGA的任意波形发生器设计探究

2014-07-19徐宇宝张晓东

徐宇宝,张晓东

(皖西学院 机械与电子工程学院, 安徽 六安 237012)

基于FPGA的任意波形发生器设计探究

徐宇宝,张晓东

(皖西学院 机械与电子工程学院, 安徽 六安 237012)

本文对 FPGA芯片实现的DDS结构中数字部分与接口部分进行了设计,将ROM改成RAM,可以实现对波形数据的更新.在对单片机控制的基础之上,通过DDS技术的运用并利用FPGA芯片.以DDS模块为核心的任意波形产生系统的形成得以实现.波形种类齐全、带宽高、频率分辨率高等是这种波形的主要特点,这是这些特点的存在,可以使得信号的调相功能得以实现.

DDS;FPGA;RAM;任意波形发生器

1 引言

当前社会信息技术发展迅猛,人们对于信息的交换(也就是通信)依赖性也越来越高,在这种背景下,提高通信的质量变成非常迫切的事情.想要提高当今通信的质量,就需要在通信的过程中着手,信号的发生、信号的传输和信号的处理是通信的几个主要过程,但是最重要的过程是信号的发生,如果没有可以进行利用的信号产生,那么信号的传输和信号的处理也都变的毫无意义[1].想要产生好的信号源,就需要有好的信号发生源,这样可以降低在信号传输过程和处理过程中发生错误的概率,从源头上避免信号发生阶段的错误,就可以减少信号接收端出现错误的情况.因此,需要我们有一个技术质量非常高的信号发生器,基于 FPGA的任意波发生器就是很适合的.

2 方案选择

当前可以实现可变频信号的方法非常多,比如改变传统 LC震荡电路中电感的值,就可以产生出不一样的频率值,但是这种方法却存在着输出频率不准确,带宽不足等缺点.还有一种方法就是晶体震荡电路,通常人们习惯称之为晶振,在晶体电路中晶体决定着频率,在以往人们通过实验得出它的频率稳定度可以达到 10﹣6量级,这样我们就不需要担心频率输出不稳定问题,但是又一个难题摆在了我们面前,在晶体电路中晶体决定着频率,如果不能很好地制作晶振,就会导致频率被固定,不可以进行调整,这样就只能产生一种单一频率的信号,这肯定是不符合信号实用性要求的.通过以上分析,我们可以看出这两种方法都不是很好,但是不必担心,随着当前电子技术的发展的提高,以及在制作大规模集成电路工艺上的进步,出现了新的DDS技术,这为我们提供了新的选择[2].

3 DDS 工作原理

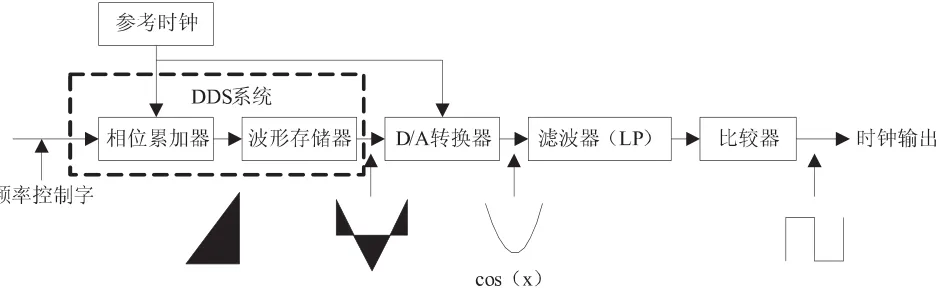

DDS工作原理如图一所示.

图1 基本DDS结构原理图

相位累加器是 DDS技术的核心,它的作用就和一个计数器相似,当一个时钟信号到来,就可以使相位累加器的输出得到增加,增加的是一个步长的相位增加量,如图1,频率控制字决定了相位增加量的大小.在储存器中有通过数据表形式保存的信号波形相位,它包含着相位信息,也就是待产生信号的一个周期的幅度.相位累加器中输出信号的信息可以从数据表中读出,这种信息是当前相位累加器输出信号相位值对应的幅度数据,并将这种数据通过DAC的转换功能变成模拟信号波形进行输出,相位累加器通过线性相位累加的方式进行叠加,当达到满量程时就可以进行一次计数溢出,输出信号的频率受溢出速率决定.想要使相位累加器有更高的溢出率,就要调高频率控制字内的相位增加量,这样才可以得到更高的信号输出频率.

4 FPGA 实现的波形数据接收模块设计

基于 DDS的基本原理并通过 FPGA实现的任意波发生器,想要任意波的任意性得以实现必须改变 DDS的基本结构,可以通过将 ROM改写成RAM,这样可以利用 RAM的接口电路实现波形数据的更新,这样就可以使任意波发生器的任意性得以实现[3].FPGA中实现的各电路中的模块连接如图2所示,我们结合图 2来对控制部分、相位累加器、波形RAM等进行分析.

图2 FPGA实现的电路示意

4.1 控制模块的设计

DDS于单片机的接口问题需要通过控制模块来解决,在 FPGA的实现中,对3个模块进行了主要设计,分别是输入寄存器模块、地址选择模块、地址锁存模块.这三个模块各有各的作用,接受单片机频率控制字需要通过输入寄存模块来完成,单片机在FPGA各模块进行工作时依据不同地址的选择在地质选择模块内完成,对于单片机PO口地址和数据线复用问题的解决是在地址锁存模块内完成.在进行输入寄存模块的设计的时候,DDS要采用32位的相位累加器,单片机要选择8位的,这样单片机可以分四次写入四个字节来形成一个频率控制字.而地址选择模块的设计相对输入寄存模块的设计就简单许多了,直接选用一个3—8的译码器就可以使地址选通的功能得以实现.因为地址锁存模块的PO口既是数据口也是地址总线的低8位,所以要选用51系列单片机作为单片机,在使用时就可以实现地址信号从分时复用的地址/数据总线的分离[4].

4.2 相位累加器的设计

结合FPGA本身的特性,并满足任意波发生器的要求,即频率分辨率达到10MHz,输出的最大频率要达到15MHz,所以要采用40MHz,32bit的相位累加器的系统时钟来设计任意波发生器.本设计在采用EP1C3T144C8的FPGA器件,并直接用32bit累加器的时候,通过仿真实验,可以看出这种情况下只能使系统时钟最大达到约25MHz,不能达到40MHz,这肯定是和我们的设计不相符的,所以我们必须对相位累加器的结构进行改进,使之能够达到我们要求的更高的工作速度.想要达到更高的工作速度,我们可以用一种在时序电路设计中常用的设计方法,就是流水线结构法,通过流水线结构来实现的累加器运行过程是这样的,现将一个位数很长的加法拆分成N比较短的加法,并在N个时钟周期内做完这个过程,然后进行结果的输出,在采用这种流水线结构后使得加法器的字长变的更短了,这对于FPGA提高其工作频率具有重大意义[5].

下面我们来详细的对累加器流水结构的实现进行分析,将一个字长为N的累加器进行拆分,分成m个n位的累加器来工作,这样拆分后的累加器的字长就变为了N=m×n.因为这m个n位的累加器之间是存在进位关系,所以这就造成了在一个周期内全部完成,这样的情况下就可以运用流水的思想,将高位的累加器晚一个时钟周期做累加,其对于低位累加器是延时的,这样低位累加器在高位累加器进行累加的时候已经计算出了进位值,在低位累加器进行结果的输出时也要延时,这是为了保证和高位累加器的结果同时输出,这样也可以使结果输出的准确性得到保证.这个过程最终得出的结果是,一个值在进入累加器以后需要在m个延时以后才可以使得高位累加器计算出结果,在高位累加器计算出结果之后才可以完成最后的结果输出.这样通过m级延时才可以得到结果,但是不会对DDS相位累加器的工作产生影响,除了在过程中的m个延时以内,结果不会有变化,但其工作速度却得到了很大的提高.通过流水线结构对相位累加器进行设计的时候,使m=8,n=4,这样就可以使其工作效率达到最高值,大约是70MHz,超过了40MHz,符合我们的设计要求.

4.3 波形RAM的设计

在进行波形RAM设计的时候,要先使波形RAM的深度和字长得到确定,波形RAM的字长应该和任意波发生器设计中DAC选择的字长一样,都是 8位的,波形RAM选择的地址线位数和相位累加器的输出最高位数一样,也是12位的.

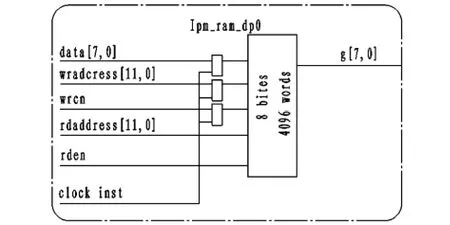

面对普通的DDS和任意波发生器不同,还要使波形RAM满足设计要求,即具有两个读写的端口这一情况,我们可以运用2套地址系统来更好地进行RAM内容的更新(也就是RAM的写操作)和输出波形幅度量(也就是RAM的读操作).我们根据FPGA的特点,可以选择EP1C3T144C8芯片内部的双口 RAM来完成这个功能的实现.双口 RAM示意图如图3所示.

图3 双口RAM示意

因为芯片内部的双口具有 2组地址线,也就数读地址和写地址,所以数据线也有俩组,就是读数据线和写数据线,这样对于完成波形 RAM的设计相对来说就简单许多了,将写数据线、写地址线与单片机的数据线、地址线进行连接,这样就可以通过单片机来实现RAM数据的更新工作.将读地址线与相位累加器的输出相连,将读数据线与数据输入相连,这样就可以在读数据线上进行波形幅度量化数据的输出.

5 波形数据的生成及处理

5.1 波形数据的生成

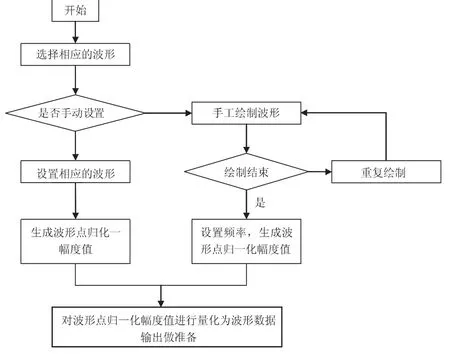

波形数据的生成总体流程图如图 4所示.因为下位硬件系统的波形RAM是波形点的幅度数据最终的储存位置,由 2.3波形 RAM的储存深度设计为 4096个单元,这样的每个单元的字长是 8bits,这样对于一个周期内的 4096个采样点来说,要将这些个波形点的数据进行量化,最终要量化为0~255的整数.

5.2 波形幅度数据及频率参数的处理

通过上述的过程可以使波形的 4096个点的数据生成,并进行储存,但是由于 4096个点的波形数据是双精度的,所以必须对这些数据进行处理来满足其传输和储存的需要.因为在另一个操作界面上,对信号输出频率值也是双精度类型的,因此对于频率参数也要进行数据处理.

图4 波形数据生成总体流程图

6 总结

本文对基于 DDS技术与 FPGA的任意波发生器的波形数据生成方法进行了研究,对DDS工作原理进行了简单的介绍,对 FPGA实现的波形数据接收模块设计进行了分析,主要包括控制模块的设计、相位累加器的设计、波形 RAM的设计三种方法,这样对于波形发生器性能的提高具有很大的意义.当前我国对于任意波发生器的研究生产还没有真正形成产业链,当期国内的成熟产品大多是PC仪器插片,独立仪器相对来说还很少,我国的任意波发生器比国外同类产片还存在相当大的差距,因为,进行基于 FPGA的任意波形发生器设计研究是非常急迫的事情.我们要通过对国外先进技术的研究分析来改进我国的技术,这样才可以尽快的使我国技术落后的状况得到改善.

〔1〕邓耀华,吴黎明,张力锴.基于FPGA的双DDS任意波发生器设计与杂散噪声抑制方法[J].仪器仪表学报,2009,30(11):2255-2261.

〔2〕何存富,周进节,郑阳.超声导波任意波形脉冲激励源的设计与实现[J].测控技术,2011,30(10): 96-102

〔3〕韩旭,郑磊.基于FPGA的任意波形发生器的设计与实现[J].电子测量技术,2013,11(7):824.

〔4〕张严,洪远泉.基于FPGA的任意波形发生器设计与研究[J].现代电子技术,2013,34(10):157-162.

〔5〕唐建东.基于FPGA的任意波形发生器设计与实现[J].电子技术,2010,9(5):37-39.

TN9ll

A

1673-260X(2014)08-0037-03