引导式讨论在小班研讨教学中的应用

2014-06-19袁小坊邝继顺

袁小坊 邝继顺

摘要:当前本科小班研讨课面临学生学习习惯的改变、学习兴趣的提升等问题,文章介绍数字逻辑教学中的两次讨论课设计,采用引导式讨论法,设计多个彼此关联的小问题,交由学生课后思考,教师采用图形、仿真与更形象的口头表述引导学生积极地参与讨论,帮助学生更快地突破知识理解上的盲点和障碍。

关键词:小班研讨:引导式讨论;锁存器;触发器

0 背景

小班研讨课是世界一流大学教学实践中广泛采用、行之有效的一种重要教学组织形式。目前国内大学也在极力推广这种教学模式,希望通过这种教学方式给予学生求知动力,激发他们的学习兴趣与探索精神,培养和提升学生自主学习、批判分析、创新思考、交流表达和团队合作等能力,全面提升学生的学术素养和综合能力。但任何一种好方法的应用都必须因地制宜,考虑实际情况与应用环境,否则很难达到预期目的,甚至可能得到相反的结果。

1 小班研讨课面临的问题

1.1 学习习惯

首先面临的一个难点是学生学习习惯的改变。大班授课中,学生基本上是被动的,而在小班授课中,要求学生变得主动。中国学生在长期应试教育中形成的被动学习习惯是一个很大的障碍,在实际的教学过程中,一个普通小班中能主动发言并上台讨论的学生只有那么几个,大多数学生都羞于表现,即使勉强上台也是应付式的,与老师的设想相差很大。中国学生的这种特点甚至让美国大学也感到头疼,由于来自中国的留学生越来越多,美国大学某些课程班的非中国学生纷纷逃离,因为“课堂上太安静了”,对于美国大学的教师来说这是一种挑战,“如何影响他们?如何让他们参与?这都是伤脑筋的事。”在中国大学里,某些精英班级的学生主动性比较好,但普通班级的学生就要差很多,况且改变习惯不是一天两天就能完成的,教师面临的挑战很大,

1.2 学习兴趣

其次面临的是学生的学习兴趣问题..学生的学习兴趣同时还受到社会的影响,应试教育、社会压力与功利性学习目的大大束缚了学生的思维、胆量与想象力。同样的年纪,16岁的爱因斯坦畅想着与光一起旅行,而我们的学生则埋身在一遍遍复习与考试之中,为高分而奋斗。现在的大学生学习的目的最低就是应付考试、拿文凭,最高也不过是找个好工作、当个旱涝保收的公务员或考研。那种与生俱来的好奇心与探究兴趣早已被压抑,仰望星空的美丽终抵不过现实的骨感,校园本身不清净,学生亦难以安心。在小班研讨课中,教师肩负着重新唤醒学生的探究兴趣的责任,这一过程也不是一蹴而就的。

1.3 时间与情绪

学生的时间与情绪也是不得不面临的问题。目前学生的负担还是蛮重的,随着课程改革的进行,除上课外,学生面临着大量的课后作业、课前研讨准备、课后实验,学生还是有一些怨言的,对新教学模式的不适应也会使学生产生焦虑情绪。如果学生总是处于被动且疲于应付的状态,学习效果自然会大打折扣。

1.4 知识基础

另外,受知识基础与知识获取能力的限制,大部分低年级学生的思维还不容易展开,难以独立进行有一定深度的问题研讨。

2 引导式讨论教学法

在分析当前小班研讨教学所面临问题的基础上,我们在具体的小班研讨教学过程中探索了不同的教学方式,引导式讨论方法是其中的一种。从教学效果来看,学生感觉收获较大,效率也较高。下面,我们以数字逻辑教学中的两次讨论课为例来进行说明。

时序电路基础部件是数字逻辑教学中的一个难点,大部分学生都会有疑问:为何没有任何记忆功能的组合电路经过设计后能变得有记忆功能,且能在时钟脉冲的控制下进行工作?锁存器(latch)与触发器(flip-flop)有什么区别?脉冲触发器与边沿触发器有什么区别?即使反复看教材,仍然很困惑。

根据大班授课时学生所感到疑惑的知识点,我们采用引导式讨论方法设计了两次讨论课。引导式讨论方法就是根据当前教学的情况,设计多个小问题,这些问题彼此关联,切合学生所面临的难点,交由学生课后思考,小班研讨时,在教师的引导下学生逐一对问题进行讨论,提出自己的观点,然后由老师总结,并给出正确的结果。

2.1 时序电路第一堂讨论课

第一堂讨论课要解决对基本概念、基本部件机制的透彻理解,设计的问题如下。

1)时序电路记忆部件类型。

请解释以下名称的区别与关系。

国内教材中:基本触发器、电平触发器(钟控触发器)、主从触发器(脉冲触发器)、边沿触发器。

国外教材中:基本锁存器、带控锁存器、脉冲触发器(Pulse-Triggered Flip-Flop)、边沿触发器(Edge-Triggered Flip-Flop)。

2)什么是“空翻”,如何解决?

3)为什么主从SR触发器会有“1—捕获”错误?

4)为什么主从SR触发器是脉冲触发而不是边沿触发?

5)主从D触发器为什么没有“1—捕获”错误?

6)主从D触发器一定是边沿触发器?

问题1)主要源自于以前国内教材把锁存器与触发器当成一个东西,学生看相关资料时会有疑惑,在国外教材中,锁存器与触发器是严格区分的:

However,some textbooks and digital designers may(incorrectly)use the name“flip-flop”for a device that we call a“latch”.

Flip-flop differs from latches due tO the triggering method used.Latches are not pulse or clock edge triggered and flip-flops are.

In this sense,the latch is transparent,since itsvalue can be seen from the outputs while the controlinputis 1.endprint

锁存器是最基础的存储器件,是触发器的构成核心。

The most basic storage elements are latches,from which flip-flops are usually constructed.

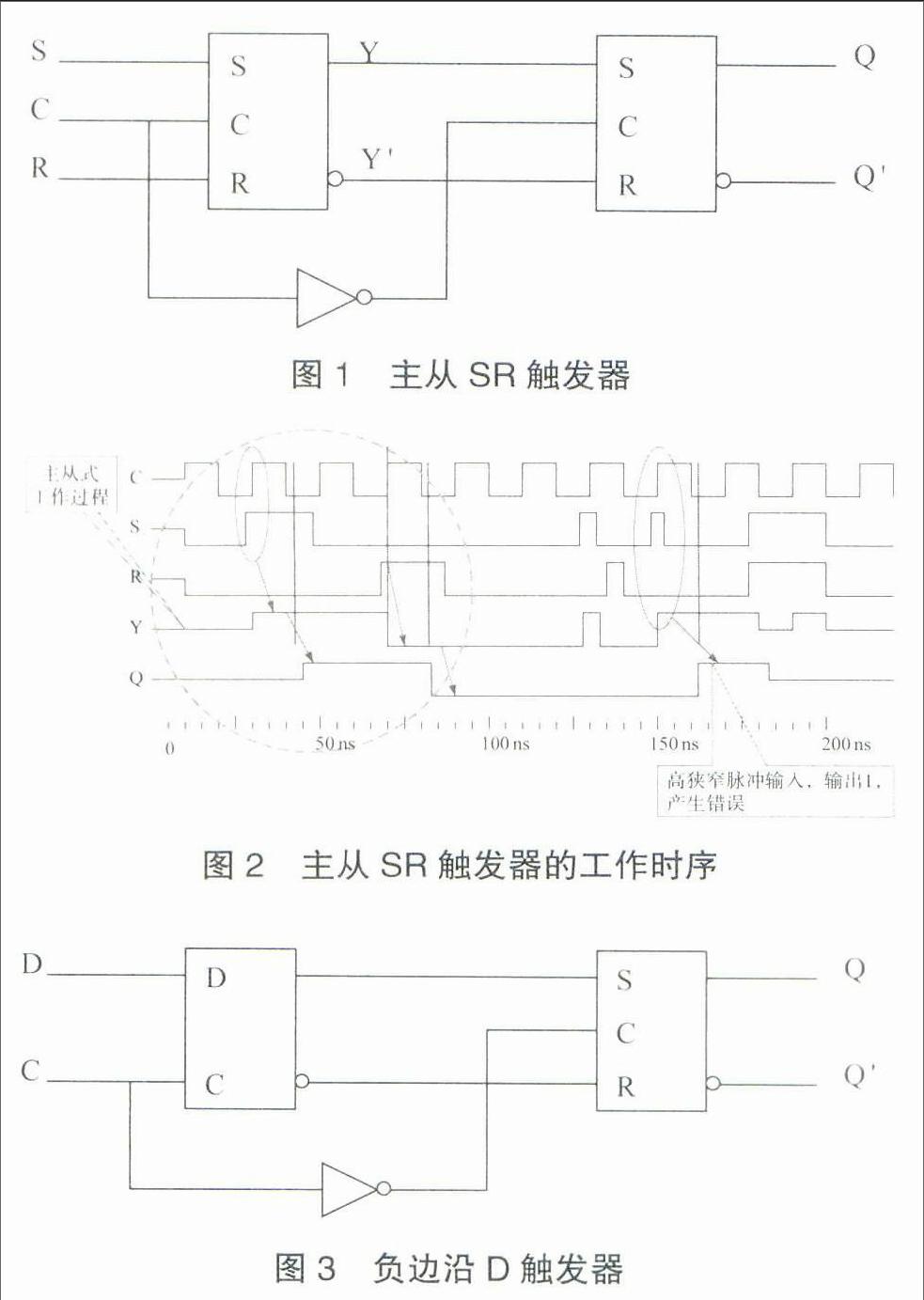

问题2)考查学生对“空翻”的理解,图1采用主从SR触发器解决一个时钟周期内输入信号的多次改变会导致输出信号多次改变的问题。

问题3)与问题4)可以说是一个问题,主从SR触发器解决空翻问题,但存在“1—捕获”错误。如图2所示,当在一个时钟脉冲的高电平前部,S端输入了一个高电平干扰窄脉冲,会使Y置高电平,即使窄脉冲消失后,Y仍然会保持高电平,最后导致时钟脉冲变为低电平时,Q端会输出高电平,这是我们不希望产生的结果。这说明主从SR触发器的抗干扰能力有缺陷,同时我们也看到主从SR触发器的输入在时钟高电平期间的变化可能影响到输出,所以称之为脉冲触发器,有的主从触发器会产生“0—捕获”错误,它们都属于脉冲触发器,而非边沿触发器。

问题5)与问题6)实际上也是一个问题,图3中的负边沿D触发器也是主从结构,但由于主D锁存器的特点,边沿D触发器可以避免“1—捕获”或“0—捕获”的错误。边沿D触发器在脉冲边沿变化的一瞬间,输出只与离时钟边沿变化最近的一次输入有关,所以称为边沿触发器,具有更强的抗干扰能力。

综合以上4个问题的答案,就可以解决学生心中一个最大的疑惑:为什么说脉冲触发器的输出与脉冲整个正电平期间的输入变化有关系,而边沿触发器则不是:

“The logic symbol for the master/slave S-Rflip-flop does not use a dynamic-input indicator.because the flip-flop is not truly edge triggered.”“Flip-flops with this kind of behavior are sometimescalled pulse-triggered flip-flops”

2.2 时序电路第二堂讨论课

在第一堂讨论课的基础上,第二堂讨论课帮助学生更深入地思考问题,并开阔学生的眼界,设计问题如下:

1)是否只有主从D触发器才是边沿D触发器?

2)是否还有其他类型的边沿D触发器?

3)边沿触发只有上升沿与下降沿模式吗?

4)什么是单一时钟?

5)触发器定时:建立时间、保持时间

6)有了触发器后,锁存器是不是就没有用了?

问题1)与问题2)引导学生思考,实现边沿触发器的方法不是只有一种,由于教材中只给出了主从结构边沿D触发器的例子,所以在讨论课中分别给出另外两种实现方式,并由学生理解讨论期中的实现机制。

图4是由CMOS逻辑门和CMOS传输门组成的主从式D触发器。该触发器利用4个传输门交替地开通和关闭,将触发器的触发翻转控制在CP下降沿到来的一瞬间,并接收CP下降沿到来前一瞬间的D信号。该电路为主从结构,具有边沿触发器的特性。

图5是维持阻塞D触发器。由于置1维持线与置0阻塞线的作用,当触发器处于状态1时,即使输入D由1变为0,触发器仍保持状态1。同理,当触发器处于状态0时,由于置0维持线和置1阻塞线的作用,即使输入D由0变为1,触发器仍保持状态0不变。这样,就保证触发器在时钟信号作用期间只变化一次,从而有效地杜绝了“空翻”,且没有“1—捕获”或“0—捕获”的错误。维持阻塞D触发器的机制较难理解,采用Proteus做仿真电路并逐步演示,学生很快就理会出其中的奥秘。

通过将这两个电路与教材中的电路进行比较,学生讨论之后,很快得出结论:维持阻塞D触发器的成本是最低的。

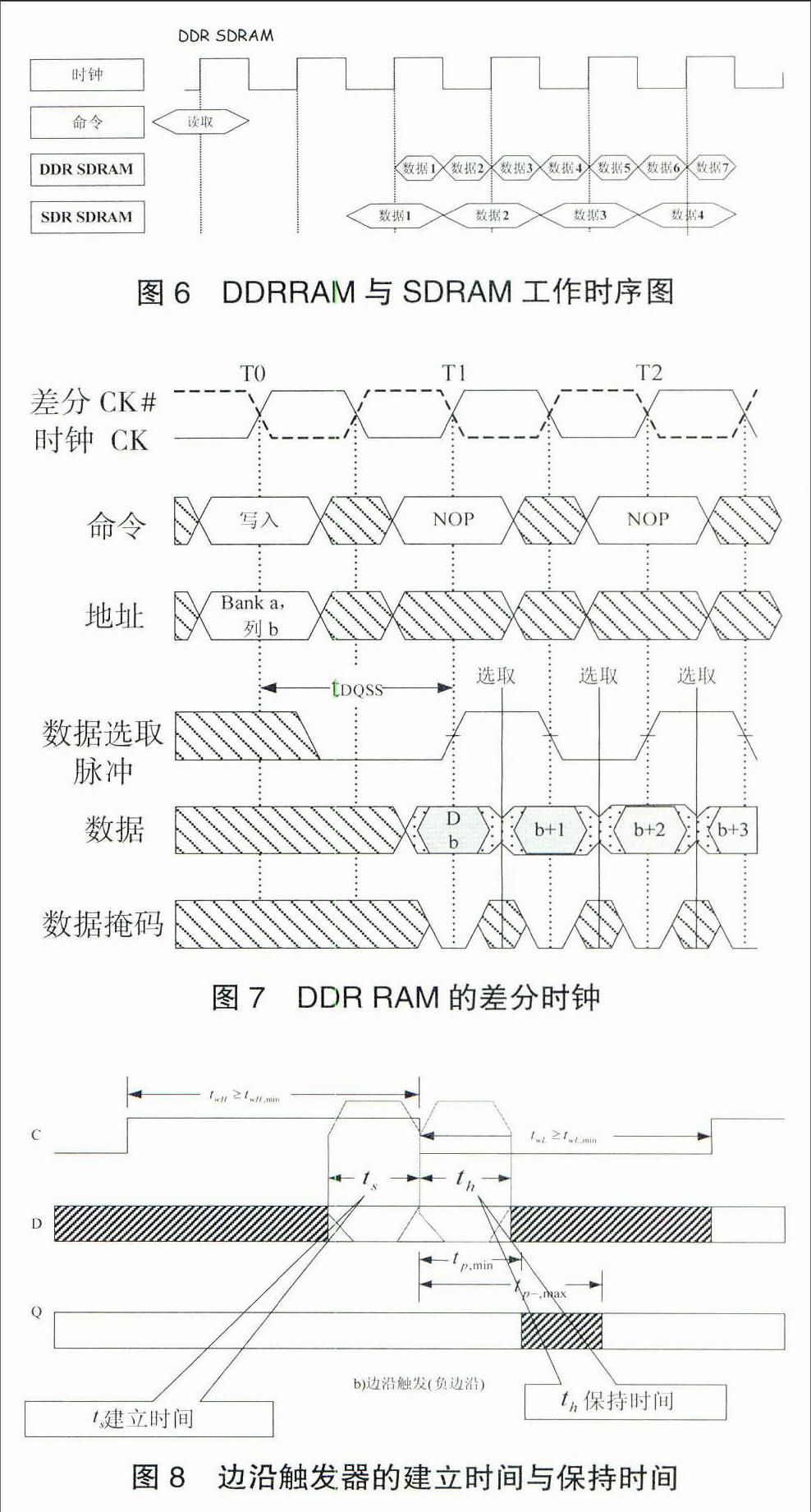

问题3)引导学生思考边沿触发的应用方式。教材中给出的电路或采用上升沿触发,或采用下降沿触发,近十多年随着技术的发展,芯片设计上已经有了很大的进步,比如DDRRAM(DoubleData Rate SDRAM)就同时采用了上升沿与下降沿都传送数据的方法,在相同工作频率下,数据传送率提高到SDRAM的两倍,如图6。

问题4)引导学生思考一个时序电路中是否只能有一个时钟信号?教材中的例子都是单一时钟的。图7中,DDR中采用了差分时钟CK#,差分时钟是DDR的一个必要设计,但CK#的作用,并不能理解为第二个触发时钟,而是起到触发时钟校准的作用。由于数据是在CK的上下沿触发,造成传输周期缩短了一半,因此必须要保证传输周期的稳定以确保数据的正确传输,这就要求CK的上下沿间距要有精确地控制。然而因为温度、电阻性能的改变等原因,CK上下沿间距可能发生变化,此时与其反相的CK#就起到纠正的作用(如果CK上升快、下降慢,则CK#就会上升慢、下降快)。在更复杂的电路中,人们会采用时钟域设计。

问题5)引导学生思考边沿触发器对建立时间与保持时间的要求。

问题6)引导学生结合第一节讨论课的内容,回想并思考。锁存器是构成触发器的核心部件,由于锁存器有缺点,是不是锁存器就不能独立使用了呢?实际上锁存器相对触发器来说,有它的优点:器件简单、面积小、速度快,所以在CPU的设计中常采用锁存器,关键是要保证信号的质量。

2.3 课堂反馈

积极参与这两节研讨课的学生基本上能将以上所有小问题都搞清楚,很多同学恍然大悟,他们感叹,以前课后看书,有些地方一大段一大段的,很难看懂,总感觉抓不住要害;研讨课则能激发自己的思维,抓住关键点,往往一下子就找到了感觉,有些同学下课时竟还有意犹未尽之感。

教材上的书面文字受各方面的限制,表达力总还是有限的。不同于大班授课,研讨课中教师可以不受特定教材内容与编排的限制,自由综合相关资料,采用图形、仿真与更形象的口头表述引导学生积极地参与讨论,确实能帮助学生更快地突破理解上的盲点或障碍。教师设计的小问题也能启发学生如何自己去思考、理解教材,如何提问。因为要提高思维能力,首先要学会提问,正如爱因斯坦所说“提出一个问题往往比解决一个问题更重要,因为解决一个问题也许仅是一个数学上的或是实验的技能,而提出新的问题,从新的角度去看旧的问题,却需要有创造性的想象力,而且标志着科学的真正进步”。endprint

3 小班研讨课对教师的要求

引导式讨论中小问题的设计是关键,教师要能体会到学生的难处,设计问题要细致、动中肯綮,视野开阔。鲁迅先生曾说过:“一条小溪,清澈见底,浅就浅吧,一潭污水,谁知道他有多深”。在讨论课中,通过对小问题的逐步讨论、剖析,教师给学生展现的就是一条清澈见底的小溪,学生自然感觉通透清凉。

小班研讨授课模式对于教师来说是一种考验,也是一种成长机会。小班研讨课不同于传统的大班授课,也不同于习题课、答疑课,是一种更接近柏拉图学园(Plato academy)的学习模式,对教师的综合素质要求更高,教师需要摆脱教材内容与编排的限制,自由综合更多的相关资料在与学生的实时互动中,教师动用的资源不仪仪与本教材、本课程、本学科相关,还与他的实践经验、人生阅历、知识视野、人文修养、个人情趣紧密相连。课程就是教师的产品,技术层面创造价格,而品位格调提升价值,一位优秀教帅的课程品格极具个人特性,难以完全复制。正是如此,Bill.Gates才表示“愿意牺牲很多东西云换取Steve.Jobs的品味(I would give a lot to haveSteves taste.)”,其实世上万事皆殊途同归

4 结语

在目前的实际条件下,引导式讨论教学法客观上起到扶着学生前进的作用,也相对减轻了新教学模式下学生的焦虑与不适应。图形、仿真、形象的口头表述以及实时的讨论可突破教材书面文字表现力的局限,更快地帮助学生掌握好知识的难点,提升思维水平,开阔眼界,提高学习效率,教学效果很明显。经过多个学期多门课程的小班研讨训练,学生的各方面能力均有所长进,教学方法也应随之调整,让学生在研讨中担当更主动的角色。当然,大环境不变,仅靠小班研讨课无法解决学生的全部问题。

参考文献:

[1]Bartlett T,Fischer K.中国留学生让美国大学伤脑筋[EB/OL].邱迟,译.http:∥qnck.cyol.com/html/2011-11/09/nw.D110000qnck-20111109-1-23.htm.

[2]Mano M M,Kime c R.逻辑与计算机设计基础[M].4版.邝继顺,译.北京:机械工业出版社,2012:135-146.

[3]Wakerly J F Digital design principles and practices[M].4th ed.北京:高等教育出版社,2009:527-537.

[4]Yarbrough J M.Digital Logic Application and Design[M].北京:机械工业出版社,2002:253-254.

[5]Mano M M,Kime C R.Logic and Computer design Fundamentals[M].4th ed.北京:机械工业出版社,2010:211-218.

[6]佚名.DDR的原理和时序[EB/OL].http:∥www.hackhome.com/InfoView/Article 92586.html.

(编辑:白杰)endprint