嵌入式存储器空间单粒子效应失效率评估方法研究

2014-06-02杨海钢秋小强李天文王新刚

支 天 杨海钢 蔡 刚 秋小强 李天文 王新刚

嵌入式存储器空间单粒子效应失效率评估方法研究

支 天①②杨海钢*①蔡 刚①秋小强①李天文①②王新刚①②

①(中国科学院电子学研究所 北京 100190)②(中国科学院大学 北京 100190)

嵌入式存储器易受到空间单粒子效应(Single-Event Effects, SEE)的影响。该文提出了一种单粒子效应失效率评估的方法,包含了单粒子翻转和单粒子瞬态扰动等效应对嵌入式存储器不同电路单元的具体影响,可对不同存储形式、不同容错方法的嵌入式存储器单粒子效应失效率进行定量评估。该文提出的评估方法在中国科学院电子学研究所自主研制的嵌入式可编程存储器试验芯片上得到了验证,地面单粒子模拟实验表明该文方法预测的失效率评估结果与实验测试结果的平均偏差约为10.5%。

片上系统;嵌入式存储器;单粒子效应(SEE);失效率;评估

1 引言

嵌入式存储器作为片上系统的核心组件,在空间电子系统中得到了广泛的应用[1]。据统计,美国宇航局单个航天器上使用存储器的类型已超过百种[2,3],其中包括通用存储器和可重构存储器等[4,5]。根据用途的不同,存储器的工作模式也多种多样。例如,在高性能计算中使用堆栈等存储形式缓存数据以解决跨时钟域的数据通信;在图像和多媒体处理中使用随机存储器缓存图像、语音和视频等数据,使用只读存储器中的数据实现压缩编解码等;将关键全局控制信号的存储于具有容错能力的存储器中以提高整个系统的可靠性。

空间飞行数据显示,嵌入式存储器易受到单粒子效应(Single-Event Effects, SEE)的影响[6,7],且随着芯片工艺节点的减小,存储单元的错误率(error rate)呈指数趋势增大[8,9]。因此,准确评估存储器的SEE失效率(failure rate)对提高航天器的可靠性具有重要意义。系统设计者可以在设计初期根据预估的失效率数值,结合功耗和性能等参数,对嵌入式存储器的实现形式和工作模式进行选择,并确定系统级加固和飞行器辐射屏蔽等方案。这种方法对于使用大量商业裸片器件、低成本和短开发周期的微小卫星系统尤为有效。

2 嵌入式存储器SEE失效率模型的建立

2.1 已有存储器SEE失效率模型

2.2 嵌入式存储器SEE失效率模型

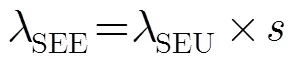

来自Rosetta的实验结果显示,影响存储器的单粒子效应有SET和SEU两种,其余类型SEE的影响可忽略不计[7,17,18]。尚未有研究发现不同电路或不同类型的SEE错误之间具有相互关联,即不同来源的SEE错误之间两两独立,为互斥事件。假设SEE错误的来源共有种,根据相互独立事件的有限可加性,可得式(2)。(SEE)代表了评估对象中第种错误来源导致系统失效的概率。根据电路实现原理可得,嵌入式存储器中的全部SEE错误来源可以归纳为:时钟电路的SET效应、写使能电路的SET效应、输入数据电路的SET效应、输出数据电路的SET效应、复位电路的SET效应、地址电路的SET效应、内部寄存器的SEU效应和内部存储阵列的SEU效应,以上SEE错误来源分别对应式(2)中下标为clk, wr, din, dout, rst, addr, ff和m的因子。

2.2.2电路单元的资源使用数式(3)中与相关的因子代表了嵌入式存储器在某种存储形式下所使用的电路单元的数目,其取值与嵌入式存储器的实现形式有关。

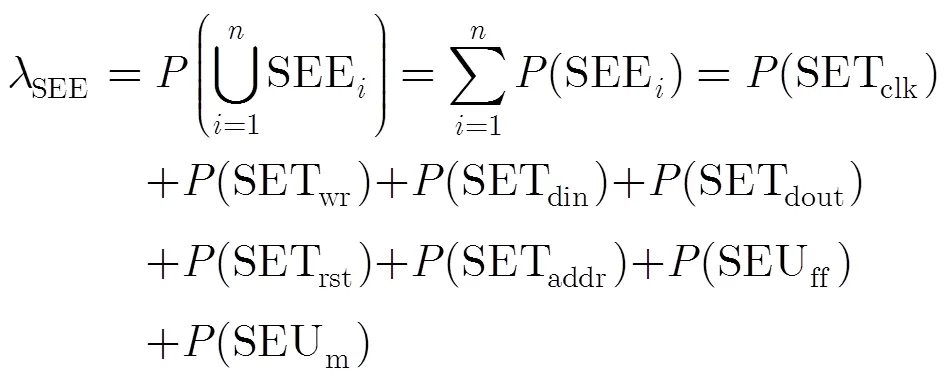

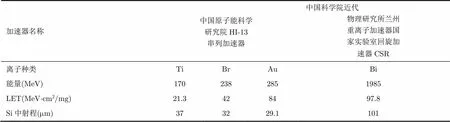

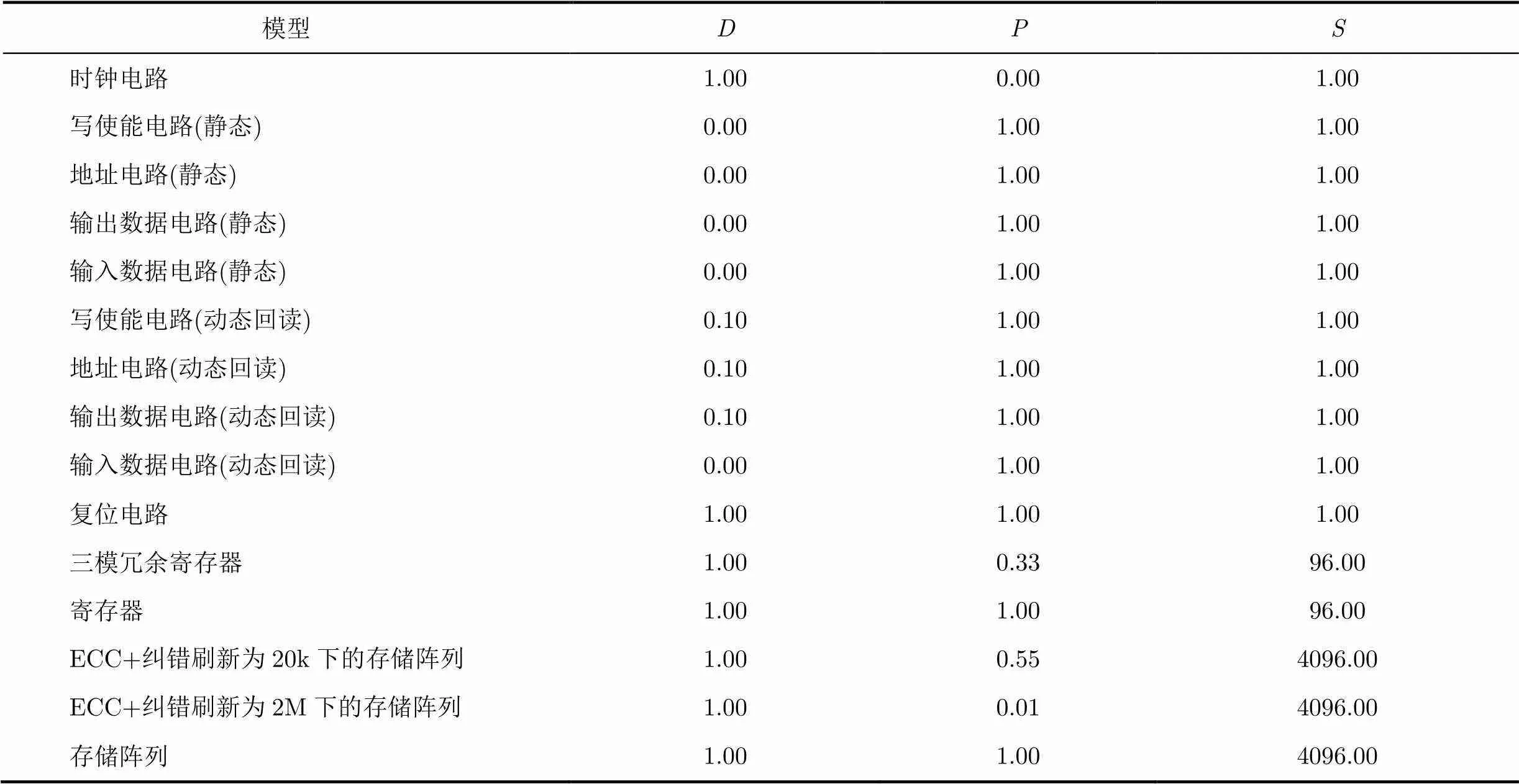

2.2.3错误导致系统失效的概率嵌入式存储器中的SEE错误(error)并不一定会导致最终失效(failure),譬如对于输入数据电路的SET错误,当存储器处于读状态或者不满足时钟触发条件时,就不会造成存储器的输出失效。其取值变化关系如图1和表1所示,其中的横轴为嵌入式存储器的建立时间和保持时间占时钟周期的比重,即(hold+setup) /cycle,其中hold和setup分别代表了嵌入式存储器时序参数中的保持时间参数和建立时间参数,cycle代表应用中嵌入式存储器使用的时钟周期。直线的斜率为零,表示时钟电路、复位电路、寄存器电路和存储阵列的错误导致系统失效的概率相关取值为1,此类电路中任何一个SEE错误都会导致嵌入式存储器的失效。直线的斜率为1,代表了写使能电路、地址电路和输出数据电路的SEE错误发生在时钟沿的建立和保持时间段内,会导致嵌入式存储器的失效。直线的斜率为嵌入式存储器(其代表了应用中写状态占整个工作状态(包括读和写两种状态)的比例),若嵌入式存储器一直为读状态时其取值为零,在此期间其发生的任何SEE错误不会导致系统失效。

图1 错误导致系统失效概率的取值

表1图1中的图示相关说明

直线错误导致系统失效的概率的对应电路 aclk, rst, ff和m bwr和addr cdout和din

使用三模冗余设计时,此因子的取值约为0.33[19]。

3 单粒子辐照实验

3.1 辐照实验环境

3.2 嵌入式存储器单粒子翻转检测测试系统

图2为嵌入式存储器单粒子试验测试系统,包含了待测芯片、检测电路和监测软件三部分。为了能对于不同存储形式和不同容错方案的嵌入式存储器进行SEE失效率评估模型的验证测试,待测芯片选取了中国科学院电子学研究所自行研制的可重构存储器试验芯片,其可被配置实现成多种存储形式,功能与Altera公司的嵌入式可重构存储器M4K[4]兼容。检测电路使用了Cyclone系列FPGA芯片,可提供测试激励、采集数据并将辐照实验结果传输至PC机。监测软件对实验条件进行控制并对实验结果进行处理。

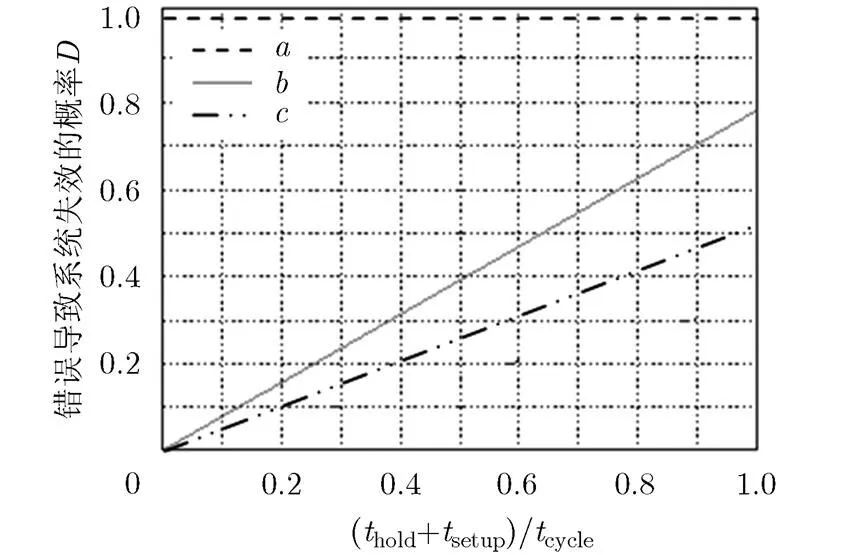

表2离子源特性参数

加速器名称中国原子能科学研究院HI-13串列加速器中国科学院近代物理研究所兰州重离子加速器国家实验室回旋加 速器CSR 离子种类TiBrAuBi 能量(MeV)1702382851985 LET(MeV·cm2/mg)21.3428497.8 Si中射程(µm)373229.1101

3.3 实验内容

3.3.1本征错误率因子的获取

(1)存储阵列本征错误率和复位电路本征错误率的测试 将待测芯片配置为表3中第1种工作模式,根据表4中的模型因子,将辐照实验结果中存储数据的错误个数得出存储阵列的错误率[20]并记录至表5。根据文献[21],计算出复位电路的错误率并记录至表5。

(2)写使能电路、输出数据电路和地址电路的本征错误率测试 将待测芯片配置为表3中第2种工作模式,将嵌入式存储器试验芯片中的存储阵列取值固化,排除存储阵列发生SEE错误而导致系统失效的可能。将时钟频率设置为20 MHz,辐照实验中动态读出ROM的值并与已知数值进行比较,得出写使能电路、输出数据电路和地址电路的错误率并记录至表5。

表3单粒子实验中存储器使用的工作模式

工作模式序号端口模式字宽模式时钟使能时钟模式字节使能上电清零输出模式错误自修复能力 1单端口512×9关闭单时钟关闭开启异步输出时钟电路加固 2单端口512×9关闭单时钟关闭关闭异步输出时钟电路加固 3BIST------- 4FIFO512×9关闭单时钟关闭开启异步输出时钟电路加固 5简单双端口512×9关闭多时钟关闭关闭异步输出时钟电路加固 6单端口512×9关闭单时钟关闭关闭异步输出时钟电路加固,错误纠错码(每32位纠错1位),纠错刷新频率为20k,寄存器三模冗余。 7简单双端口512×9关闭多时钟关闭关闭异步输出时钟电路加固,错误纠错码(每32位纠错1位),纠错刷新频率为20M,寄存器三模冗余。

表4模型影响因子的取值

模型DPS 时钟电路1.000.001.00 写使能电路(静态)0.001.001.00 地址电路(静态)0.001.001.00 输出数据电路(静态)0.001.001.00 输入数据电路(静态)0.001.001.00 写使能电路(动态回读)0.101.001.00 地址电路(动态回读)0.101.001.00 输出数据电路(动态回读)0.101.001.00 输入数据电路(动态回读)0.001.001.00 复位电路1.001.001.00 三模冗余寄存器1.000.3396.00 寄存器1.001.0096.00 ECC+纠错刷新为20k下的存储阵列1.000.554096.00 ECC+纠错刷新为2M下的存储阵列1.000.014096.00 存储阵列1.001.004096.00

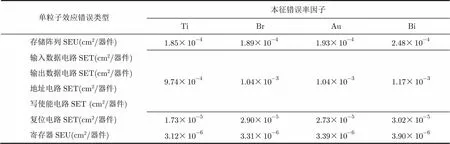

表5 重离子实验监测结果

(3)寄存器的本征错误率测试 将待测芯片配置为表3中第3种工作模式,即Build-In-Self-Test (BIST)扫描链模式,根据实验可得此电路内部寄存器的错误率并记录至表5。

3.3.2嵌入式存储器应用实例的测试 将待测芯片依次配置为表3中第4种,第5种,第6种和第7种工作模式后,向嵌入式存储器芯片中写入数据。在辐照实验中,将时钟频率设置为20 MHz,对于第4种模式动态读出嵌入式存储器中的数据,其余模式测试静态翻转截面,得出不同应用实例电路的SEE失效率,记录至表6和表7中实测失效率一栏。

3.3.3 模型影响因子的计算 针对3.3.2节中的嵌入式存储器应用实例,可得到模型中因子的取值如下表4所示。需要特别指出的是,根据2.2.3节中因子的计算公式可知,根据应用电路只采用了读操作而未采用写操作以及存储器时序参数中的建立时间、保持时间和工作频率,可得din的取值为0,输出数据电路、写使能电路和地址电路的取值为0.1;根据辐照时嵌入式存储器试验芯片的自修复能力、实验环境、表5中数据和2.2.4节中的计算公式可知,对于采用加固设计的时钟电路其clk的取值为0,对于采用容错方案的存储阵列,其m的取值与容错方案等因素有关。

4 单粒子实验结果与分析

4.1 模型影响因子分析

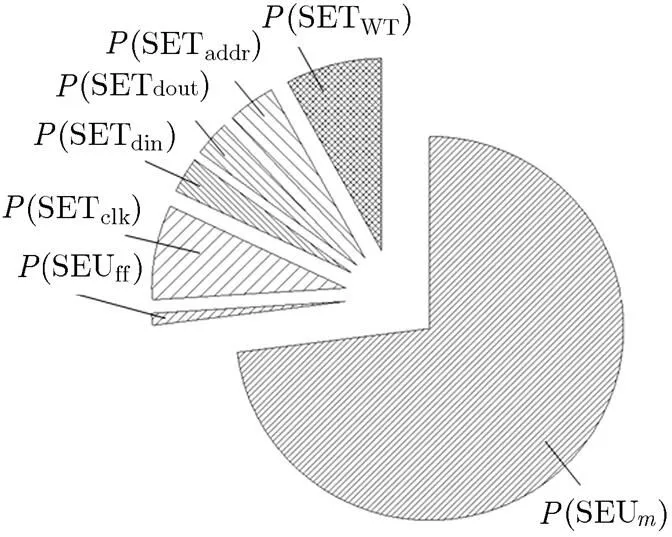

实验结果如表5所示。表中数据可证实模型中所包含的写使能电路的SET效应、输出数据电路的SET效应、复位电路的SET效应、输入地址电路的SET效应、寄存器的SEU效应和存储阵列的SEU效应的存在。将表5中的结果代入FIFO应用电路中,并假设其中包含的电路都不采用加固,得出其内部电路单元失效率百分比关系如图3所示,可以证明:SET对嵌入式存储器的影响不可忽略,且使用归一化存储阵列模型无法准确评估存储阵列、内部寄存器和内部逻辑单元等电路受到的不同SEE影响。

4.2 模型验证结果

根据上述步骤得出的因子,可对不同配置模式、不同容错方案的存储器应用实例SEE失效率进行预估。

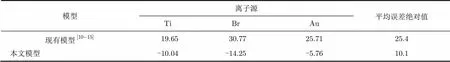

4.2.1不同辐照条件下模型有效性的验证 本文选取评估的应用电路为表3中第4种工作模式,在Ti, Br和Au粒子环境下进行实验,并采用读操作的存储器电路。将得出的因子代入通用存储器SEE失效率模型和本文的失效率模型中进行计算,可得到图4。

图3 FIFO应用电路中各个电路单元失效率占存储器失效率的百分比

图4 文中模型与现有模型[16]结果的比较

将上述两项预测结果与辐照实验中对存储器应用实例的实测失效率进行比较,可得到表6,可知本文模型的平均误差绝对值为10.1%,小于现有模型的平均误差绝对值25.4%。相较于现有的存储器SEE失效率模型。本文模型的误差主要来自于以下两个方面:一是由于实验环境中粒子总注量和注量率无法精确控制而导致实验中实测失效率的测量误差。二是由于实验环境中粒子总注量和注量率无法精确控制而导致影响模型预测失效率结果的本征错误率因子(包括存储阵列、写使能电路、输出数据电路、寄存器、地址电路和复位电路的本征错误率)的测量误差。

上述试验对模型有效性的验证过程中,对存储器的配置模式包括了不同端口数目,不同工作模式,不同时钟模式和不同辐照实验环境,覆盖了嵌入式存储器目前存在的所有工作模式,结果显示,其误差小于原有的失效率评估模型,由此可知,该模型评估不同辐照条件和不同工作模式下的存储器具有普遍适用性。

4.2.2不同容错方案下模型有效性的验证 将上述步骤得出的因子代入本文的SEE失效率评估模型中计算,可对辐照实验中不同配置模式、不同容错方案的存储器应用实例SEE失效率预估。实验使用离子源为Bi粒子,预估失效率如表7所示,其平均误差仅为10.5%,本文容错方案下模型预测误差除了受到4.2.1节中由于地面辐照实验中的离子总注量和注量率无法精确控制而导致模型中用于计算预测失效率的本征错误率因子和实测失效率的误差以外,还有在计算时采用的系统对错误的自修复能力等因子取近似值而导致的计算误差。

表6不同辐照条件下模型有效性验证结果(%)

模型离子源平均误差绝对值 TiBrAu 现有模型 19.65 30.7725.7125.4 本文模型-10.04-14.25-5.7610.1

本实验的存储器中包括了常用的存储器容错模式(包括了三模冗余容错,错误纠错码和纠错刷新),并在上述容错模式的自修复能力因子取值不同时,对于存储器的失效率进行了预估,实验结果显示,其误差小于原有失效率预测模型,由此可知,该模型在评估不同容错方案下存储器的失效率具有普遍适用性。

表7不同容错方案下模型有效性验证结果

模型实验中嵌入式存储器工作模式 表3中工作模式5表3中工作模式6表3中工作模式7 本文模型预测失效率(cm2/器件)2.491.380.04 实测失效率(cm2/器件)3.251.560.04 误差绝对值(%)14.0011.745.83 本文模型的平均绝对误差(%)10.5

5 结束语

准确评估嵌入式存储器SEE失效率,对现代宇航电路系统的可靠性设计具有重要意义。本文采用了自底向上的方法,提出了一种涵盖不同辐照敏感电路、不同SEE失效类型的嵌入式存储器失效率评估模型,并介绍了如何通过地面重离子实验取得模型中参数的具体方法。利用此模型和辐照实验中得到的参数,可以对嵌入式存储器在不同模式下的SEE失效率进行准确量化分析,而无需进行一一辐照实验验证,可以大大缩短可靠性验证所需的时间。此外,系统设计者可以结合功能和可靠性要求,在设计初期利用此模型对嵌入式存储器应用模式和容错方案进行选择,从性能、功耗和面积等方面进行全面优化。

致谢 本文实验得到了中国原子能科学研究院核物理研究所HI-13串列静电加速器和中国科学院近代物理研究所兰州重离子加速器国家实验室回旋加速器CSR运行人员的大力支持,在此表示衷心的感谢。

[1] 宋凝芳, 朱明达, 潘雄. SRAM型FPGA单粒子效应试验研究[J]. 宇航学报, 2012, 33(6): 836-842.

Song Ning-fang, Zhu Ming-da, and Pan Xiong. Experimental study of single events effects in SRAM-based FPGA[J]., 2012, 33(6): 836-842.

[2] Li Y. Reliability Techniques for Data Communication and Storage in FPGA-Based Circuits[M]. Brigham Young University, US, 2013: 15-20.

[3] John H, Roy C, and Hilton H. Phoenix Mars mission the thermal evolved gas analyzer[J]., 2008, 19(7): 1377-1383.

[4] Altera Corporation. Stratix V device handbook[R]. California, America, 2013.

[5] Xilinx Corporation, Virtex-7 FPGA user guide[R]. California, America, 2013.

[6] 蔡刚, 杨海钢. 嵌入式可编程存储器设计中的”选择性寄存”方法[J]. 电子与信息学报, 2009, 31(11): 2672-2766.

Cai Gang and Yang Hai-gang. A “selective registering” technique for design of an embedded programmable memory[J].&, 2009, 31(11): 2672-2766.

[7] Lesea Austin, Drimer Saar, and Fabula Joe. The rosetta experiment: atmospheric soft error rate testing in differing technology FPGAs[J]., 2005, 5(3): 317-328.

[8] SheXiao-xuan, Li N, and Waileen JD. SEU tolerant memory using error correction code[J]., 2012, 59(1): 205-210.

[9] Mukati Altaf. A survey of memory error correcting techniques for improved reliability[J]., 2011, 34: 517-522.

[10] Maestro Juan Antonio and Reviriego Pedro. Reliability of single-error correction protected memories[J]., 2009, 58(1): 193-201.

[11] SchianoLuca, OttaviMarco, and LombardiFabrizio. Markov models of fault-tolerant memory systems under SEU[C]. International Workshop on Memory Technology, Design and Testing, Paris, 2004: 1052-1087.

[12] ReviriegoPedro and MaestroJuan Antonio. Reliability analysis of memories suffering multiple bit upsets[J]., 2007, 7(4): 592-601.

[13] Sanchez-Macian Alfonso, Reviriego Pedro, and Antonio Juan. Enhanced detection of double and triple adjacent errors in hamming codes through selective bit placement[J]., 2012, 12(2): 357-362.

[14] Guo Jing, Xiao Li-yi, and Mao Zhi-gang. Enhanced memory reliability against multiple cell upsets using decimal matrix code[J].(), 2014, 22(1): 127-135.

[15] Lee Soonyoung, Jeon Sang Hoon, and Baeg Sanghyeon. Memory reliability analysis for multiple block effect of soft errors[J]., 2013, 60(2): 1384-1389.

[16] Sterpone L. On the design of tunable fault tolerant circuits on SRAM-based FPGAs for safety critical applications[C]. Proceedings of Design, Automation and Test in Europe, Paris, 2008: 59-65.

[17] Swift Gary M. 1st consortium report virtex 2 static SEU characterization[R]. California, America, 2004.

[18] Wang J J. RTAXS single event effects test report[R]. California, America, 2004.

[19] Morgan Keith S, McMurtrey Daniel L, Pratt Brian H,.. A comparison of TMR with alternative fault-tolerant design techniques for FPGAs[J]., 2007, 54(6): 2065-2072.

[20] 王忠明, 姚志斌, 潘雄. SRAM型FPGA的静态与动态单粒子效应试验[J]. 原子能科学技术, 2011, 45(12): 1506-1510.

Wang Zhong-ming, Yao Zhi-bin, and Pan Xiong. Static and dynamic tests of single-event effect in SRAM-Based FPGA[J]., 2011, 45(12): 1506-1510.

[21] Cabanas-Holmen Manuel, Cannon Ethan H, and Amort Tony. Predicting the single-event error rate of a radiation hardened by design microprocessor[J]., 2011, 58(6): 2726-2733.

支 天: 女,1987年生,博士生,研究方向为嵌入式存储器设计及可靠性理论研究.

杨海钢: 男,1960年生,研究员,中国科学院“百人计划”引进国外杰出人才,研究方向为数模混合信号SoC设计和大规模集成电路设计.

蔡 刚: 男,1980年生,助理研究员,研究方向为嵌入式IP设计及抗辐照理论研究.

Study on the Prediction of Single-event Effects InducedFailure Rate for Embedded Memories

Zhi Tian①②Yang Hai-gang①Cai Gang①Qiu Xiao-qiang①Li Tian-wen①②Wang Xin-gang①②

①(,,100190,)②(,100190,)

Embedded memories are easily influenced by Single-Event Effects (SEE). A model to calculate the SEE failure rate of an embedded memory is proposed, which considers the likelihood that an single-event upset or single-event transient will become an error in different types of circuits. It can also be used for the quantitative analysis of SEE mitigation techniques for versatile memories. Experimental investigations are performed using heavy ion accelerators on an experimental embedded programmable memory, which is designed by Institute of Electronics, Chinese Academy of Sciences. The result of 10.5% average error verifies the effectiveness of the proposed model.

System on Chip (SoC); Embedded memory; Single Event Effects (SEE); Failure rate; Prediction

TN432

A

1009-5896(2014)12-3035-07

10.3724/SP.J.1146.2013.02025

杨海钢 yanghg@mail.ie.ac.cn

2013-12-25收到,2014-05-19改回

中国科学院、国家外国专家局创新团队国际合作伙伴计划资助及国家科技重大专项(2013ZX03006004)资助课题