一种基于Nios II/DMA的 TFT-LCD控制器IP核设计

2014-03-21雷瑞庭

宋 跃,程 博,2,雷瑞庭

(1.东莞理工学院电子工程学院,广东东莞 523808;2.华南理工大学电子与信息学院,广东广州 510640)

0 引言

对于TFT-LCD控制器。目前国内外主要的解决方案有:(1)专用的LCD控制器芯片,其针对性较强,价格昂贵,不利于片上系统的开发;(2)软件控制方法,会占用大量的处理器资源,降低系统性能[1];(3)采用单片机的解决方案,在系统要求高速处理大量的实时数据并显示时显得非常困难[2-3]。文中运用DMA技术,较好地完成了基于Nios II 的全彩AT070TN84 TFT-LCD控制器IP核设计。既提升现有FPGA的利用率,又提升了系统的集成度。

1 控制器系统设计

FPGA主芯片采用Altera-Cyclone IV-EP4CE6F17C8N。图1中整个系统主要在一片FPGA中实现,以NiosII软核处理器为核心,各种IP核通过Avalon总线连接到NiosII[4-5]。其中,自主设计编写的LCD控制器IP核通过流模式从端口与DMA相连,其接口符合Avalon总线规范。

图1 系统设计

NiosII处理器在SDRAM中开辟帧缓冲区,可以是单缓冲也可以是双缓冲。如单缓冲:处理器将1帧数据(800×480×2 Bytes,RGB565,16 bit)存入帧缓冲,然后将帧缓冲的首地址与LCD控制器地址写入到DMA控制器,并启动DMA控制器。DMA控制器自动从传来的首地址处开始读取数据,并输出给LCD控制器。LCD控制器建立帧缓存与液晶屏幕像素之间一一对应的关系,并将帧缓存中的数据输送给LCD屏完成显示刷新。

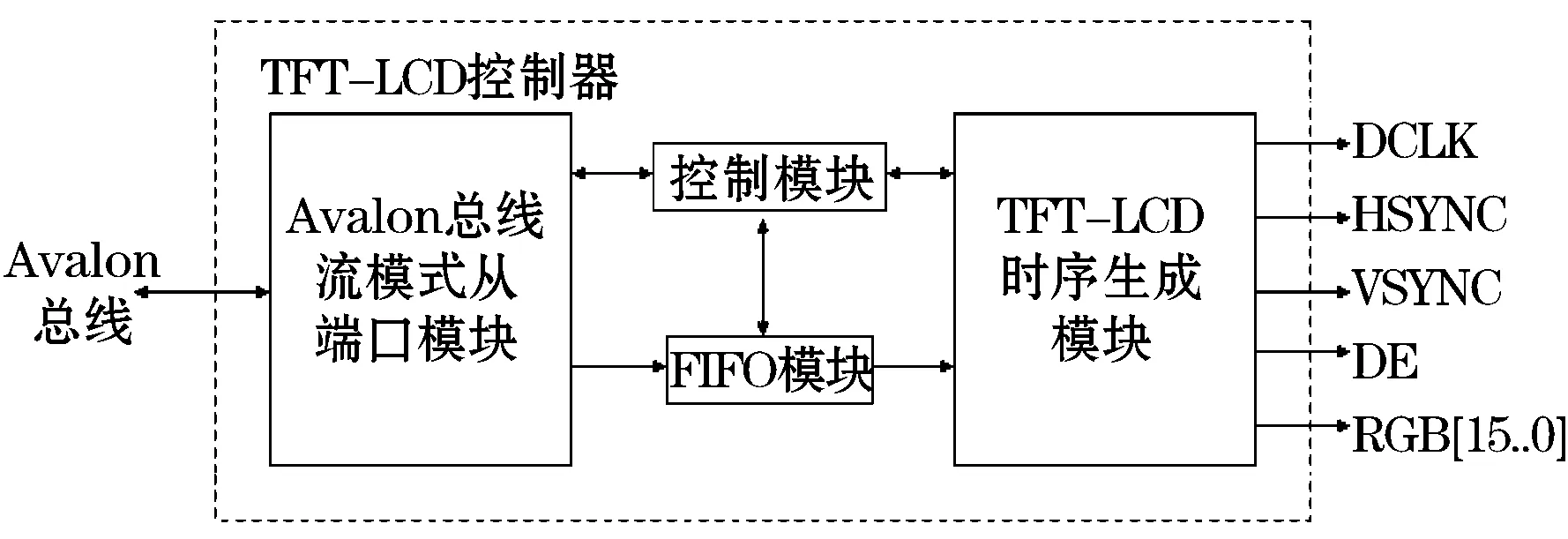

图2为TFT-LCD控制器结构设计。由于要与DMA模块进行对接,Avalon总线接口选择以Avalon流模式从端口的形式进行开发。控制器启动后,通过Avalon总线读取DMA传输的数据,然后存入FIFO中,时序生成模块依据LCD屏的时序规范生成行、场同步信号,从FIFO中读取数据,然后送出去显示。由于DMA读取速度与TFT-LCD时序发生器输出的速度不一致,所以需加FIFO用来缓冲数据。各个模块间通过控制模块进行有效控制。当FIFO快满时控制Avalon总线接口暂停DMA;当FIFO快空时控制Avalon总线接口重新启动DMA;当FIFO为空时暂停时序发生器,当FIFO不为空时启动时序发生器,以此协调画面连续稳定。

图2 TFT-LCO控制器结构

2 TFT-LCD IP核设计

2.1流模式从端口接口模块

Avalon总线流模式从端口接口负责DMA与LCD控制器的接口控制,DMA通过该总线接口将数据传入LCD控制器中的FIFO缓存,并接受控制信号的控制[6]。该模块接口如下:

//----Avalon------

input clk_100M;

input rst_n;

input chipselect;

input write;

input [15:0] writedata;

output readyfordata;

output endofpacket;

LCD控制器通过设置readfordata有效来表示它能够接收写传输。Avalon总线模块在readyfordata无效时不能发起传输。当readfordata有效时,Avalon总线模块能够通过在一个clk 上升沿设置chipselect有效来开始一次写传输,从Avalon总线到从端口的锁存输出write和writedata有效。在一次传输结束后,如果外设不能接收随后的写传输数据,则必须置readyfordata无效,使得Avalon总线模块不会在下一个clk上升沿发起另一次写传输。当LCD控制器使readyfordata失效时,会迫使Avalon总线模块将送到这一从端口的chipselect、write置为无效[7-8]。因此,在LCD控制器将readyfordata再次置为有效之前,Avalon总线模块不会对该从端口发起另一次写传输。如果流模式主端口在从端口的readyfordata无效时发起了一次写传输,Avalon总线模块会简单地迫使主端口等待,直到能再次从从端口捕获数据。

2.2FIFO模块

图3为FIFO模块,实现DMA输出的图像数据缓存,以匹配时序控制模块的输出速度[4,9]。FIFO大小暂定为2 048×16 bit,在实际应用时可根据需要以及资源状况再做调整。

图3 FIFO模块

FIFO由DMA控制器写入数据,写入时钟为100 MHz,由LCD控制器的时序发生模块读出数据,读出时钟为DCLK,即LCD的像素点扫描频率,通常取25 MHz.在独立的写时钟和读时钟作用下,FIFO可以提供wrusedw[10:0]信号,用于指示在wrclk时钟下FIFO中的数据个数[6]。系统可以设置一个上限和一个下限,当FIFO中的数据量高于上限或低于下限时,控制器暂停DMA传输或启动DMA传输,用以保证系统性能。

2.3时序模块

TFT液晶显示屏采用逐行扫描的扫描方式[4],液晶的控制和驱动主要是依据液晶显示所需控制信号的标准来实现的,控制信号主要是行、场同步时序信号,在控制信号的作用下将显示数据输出至显示端口[3]。AT070TN84时序如图4、图5。

图4 行信号时序

图5 场信号时序

设计TFT-LCD的工作时钟为25 MHz,设f为刷新率,则有:

F=tHP·tVP·f=25 MHz

tHP=tHW+tHBP+tHV+tHFP

tVP=tVW+tVBP+tW+tVFP

可求得f=61.54 Hz,即设计得到TFT-LCD工作在25 MHz时有61.54 Hz的刷新率,满足人眼分辨的要求[7]。

设计中以参数化形式对时序参数进行编程如下:

parameter HP = 824;

parameter VP = 493;

parameter HW = 3;

parameter HBP = 13;

parameter HV = 800;

parameter HFP = 8;

parameter VW = 1;

parameter VBP = 7;

parameter VV = 480;

parameter VFP = 5;

这样在使用其他TFT-LCD屏时只需修改相应参数就可以完成对控制器IP核的复用。

3 仿真与软件编程测试

TFT-LCD控制器时序仿真结果如图6、图7,仿真结果表明显示控制器工作正常。

图6 功能仿真

图7 时序仿真

软件编写中主要是对DMA的设置,以下是部分程序代码:

//设置DMA所要传输的字节数,则一帧图像TLENGTH =800*480*2

IOWR_ALTERA_AVALON_DMA_LENGTH (DMA_0_BASE,TLENGTH);

//设置DMA传输中要读取的第一个数据单元的地址,即SDRAM中帧缓冲的首地址

IOWR_ALTERA_AVALON_DMA_RADDRESS (DMA_0_BASE,(int)P_VIDEO_MEMORY);

//设置DMA写地址,即流模式从外设TFT-LCD控制器地址

IOWR_ALTERA_AVALON_DMA_WADDRESS (DMA_0_BASE,(int)P_LCD_CONTROL);

//设置DMA控制寄存器

IOWR_ALTERA_AVALON_DMA_CONTROL (DMA_0_BASE,

ALTERA_AVALON_DMA_CONTROL_HW_MSK | //半字(16bit)传输

ALTERA_AVALON_DMA_CONTROL_GO_MSK | //启动DMA

ALTERA_AVALON_DMA_CONTROL_I_EN_MSK | //开启中断

ALTERA_AVALON_DMA_CONTROL_WCON_MSK | //向固定地址写入数据

ALTERA_AVALON_DMA_CONTROL_WEEN_MSK | //允许写端口包结束事件

ALTERA_AVALON_DMA_CONTROL_LEEN_MSK //传输完固定长度数据结束

);

试验照相表明图像显示清晰,色彩丰富,没有闪屏、错行等现象,视觉效果良好。在试验过程中液晶屏出现错行现象,分析发现为控制器对FIFO为空时的处理不当,以及FIFO模块与时序生成模块间有一个节拍的延迟所导致,修复后液晶屏显示正常。

4 结束语

该设计通过DMA完成对帧缓存的读取,大大提高了处理器效率,参数化的组件设计思想,也提高了IP核的可复用性,具有较强的实用性和通用性,便于二次开发,为满足项目更高需求,计划再设计ADS7843 SPI串行接口芯片,使系统能结合触摸信息,来丰富液晶屏显示的系统控制功能,这些还在研制之中。

参考文献:

[1]黄俊凯,蒋存波,叶汉民,等.嵌入式LCD控制器的设计和实现.计算机工程,2005,31(3):218-220.

[3]于 海,樊晓桠.基于FPGA 异步FIFO的研究与实现.微电子学与计算机,2007,24(3):210-216.

[4]朱耀东,经亚枝,张焕春.基于FPGA的LCD&VGA控制器设计.电子技术应用,2002,28(11):44-46.

[5]群创光电股份有限公司.INNOLUX DISPLAY CORPORATION LCD MODULE SPECIFICATION[Z].2008:1-120.

[6]付先成,邹雪城,雷镒铭.FIFO电路在液晶显示控制器中的应用.华中科技大学学报,2006,34(4):8-10.

[7]高恭娴,胡国兵.基于SOPC的彩色液晶显示控制器的设计.液晶与显示,2010(1):79-84.

[8]王言荣.基于FPGA液晶控制器设计与实现:[学位论文].杭州:浙江大学,2006:1-74.

[9]胡健生,罗卫兵,钱渊.嵌入式TFT-LCD控制器设计.2010,36(5):237-239.