基于FPGA的PLC输入存储与读取控制器的设计

2014-03-21蔡启仲张玲玲

李 静,蔡启仲,张 炜,张玲玲

(1.桂林电子科技大学电子工程与自动化学院,广西桂林 541004;2.广西科技大学电气与信息工程学院,广西柳州 545006)

0 引言

可编程控制器(PLC:Programmable Controller)是现代工业控制极其重要的核心器件。PLC在输入采集阶段读入所有开关量的状态,并存入输入映像存储器,在PLC用户程序执行过程中,需要频繁地对输入映像存储器进行读操作,读取PLC指令执行所需开关量软元件的位信息或4位1组以及多组4位1组信息构成的开关量数据[1-2]。为了简便高速地读取相应的位信息和数据,利用FPGA高效的运算能力和并行处理的特点,设计PLC输入存储与读取控制器,在内部时序脉冲控制下,通过地址运算或移位方法迅速读取开关量的位信息和数据,解决控制器的时序脉冲与命令执行过程中的相关问题,从而有效地提高可编程控制器执行指令的速度。

1 系统总体设计

1.1系统基本功能

(1)输入信号采集:PLC输入采集阶段,直接读取PLC输入端口开关量信息传输给映像存储器,采取一次读入64位数据的方式。

(2)高速输入位信息的读取:在PLC执行高速指令时直接从PLC的输入端口X00~X07读取1位信息。

(3)PLC程序执行过程中位信息的读取:在PLC执行程序时直接从映像存储器读取位信息,这是PLC执行程序时使用频率最高的功能。

(4)PLC程序执行过程中数据信号的读取:这是针对PLC程序执行过程中类似于X4K3这样由位组成的数据,针对这种情况PLC 需要读取4位信息为1组或多组以4位信息为1组的信息(即4,8,12,16,20,24,28,32位的形式)。

根据系统的4个基本功能确定系统的4个功能命令:输入信号采集命令、高速输入位信息读取命令、位信息读取命令和数据信号读取命令。

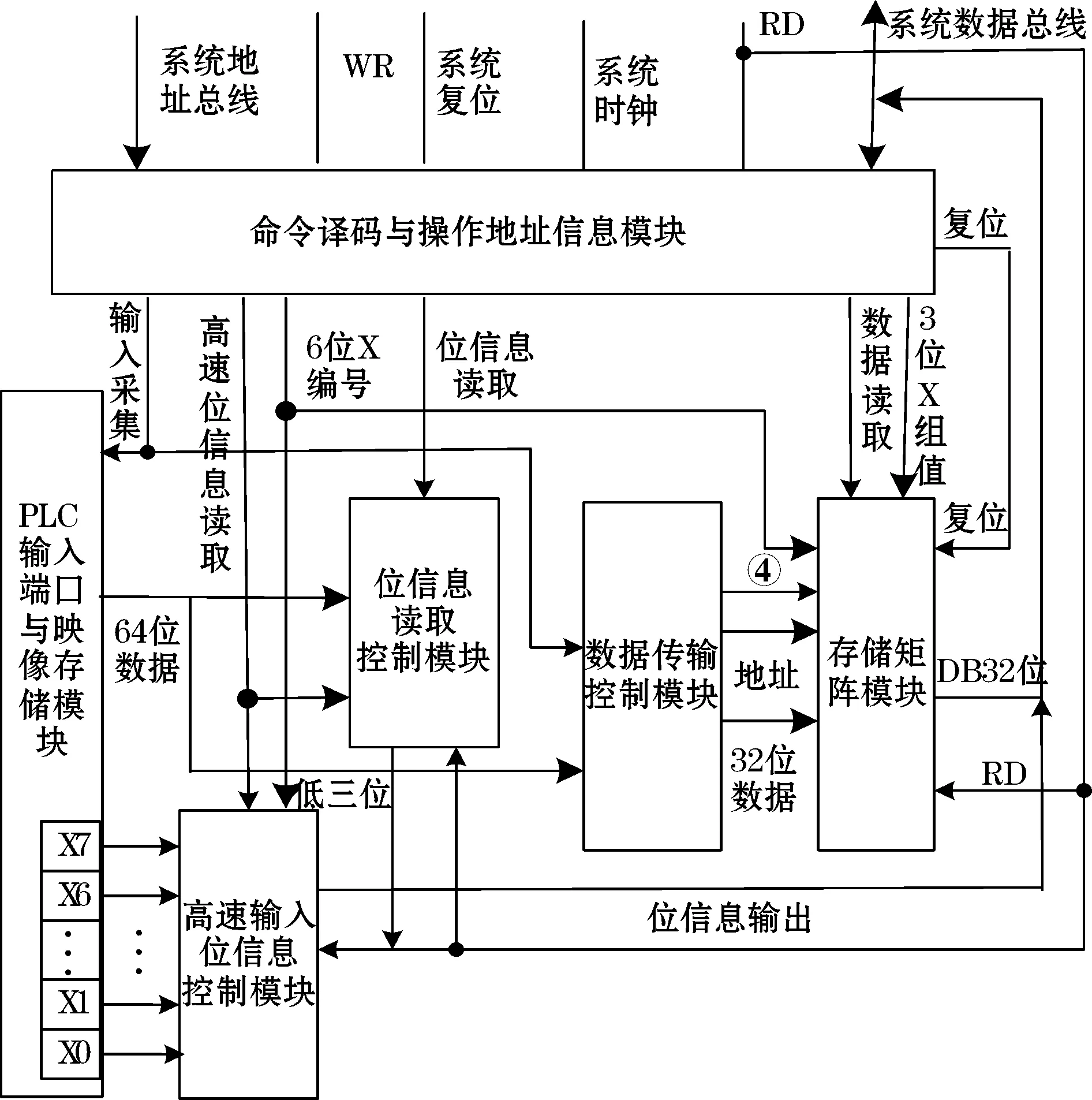

1.2系统整体方案

系统整体设计框图如图1所示,分为6个部分:PLC输入端口与映像存储模块、命令译码与操作地址信息模块、高速输入位信息控制模块、位信息读取控制模块、数据传输控制模块和存储矩阵模块。

其工作流程为:系统一个写脉冲WR写入命令,经过译码得到执行的功能命令;执行输入信号采集命令时,将PLC输入端口的信息以64位的形式一次读入映像存储器,并在内部时序脉冲作用下自主完成4位1组输入数据的所有数据的组合,并按照顺序存入存储矩阵中。执行读取命令时,一个读脉冲RD即可读出位信息、高速输入位信息或数据至系统数据总线[3-4]。

图1 PLC输入存储与读取控制器结构图

PLC共有64个输入端口X00~X63;系统复位信号为低电平有效;系统地址总线定义为5位,地址值为本模块地址时,使能片选信号;总线通过32位数据总线D31~D0写入命令和操作位;用WR和RD控制数据的写和读,当写信号WR作用时将来自系统数据总线的命令字写入命令译码与操作地址信息模块;当读信号RD作用时,读出位信息或数据至系统数据总线[5-6]。

2 功能模块设计

2.1PLC输入端口与映像存储模块

PLC输入端口与映像存储模块由PLC输入端口、PLC输入调理电路、FPGA输入端口、64位入64位出输入映像存储器组成。

PLC输入端口与外部输入开关和PLC输入调理电路连接,PLC输入端口从外部输入开关获得64位开关量信息,并将开关量信息传输给PLC输入调理电路,PLC输入调理电路将0~24 V开关量调理成为FPGA端口输入对应的0~3 V信号,并对开关信号滤波,消除开关输入信号的抖动。在输入采集信号的作用下,将64位开关量信号存入64位入64位出输入映像存储器中。

2.2命令译码与操作地址信息模块

命令译码与操作地址信息模块是PLC输入存储与读取控制器的控制核心,用来完成输入命令的译码和操作地址的存储。该模块主要包括模块地址识别、命令寄存器和操作特征译码器。

系统选定PLC输入存储与读取控制器工作时,系统地址总线的地址值和模块地址相同,模块地址识别输出片选信号为“0”,使能命令寄存器,在系统写脉冲WR作用下,将系统32位数据(D31~D0)存储在命令寄存器中,操作特征译码器根据存储在命令寄存器中的3位命令字,决定执行的命令。

系统数据总线输入的命令字主要分为3部分:操作特征编码线、X元件编号、3位X组值。

(1)操作特征编码线(D11~D9):操作特征编码线经过译码输出5个译码值作为输入模块4个功能的命令线和复位输出。操作特征编码如表1所示。

表1 操作特征编码

(2)X元件编号(D8~D3):作为读取命令时软元件寻址的地址编码。位信息读取时,编码位分为2部分:高4位(D8~D5)作为X软元件的组编码地址,每4个X软元件编为1组,低2位(D4~D3)作为X软元件的组内编码地址;高速输入位信息读取时只取X元件编号的低3位(D5~D3)作为元件的寻址地址;数据信号读取命令作用时,用X元件编号的高4位(D8~D5)来寻找组内首元件的地址。

(3)3位X组值(D2~D0):数据信号读取命令作用时,X组值用来寻找组号K1~K8。

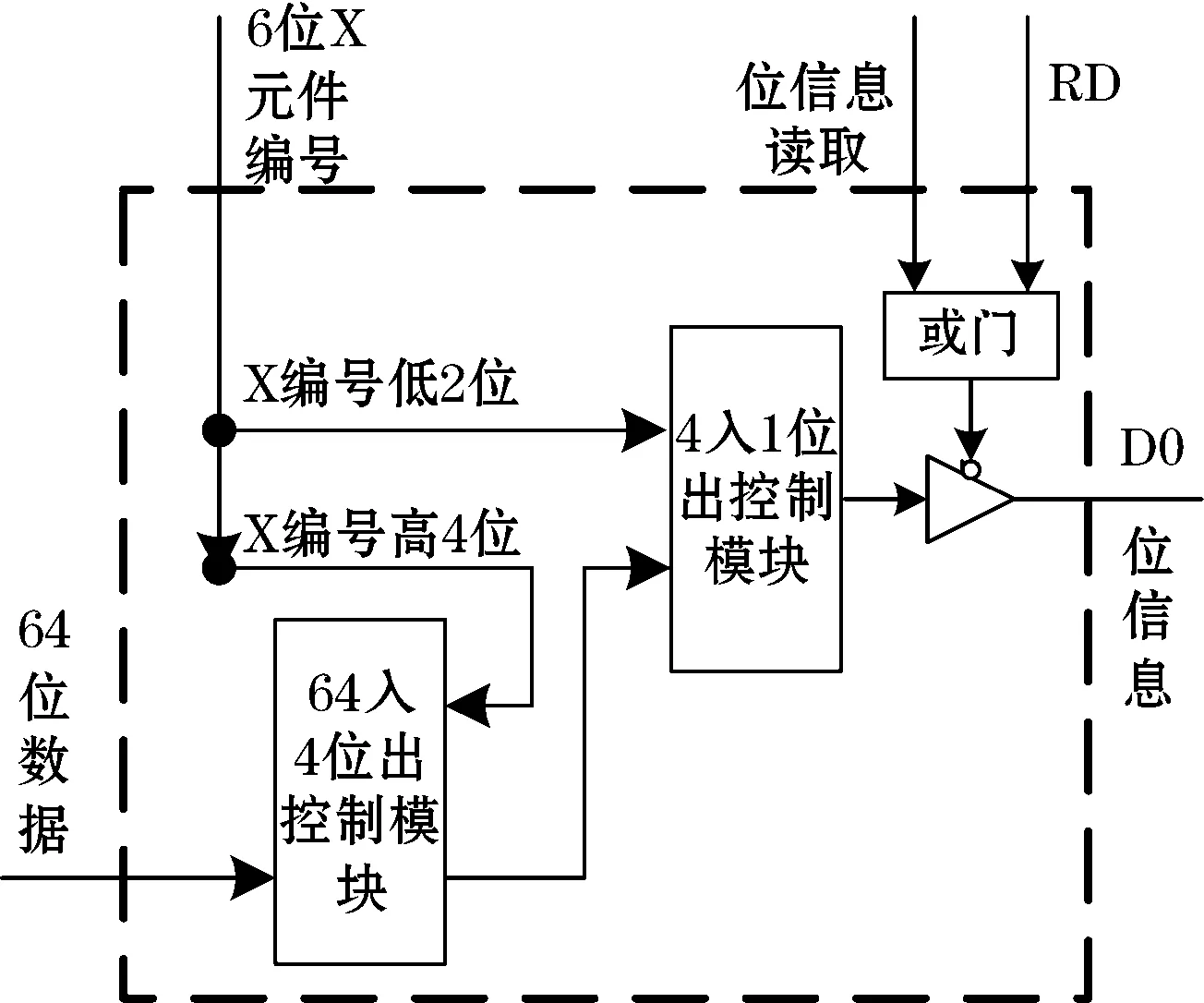

2.3位信息读取控制模块

位信息读取控制模块主要由64位入4位出存储模块、4位入1位出控制模块和三态门组成。图2为位信息读取控制模块结构图。

图2 位信息读取控制模块结构图

写脉冲WR作用时,6位X元件编号通过命令寄存器直接写进来,按照X元件编号高4位编码地址,选定64位入4位出存储模块中1组4位信息输出至4位入1位出控制模块;根据X元件编号的低2位指定的组内编码地址选定4位入1位出控制模块的1位信息输出至三态门的输入端口;在位信息读取命令和读信号RD的作用时,三态门输出位信息至系统数据总线的D0位。

位信息的寻址设计:用X元件编号实现寻址,首先将X63~X00软元件4位1组进行分组,64位共计16组,每个组内的4个元件编号的高4位二进制数相同,为0000H~1111H。用X元件编号的高4位来表示这16组的首元件地址,然后将每个组内的4个元件用X元件编号的低2位来寻址,从首元件开始依次为00~11。例如X53,X元件编号为110101,高4位地址为1101(52),先选定X55~X52这一组,然后根据低二位地址01,选定X53的位信息。

2.4高速输入位信息控制模块

该模块主要由3-8译码器和8个三态门组成。

3-8译码器的输入端是X元件编号低3位,输出端分别作为8个三态门的控制信号,低电平有效;8个三态门的输入端对应X0~X7的8个软元件位信息。当高速输入位信息读取命令作用时,3-8译码器使能,按照X元件编号低3位译码输出,3-8译码器有1个输出端为“0”,选定一个三态门导通,在读信号RD作用下,读出选定的软元件位信息至数据总线的D0位。

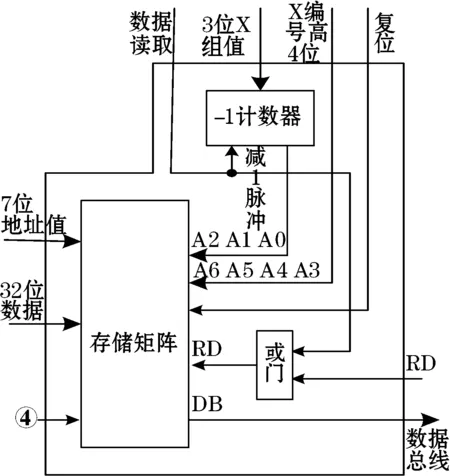

2.5存储矩阵模块

存储矩阵模块主要实现PLC应用指令中由位组成的数据的存储。基本思路是:设计一个双端口存储矩阵,存储4位1组或多组4位1组的数据,将所有这种数据组合存储在矩阵中的相应位置;PLC执行程序过程中,数据信号读取命令作用时,根据地址运算的结果选定双端口存储矩阵的单元内容,读出4位1组的信息。该模块主要包括存储矩阵、-1计数器。图3为存储矩阵控制模块结构图。

图3 存储矩阵控制模块结构图

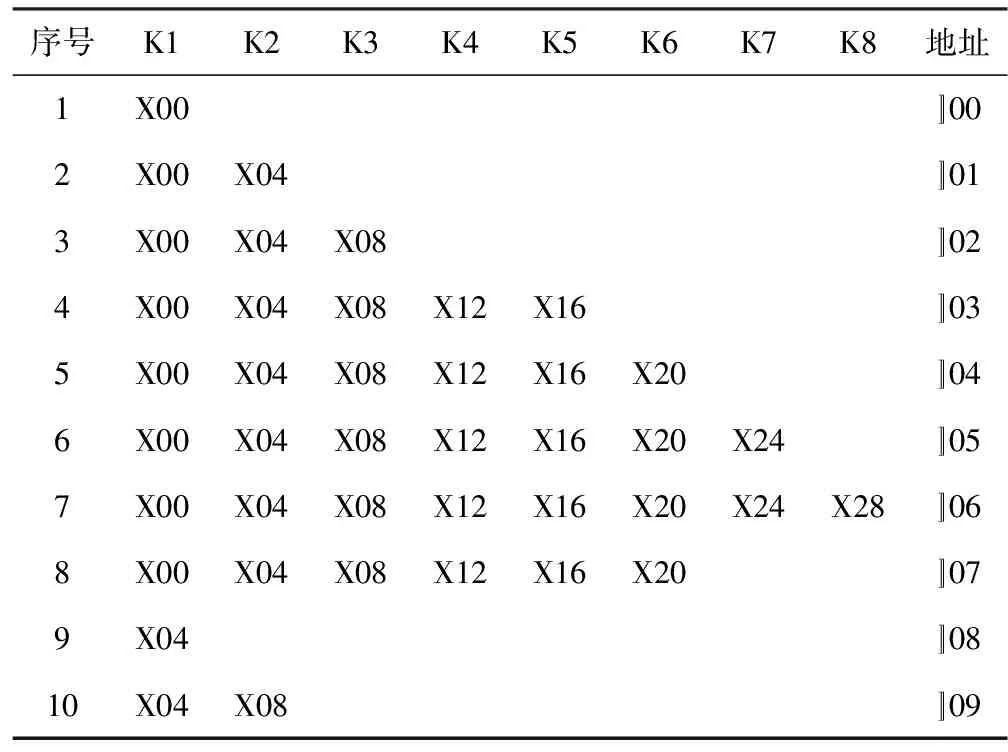

该存储矩阵共有100个存储单元,表2是存储矩阵00~09H地址单元存储内容示意图,对于每个首个X的K值按照K1、K2~K8排列,写入操作按照表中的顺序输入,例如,第1行~第8行,首先写入地址为00的存储单元的内容为X00~X04的位信息。然后将X00~X04、X05~X08的信息写入地址为01的存储单元,依次类推按照顺序存储。观察K1X00和K1X04,序号1的X00的地址为00,序号9的X04的地址为08,恰好是4位1组的4位数据的首元件编号的2倍。确定存储矩阵的读出地址有7位,由2个参数组成,一是X元件编号高4位,其值从0000~1000,将其与存储矩阵的高4位地址线连接。二是3位X组值,确定K1~K8这样的组号,将K值[组号]-1的值与存储矩阵的低三位地址线连接。

最终得出存储矩阵地址运算公式:

任何一个单元地址的计算=X元件首地址×2+(K值[组号]-1)

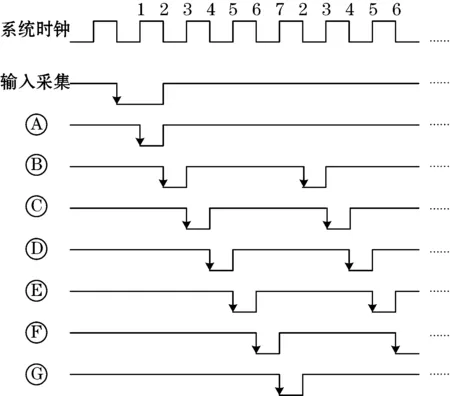

2.6数据传输控制模块

数据传输控制模块为存储矩阵模块提供地址运算和时序控制。该模块由地址与时序控制模块、64入4位出存储模块、4入32位出存储模块和脉冲分配器组成。其中,脉冲分配器是PLC输入存储与读取控制器实现自主控制的重要手段。图4为脉冲分配器脉冲输出波形。

表2 存储矩阵示意表格

图4 脉冲分配器脉冲输出波形

输入信号采集命令作用时,启动脉冲分配器作为该模块的内部时序控制信号。脉冲A作用时,将映像存储器中的X63~X00的软元件信息存储在64位入4位出存储模块;脉冲B作用时,按照地址与时序控制模块的地址运算结果指定的4位数据输出到内数据总线;脉冲C作用时,4位入32位输出存储模块按照地址与时序控制模块的运算结果,将数据线上的4位数据信息存进相应的存储单元。脉冲D作用时,按照地址与时序控制模块运算的地址值输出32位信息至存储矩阵模块。

3 仿真与验证

完成相应设计后,采用在底层设计方面更具优势的Verilog HDL语言来完成有关硬件的描述,编写testbench.v文件用于模拟外部系统输入信号,然后使用ModelSim软件进行功能仿真,观察该控制器内部数据的变化以及外部端口的输出状态[7-8]。

测试方法为:

(1)根据各个模块的功能要求编程完成仿真,然后编写顶层文件,将这些模块例化在顶层文件中,使其关联起来;

(2)对PLC输入存储与读取控制器的输入采集命令以及3种读取方式进行测试。写入功能命令,测试该控制器能否完成位信息或数据的正确读取[9-10]。

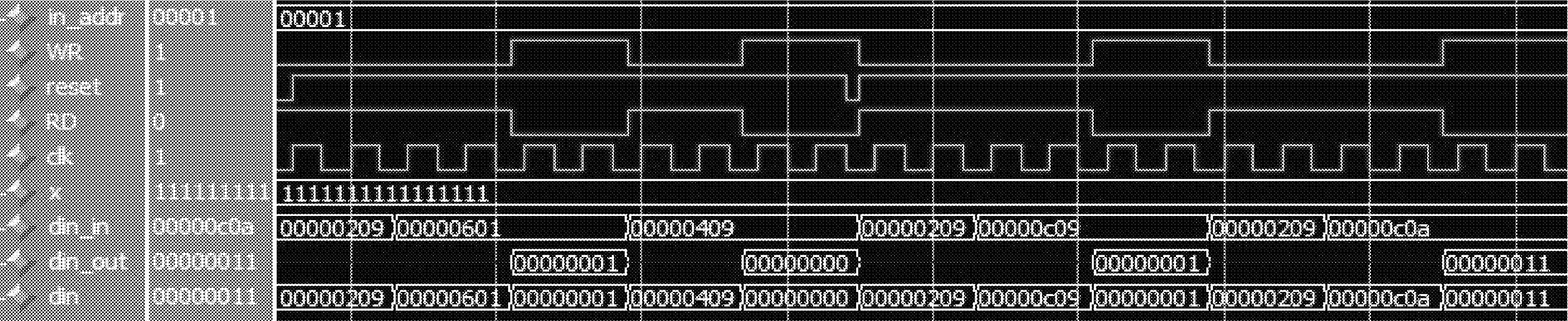

PLC输入存储与读取控制器位信息读取仿真图如图5所示。写入PLC输入采集命令Ox00000209,将64位开关量信息Ox1111111111111111存入映像存储器,同时启动脉冲分配器工作,在内部时序脉冲的作用下独立完成数据的读入操作;写入数据信号读取命令Ox00000C09 ,当读信号RD使能时,读出存储矩阵中地址为00H的4位信息为1组的数据Ox00000001,写入Ox00000C0A命令时,读出存储矩阵中地址01H的2组4位信息为1组的数据Ox00000011;写入高速位信息读取命令Ox00000601和位信息读取命令Ox00000409时,在读信号RD作用下,分别读出位信息X0和X1至系统数据总线D0位,如图5中所示D0分别为1和0。符合设计要求。

图5 PLC输入存储与读取控制器位信息读取仿真图

经测试,无论是读取输入位信息、高速输入位信息还是数据信号,只需要在系统的写信号WR作用下将命令写入命令寄存器,在系统读信号RD的作用下将选中的位单元信息发送到系统数据总线,使输入信息的读取更简便。表明此FPGA系统可以初步实现PLC输入存储与读取控制器的预期功能。

4 结论

PLC输入存储与读取控制器在内部时序脉冲作用下,具有自主组织4位1组输入数据的功能,使得输入采集与其他控制器模块实现并行处理;PLC用户程序执行过程中,位信息、高速输入位信息和数据信号读取都只需要2个PLC系统时钟,提高了PLC执行指令序列的速度,增强了控制性能。

参考文献:

[1]李青云.PLC可编程控制器的应用及发展趋势探析.中国科技信息,2010(16):117.

[2]方承远,张振国.工厂电气控制技术.3版.北京:机械工业出版社,2006.

[3]侯鸿佳,蔡启仲,陈文辉,等.ARM+FPGA组成的PLC结构的通信系统.广西工学院学报,2012(1):60-64.

[4]黎娜,蔡启仲,黄捷峰.基于ARM7与FPGA组成的可编程控制器,微计算机信息,2008(4):54-58.

[5]夏宇闻.Verilog数字系统设计教程.2版.北京:北京航空航天大学出版社,2008.

[6]华清远见嵌入式培训中心.FPGA应用开发入门与典型实例.北京:人民邮电出版社,2008:6.

[7]王强,文丰,任勇峰.基于FPGA的高速实时数据采集存储系统.仪表技术与传感器,2009(1):50-52.

[8]王荣扬,殷勇辉.伪随机序列超声测距系统与FPGA.仪表技术与传感器,2013(2):46-48.

[9]李霞,蔡启仲,陈文辉.基于CAN的嵌入式PLC和监控系统通信设计.仪表技术与传感器,2011(10):41-43.