通用运放测试仪

2014-03-16厦门大学嘉庚学院许燕儒黄云森林淑端林灿灿林天增刘伟俊

厦门大学嘉庚学院 许燕儒 黄云森 林淑端 林灿灿 林天增 刘伟俊

通用运算放大器(简称运放)芯片种类繁多,在电子设计很常用,性能有很大差异。在运放的技术指标中,带宽增益积(1)是重要技术指标之一,本文设计的通用运放测试仪能够测试运放的带宽增益积。

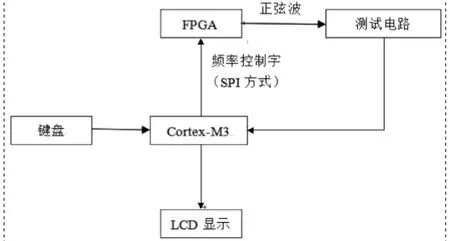

通用运放测试仪由Cortex-M3单片机(2)、FPGA、测试模块、键盘、LCD显示组成。其主控芯片Cortex-M3(3)单片机是一款低功耗处理器,是专为深度嵌入式应用而设计的,集合了高性能、低功耗、低成本等优点。LPC1768内部具有8路12位精度的AD转换通道,12位转换时间达到200KHz,转换电压0~3.3V;2个SPI接口(4)及控制器,具有同步、串行、全双工通信和可编程的数据长度。

通用运放测试仪工作时通过键盘控制扫频的范围,Cortex-M3单片机将各个频率控制字通过SPI接口传送给FPGA,FPGA接收到频率控制字后,通过DDS模块及D/A模块输出正弦波,正弦波是测试电路的输入信号。测试电路由被测运放组成运算放大器,测试电路的输出信号送至Cortex-M3单片机。Cortex-M3将接收到的信号首先计算出其有效值,再将有效值与输入信号比较,扫频计算得到带宽增益积。系统框图如图1所示。

图1 系统框图

下面说明测试电路模块(5)、FPGA扫频信号源模块、Cortex-M3单片机模块、软件的设计方法。

一、测试电路

运放工作时的输入电阻和反馈电阻大小不一,测试电路模块为运放工作选择不同的外围电阻,能够测试多种运放。模块由NE555(6)、CD40161(7)、74HC138、指示电路、CD4051、运放等组成。

NE555产生可编程4位二进制同步计数器CD40161所需的时钟信号,74HC138译码后通过CD4051选择不同电阻,框图如图2所示。

图2 测试电路模块框图

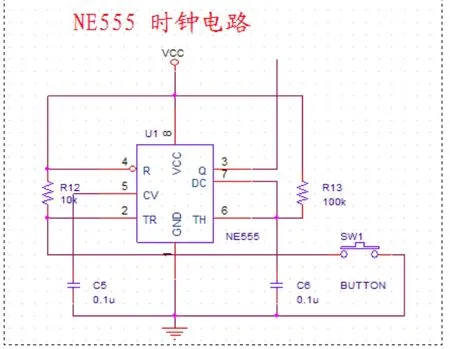

由NE555定时器构成的多谐振荡器电路原理图如图3所示。

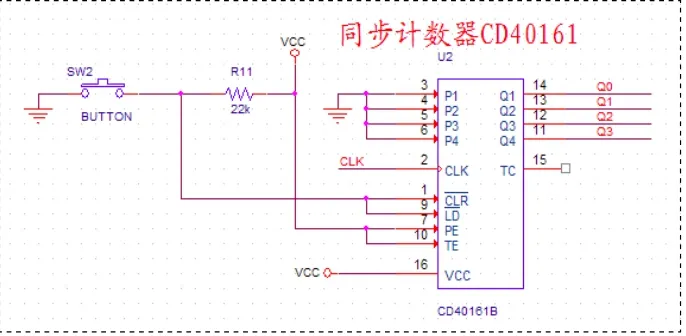

可编程4位二进制同步计数器CD40161电路原理图如图4所示。

运算放大器的外接电阻由电子开关CD4051根据74HC138的译码地址选择,可以选择8种不同的运放外接电阻。其电路原理图如图5所示。

图3 时钟产生电路原理图

图4 计数器电路原理图

图5 运放外围电阻选择电路原理图

图6 基于FPGA的扫频信号源

二、FPGA模块设计

FPGA模块设计采用的主控芯片是Altera公司生产的CycloneⅡ系列的FPGA芯片EP2C8Q208C8N,该系列的芯片是目前市场上性价比较高的芯片,与第一代芯片相比,有较大的改进,价格也可以被广大客户所接受。EP2C8Q208C8N的核心供电电压为1.2V,共有多达138个I/O口,内部有2个锁相环,16万RAM bit,最高工作频率可达320MHz。

扫频信号源是由FPGA与外围电路组成,其外围电路有D/A转换电路、调理电路、滤波输出。信号源的工作原理是:FPGA通过SPI接口接收来自于Cortex-M3单片机的指令和频率控制字,FPGA对频率控制字进行判断,从ROM中提取与频率控制字对应的正弦波数据并将数据输出至D/A转换电路,产生该频率的正弦阶梯波,经过调理电路提高波形的电压和功率,滤波器滤除D/A转换时带来的高次谐波,最后输出为连续的正弦波。其原理框图如图6所示。

D/A转换电路的芯片是AD9708,是一款高速DAC芯片,兼容8位、10位和12位并行数据输入,转换速度高达125MSPS,精度可达1/4LSB,工作电压为3V和5V,内部有1.2V的参考电压,也可外接参考电压,该芯片与一般的DAC芯片没有太大区别,工作模式配置好即可工作,本测试仪使用的是8位精度的DAC。电路原理图如图7所示。

图7 D/A转换电路

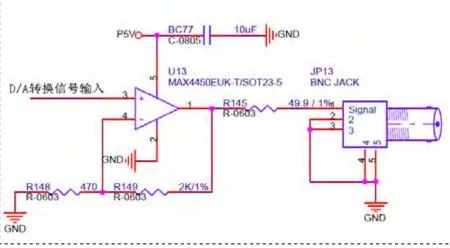

图8 调理电路

图9 滤波输出电路

图10 LPC1768系统框图

图11 Cortex-M3单片机流程图

调理电路放大D/A转换后的输出电压。其MAX4450是一款高速高性能的芯片,它的通频带为210MHz,转换速率可达485V/us,很好地满足了设计的要求,其原理如图8所示,同相放大电路的放大倍数为5.25倍,满足设计的需要。

滤波输出电路的设计是为了滤除D/A转换时带来的高次谐波,高次谐波会影响到D/A输出的结果。本次设计的滤波器是二阶巴特沃斯低通滤波器,其阻带衰减速率为-40dB/10倍频,采用了无限增益多路反馈电路。电路图如图9所示。

三、基于LPC1768的Cortex-M3单片机模块设计

LPC1768的Cortex-M3单片机负责信号源的控制、SPI接口的数据传输管理、A/D转换、对采集的数据进行处理和LCD显示等。LPC1768的外围电路主要有:按键电路、SPI接口电路、A/D转换电路、LCD接口电路等。其原理图如图10所示。

工作时LPC1768首先根据按键选择的频率范围进行数据处理,将频率控制字传送给FPGA;被测电路的输出信号再由LPC1768控制A/D转换,经过对数据的集中处理,判断出3dB带宽,在LCD上显示出带宽增益积。

四、带宽增益积的计算

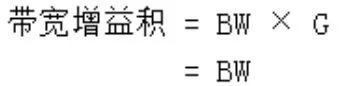

带宽增益积(GBW)顾名思义,就是频带宽度(BW)与增益(G)的乘积,由于本系统设计时就将增益(G)的值设置为1,所以,根据带宽增益积(GBW)的定义可以得到:

测量到频带宽度就可得到带宽增益积的值。测量时先设定FPGA输出的正弦波(即被测电路的输入信号)幅值为100mV,被测系统的增益(G)固定为1,将LPC1768多次测量的结果依次分别与100mV相比较,若所测量点的幅值衰减为初始幅值的0.707倍,即70.7mV时,该测量点即为频率截止点,而该点所对应的频率即为频带宽度,由此带宽增益积可知。

五、软件设计

设计的FPGA相当于一个信号源,程序比较简单。这里给出Cortex-M3单片机程序流程图如图11所示。

六、结束语

本系统采用性能优良的主流芯片,以单片机为核心控制各个模块工作,设计方案合理。在软硬件设计完成后进行逐级调试,逐级调试成功后再优化处理,使之工作在最佳状态。不足之处是受制于系统的工作速度,测试高速运放会力不从心,测试中低速运放则性能良好。

[1]Martin Hartley Jones A practical introduction to electronic circuits,Cambridge University Press,1995.page 148J.

[2]ARM Limited.Cortex-M3 Technical Reference Manual.2006.

[3]NXP Limited.UM10360 LPC17xx User manual(Rev.2).2010.

[4]Lei Jinhong.Design and implementation of a fault diagnosis system.[M].Control Conference(CCC),2012 31st Chinese,2012.

[5]Robert L.Boylestad,Louis Nashelsky.Electronic Devices and Circuit Theory Ninth Edition.Electronic Industry Press.2007.

[6]Dioszegi,Gyula,Nagy,Janos.NE555 timer sparks low-cost voltage-to-frequency converter,EDN,vol 53(4),2008,pp.75.

[7]Thomas L.Floyd.Digital Fundamentals,Tenth edition.Electronic Industry Press.2011.