基于SoC的DW450断路器用欠压脱扣器研究与设计

2014-03-07吴志祥蒋文贤

吴志祥,高 波,蒋文贤,黄 波

(1.常州工学院,江苏 常州 213002;2.江苏国星电器有限公司,江苏 常州 213177)

基于SoC的DW450断路器用欠压脱扣器研究与设计

吴志祥1,高 波1,蒋文贤2,黄 波2

(1.常州工学院,江苏 常州 213002;2.江苏国星电器有限公司,江苏 常州 213177)

针对新一代智能型低压万能式DW450断路器体积明显缩小,且对内嵌电子单元要求更高等特点,设计一种基于SoC(system-on-chip)的高性能欠压脱扣器。在现有DW45电磁型欠压脱扣器的基础上,分析存在的问题,提出基于电容降压、电容充放电的新方案。实验表明:该欠压脱扣器方案整体电路简洁,在78mm×30mm×35mm的空间里实现瞬时或延时欠压脱扣;动作点准确度达±2V,测控电路工作电流仅为0.73mA@5V。为新一代智能型低压万能式DW450断路器提供一种高可靠的小型化欠压脱扣器优选方案。

DW450断路器;欠压脱扣器;电路设计;SoC系统;瞬时脱扣;延时脱扣

0 引 言

DW450断路器作为新一代智能型低压万能式断路器,具有智能化、可通信、体积小、短路分断能力高和保护功能完善等特点[1-2],逐步成为智能电网中的主要配电单元。新一代断路器整体体积缩小,对内嵌电子单元提出了更高要求。如何在DW45电磁型欠压脱扣器的基础上,分析原有存在的问题,提出更优的设计方案,研制适用DW450系列断路器的高性能欠压脱扣器,是目前急需解决的问题。

欠压脱扣器作为断路器中内嵌的重要元件,对欠压脱扣-断路器分闸起着关键作用。设有欠压脱扣器的断路器,按照国标[3]规定,当电网电压下降到一定程度时,断路器分闸切断电源,既保护了重要设备的正常运行,又保护了本级电网下的用电设备。欠压脱扣器通常由测控电路与脱扣执行部件组成。执行部件可分为电磁型[4]和永磁型[5]两类。执行部件故障率较低,故欠压脱扣器品质,主要由测控电路决定。欠压脱扣器同时必须满足断路器电磁兼容性的全部规定[6]。

电磁型欠压脱扣器采用电磁铁为执行部件,控制电路首先向电磁铁发出一个较大的始动脉冲功率,然后保持电磁铁处于一定功率状态,以克服复位弹簧力并保持动铁芯处在吸合位置,为断路器主触头系合闸提供条件。当电压下降到一定值时,测控电路使电磁铁断电,动铁芯受复位弹簧反作用力弹出,顶开锁扣机构(脱扣),主触头系依靠自身储能弹簧力,断开主触头系。因电磁型部件在断电后具有复位自脱扣能力,在目前断路器中仍得到广泛应用。

现有DW45电磁型欠压脱扣器体积较大,普遍采用交流线路输入电压,经过整流、滤波,获得直流工作电压后,使用脉冲宽带调制(pulse width modulation,PWM)法[7-8],降低线圈端电压至一合适的平均工作电压(约30V)。因其PWM占空比过小(约为5%),使得PWM主控元件(MOS管)截止期间受过压、脉冲群的干扰机率达95%,严重影响MOS管的安全性。在现有欠压脱扣器方案故障原因总和中,MOS管损坏约占主要原因的90%。

1 DW450欠压脱扣方案研究

如将一电容器串联在交流输入回路中,在电磁铁得电之前,通过该电容器对主回路中的滤波电容充电。电磁铁得电之后,该电容器成为降压电容,为电磁铁提供一合适电压,则主控电路中无“活动”元件,可靠性将大幅度提高。在此基础上,电路整体简洁、电磁铁吸合可靠,在脱扣时,脱扣力满足要求且脱扣电压值准确。基于这一思路设计的欠压脱扣器方案如图1所示。

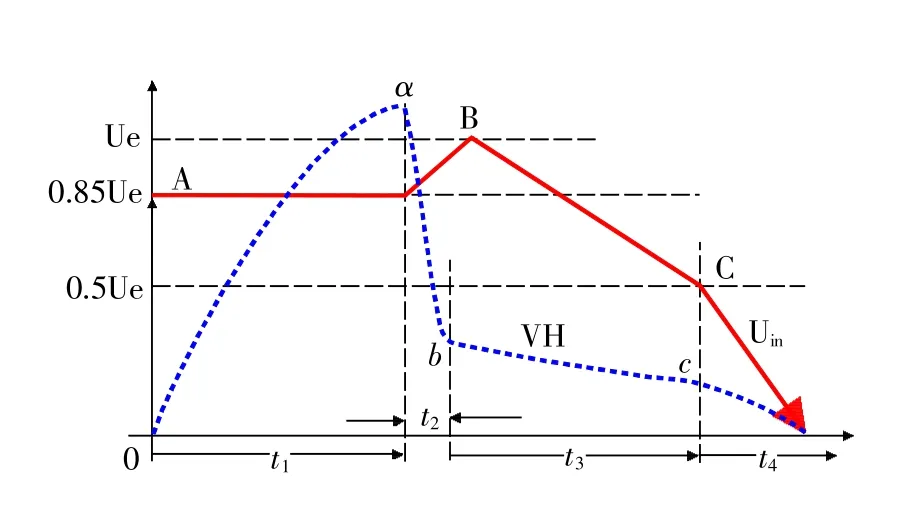

线路输入电压(220V/380V)从L、N输入,经EMC电路抗干扰抑制,形成“二次电源”L1、N1。设输入电压为0.85Ue,经过电容器C1由全桥B1整流后向电容器C2充电,经过t1时间后,VH电压被充电到a点控制开关电路接通电磁铁,C2上的电荷经电磁铁释放,电磁铁被强力启动,VH电压下降到b点。输入电压增加,则电磁铁端电压增加。输入电压逐步下降到0.5Ue时,VH电压下降到c点,SoC控制开关电路断开电磁铁。基于电容降压的欠压脱扣器电压运行状态如图2所示。

图1 DW450欠压脱扣器方案

图2 脱扣器电压运行状态图

方案中,电阻R3、R4对VH分压后的电压信号SB送入SoC,用于检测C2的充电电压值,Z2作限幅保护。L1经过二极管D0半波整流向电源电路供电,同时由电阻R1、R2组成电网的半波取样电路,取样信号SA送SoC,Z1限幅SA信号。电源电路产生12V电压供开关电路,生产的5V电压供SoC电路。

因采用SoC作为主控芯片,大为简化电路整体设计。在正常电压区间,电磁铁处于被接通状态,开关电路(MOS管)始终处于“静态”导通状态,对脉冲群等干扰呈现极低阻抗,承受干扰电压的几率几乎为零,可靠性得到大幅度提高。

2 主要单元电路设计

2.1 电磁铁参数

DW450欠压脱扣器的电磁铁,其主要参数设计为:线圈采用φ0.11mm漆包线绕制5600匝,直流电阻410Ω,电感量700mH;始动电压(US)120V;工作电压(UW)30V;维持电压(UM)9.5V;脱扣力大于22N。

2.2 主电容与储能电容

图1中的C1串联在交流回路,B1整流后向C2充电,在开关电路接通之前,C2上的充电电压为输入电压的开关电路接通之后,C2起到滤波作用。

将电磁铁等效为一电阻R与一电感L串联。设线路输入电压为Uin,忽略全桥B1压降及内阻,电磁铁工作电压UW为电磁铁获得一合适工作电压,C1容量为

C2上的VH电压,除了满足始动电压之外,C2所提供的功率还必须满足电磁铁完全吸合之需要,即向电磁铁提供足够的“始动功率”。或C2对电磁铁的放电时间,必须大于电磁铁的触动时间与运动时间之和[9]。设C2被充电到a点时的电压值为U0,电磁铁始动功率为P,则C2为

已知电磁铁触动时间与运动时间之和为t,且认为U0放电到UW(b点)时,电磁铁完成吸合,由式(2)可求得C2的具体数值。式(2)中的t,其含义如图2中的t2所示。

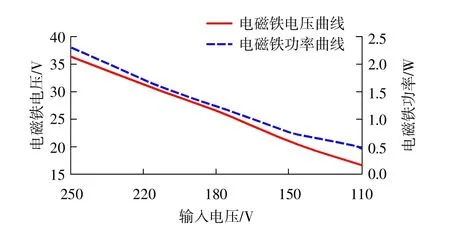

以220V电压等级为例,由C1、B1、C2及电磁铁组成的主回路,其电磁铁端电压VH及电磁铁功率,随输入电压的变化特性如图3所示。

图3 电磁铁电压及功率曲线

由图3可知,输入为额定电压时,电磁铁端电压及功率分别为31.4V、1.7W;输入降为110V时,电磁铁端电压及功率分别为16.6V、0.48W。完全满足电磁铁电气参数特性要求。

2.3 SoC电路设计

片上系统(system on chip,SoC)电路包括SoC和用于设定延时脱扣时限的3位拨码接口电路。

现今单片机或SoC,含有电源欠电压-复位、内置比较器、内置A/D转换器、可设定A/D转换器参考电压(VREF)、振荡器可被停止(STOP模式)以及在STOP模式下可“定时激活”等先进功能[10],选用体积小、功能强的SoC,可显著简化电路,缩小线路板面积。结合图1特点,选用廉价型ATtiny13为主的SoC电路,如图4所示。

图4 SoC电路

PB2、PB3和PB4设置为ADC模式,分别采样SA、 SB和T信号。PB0作输出控制信号,PB5为复位脚。3位拨码开关SW及周边电阻组成时间值给定电路,拨码开关全部断开时,PB4电压为VCC电压,脱扣器执行瞬时脱扣动作。其余7种组合方式,ADC2转换出的二进制数,分别表示0.5~10.5s不同的延时脱扣时间值。

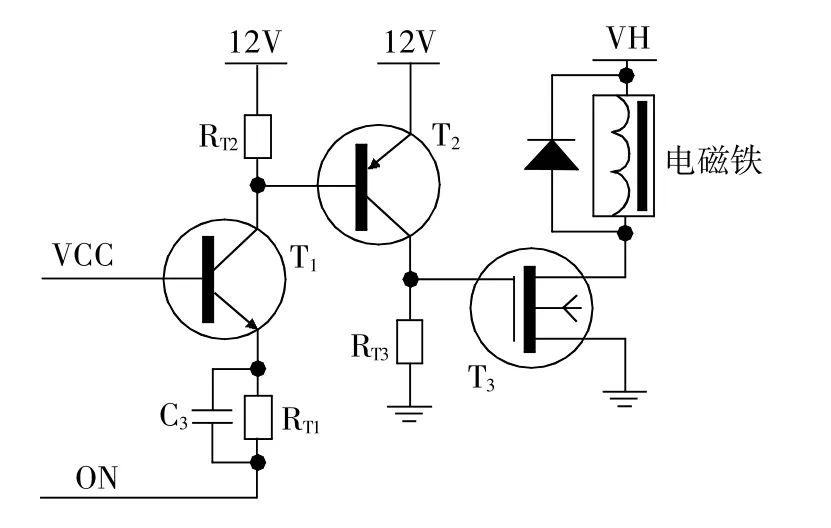

2.4 开关电路设计

开关电路用来接通电磁铁。图5所示的电路简单,且可低电平驱动。当来自SoC的控制信号ON信号为低电平时,T1基极被偏置,T2导通,T3获得栅极电压导通,电磁铁得电吸合。当ON高电平时,T1截止,T2无基极电流而截止,T3栅极被RT3下拉为低电平截止,电磁铁断电释放脱扣。

图5 开关电路

3 软件设计

充分发挥SoC的性能,可进一步增强欠压脱扣器的功能,如自动识别50Hz或60Hz线路输入电压频率等。

3.1 电网周期捕捉

SoC上电之后,令片内比较器+输入端与内部基准源(CVREF)连接,连接于采样信号的PB1(AIN1)与CVREF比较,即ACIS1:ACIS0=11模式,比较器输出中断,控制定时器(T/C0)启动与停止,获得线路输入电压半周期的时间值。时间值t0、t1、…、t9十个数值进入队列,对队列中的数组“去大”、“去小”求累加和,右移2次,求得电网周期T。

将电网周期T除以32,得到每周期采样时间间隔值tS,tS由T/C0完成定时,即在一个电网周期内采样32次。

3.2 有效值计算与及判据

为避免开方运算,缩短程序运行时间,将有效值算法定义改写为下式:

PB2(ADC1)对线路输入电压信号SA按时间周期tS采样,共计采样32次后,按式(3)进行有效值计算一次。

电磁铁吸合之前,在每次有效值计算完成后,对C2充电的SB信号采样,由PB3(ADC3)直接采样后保存为VSB。

3.3 主控流程图设计

吸合值UA、欠压脱扣值UR各自平方除以2和C2充电目标值UE作为常数存放。SoC上电初始化后,先行读取3位拨码开关设定的时间值,进入“空闲模式”。

定时器定时tS时间到了,激活CPU的同时,启动A/D采样SA信号,并判断是否完成了一个周期的采样。

当VSA>UA时,进一步判断VSB是否大于UE,若大于时,SoC输出ON信号为低电平,控制开关电路接通电磁铁。接着判断VSA是否小于UR,小于时判断是瞬时脱扣还是延时脱扣。瞬时脱扣状态时,SoC输出ON信号转为高电平,控制开关电路断开电磁铁实现脱扣。否则,继续完成设定的延时时间后脱扣。主控流程图如图6所示。

表1 DW450与DW45欠压脱扣器参数对比

主控程序中,加入了“空闲模式”,使得CPU消耗电流明显降低,既减轻了电源电路的功耗,又进一步提高了测控电路的可靠性。

4 结束语

本文研究的脱扣器,由主电路结构决定了C1、C2的工作性质,既为电磁铁提供了较大的始动功率,又自动地为电磁铁提供了合适的工作电压。电磁铁获得的始动功率大,吸合可靠,且电磁铁静、动铁芯之间的撞击小,在狭小的塑壳空间里实现了电磁机构与控制电路一体化。“万次”疲劳试验表明,脱扣器塑壳部分的形变可忽略不计,基本参数对比见表1。脱扣器整体电路简洁,瞬时或延时欠压脱扣功能全面。测控电路工作电流仅为0.73mA@5V。经受1.3倍电网电压老化,通过了4 kV脉冲群考核试验。为DW450断路器提供了一种高可靠小型化欠压脱扣器方案。

[1]陈培国.新一代DW450-1600智能型低压万能式断路器[J].低压电器,2005(1):8-14.

[2]何瑞华.我国低压电器现状与发展趋向[J].电气时代,2012(1):37-42.

[3]GB 14048.1—2006/IEC 60947-1:2001低压开关设备和控制设备第1部分:总则[S].北京:中国标准出版社,2006.

[4]王加法.欠电压分励一体化脱扣器的设计[J].江苏电器, 2008(11):23-24.

[5]吴志祥.基于ATtiny SoC的永磁型欠压脱扣器的设计[J].工矿自动化,2008(6):119-121.

[6]GB 14048.2—2008/IEC 60947-2:2006低压开关设备和控制设备第2部分:断路器[S].北京:中国标准出版社,2006.

[7]王永忠.断路器欠压脱扣器的优化设计[J].低压电器,2012(2):17-19.

[8]Durif G.Standard control device of a circuit breaker opening or closing electromagnet:USA,US6504698[P]. 2003-1-7.

[9]贺湘琰.电器学[M].北京:机械工业出版社,2007:29-90.

[10]马潮.AVR单片机嵌入式系统原理与应用实践[M].2版.北京:北京航空航天大学出版社,2012:40-120.

Research and design of undervoltage release used in DW450 circuit breaker based on SoC

WU Zhi-xiang1,GAO Bo1,JIANG Wen-xian2,HUANG Bo2

(1.Changzhou Institute of Technology,Changzhou 213002,China;2.Jaingsu Guoxing Electrical Co.,Ltd.,Changzhou 213177,China)

Considering that the new generation of intelligent DW450 low pressure universal type circuit breaker significantly reducesin size and hashigherrequirementsforthe embedded electronic units,a high-performance undervoltage release,based on SoC,has been worked out. On the basis ofthe problem analysisconcerning the existing DW45 type electromagnetic undervoltage release,the paper puts forward a new scheme based on the key technique of capacitance step-down and capacitor charging-discharging.Experimental results show that the whole circuit of the new undervoltage release is concise and capable of realizing the instantaneous undervoltage tripping or delay undervoltage tripping in 78 mm×30 mm×35 mm space.The accuracy of the action point is limited within plus or minus 2 V and the working current of measurement and control circuit is 0.73mA@5V only.In short,it provides an optimization scheme of a highly reliable and miniaturized undervoltage release for the new generation of intelligent DW450 low pressure universal type circuit breaker.

DW450 circuit breaker;undervoltage release;circuit design;SoC system;instantaneous trip;delay trip

TM561;TM76;TM930.12;TP273

:A

:1674-5124(2014)06-0064-04

10.11857/j.issn.1674-5124.2014.06.017

2014-04-21;

:2014-06-09

常州市知识产权计划项目(CK20122008)

吴志祥(1960-),男,江苏常州市人,副教授,研究方向为电力电子技术、智能电器。